текст лаб / lab_2

.docxЛабораторная работа № 2.

Исследование работы ПЦУ.

Цель работы: изучение принципов функционирования ПЦУ:

основная ячейка хранения – асинхронный RS-триггер;

синхронные триггеры D-триггер и JK-триггер;

регистры.

Краткие сведения об исследуемых устройствах.

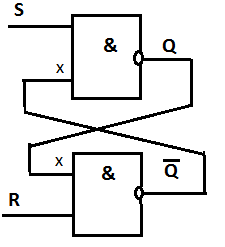

Последовательностные цифровые устройства ПЦУ всегда имеют в своей структуре обратные связи, так как их назначение в схемах – хранение информации. Основной ячейкой хранения всегда служит асинхронный RS-триггер. Он может быть реализован как на элементах И-НЕ, так и на элементах ИЛИ-НЕ. В настоящей лабораторной работе рассматривается триггер на И-НЕ.

Активный уровень воздействия на входы в такой структуре – «0». Если ни на один вход не поступает активный уровень, информация хранится за счет перекрестной обратной связи (входы x). Поступление активных уровне на оба входа нарушает действие обратной связи, устанавливая оба элемента в состояние «1». Это запрещенная комбинация. Но. Так как асинхронный RS-триггер входит в состав синхронных триггеров как основная ячейка хранения, то запрещенная комбинация становится практически невозможной.

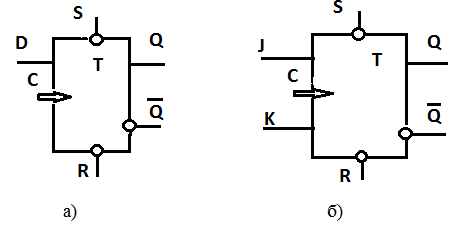

Основные типы синхронных триггеров: а) D-триггер и б) JK-триггер.

В настоящее время основное применение получил D-триггер.

На его основе строятся регистры.

Регистры могут служить для сдвига информации – последовательные,

Или для хранения информации – параллельные.

Постановка задачи.

На примере простейшей ячейки асинхронного RS-триггера и двух синхронных триггеров, D-триггера и JK-триггера, изучить назначение входов и принципы функционирования устройства. Для этого в пакете Quartus15 записать программы функционирования устройств на языке Verilog HDL, а затем построить временные диаграммы.

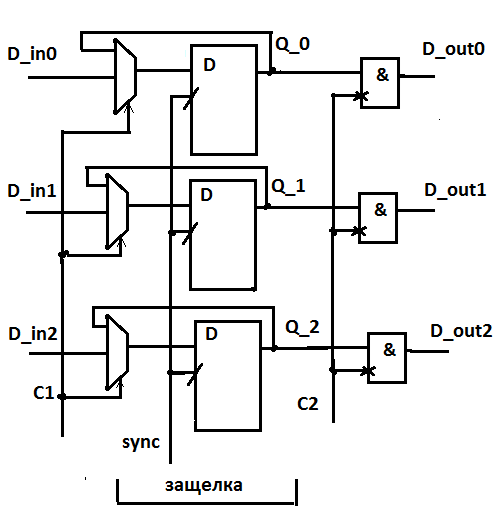

Изучить работу регистров сдвига на примере 8-разрядного регистра, а также двух разновидностей параллельных регистров: защелки, для краткосрочного хранения информации и двухбуферного – для длительного хранения информации. Параллельные регистры представлены на 4 разряда.

.

Задание на работу в лаборатории.

1. 1. Загрузить Quartus15, создать проект.

1. 2. Открыть Verilog HDL файл, записать программу 2.1, отражающую работу асинхронного RS- триггера.

1. 3. Сохранить файл, установить его старшим в иерархии и откомпилировать.

1. 4. Открыть окно симулятора. Построить диаграммы работы Рекомендуемые интервалы времени:

s – 80 нс с начальным уровнем 1, r – 50нс с начальным уровнем 0.

Скопировать диаграммы в отчет.

1. 5. Открыть новый Verilog HDL файл, записать программу 2.2, отражающую работу D – триггера.

1. 6. Сохранить файл под именем модуля, установить его старшим в иерархии и откомпилировать.

1. 7. Открыть окно симулятора. Построить диаграммы работы. Рекомендуемые интервалы времени:

для сигналов синхронизации – 20нс, информационного D-входа – 90нс с начальным уровнем 1, для s – входа при базовом уровне 1 короткий 0 от 110 до 130 нс, для r – входа при базовом уровне 1 короткий 0 от 270 до 290 нс.

Скопировать диаграммы в отчет.

1. 8. Открыть новый Verilog HDL файл, записать программу 2.3, отражающую работу JK – триггера.

1. 9. Дать файлу имя и сохранить его, установить старшим в иерархии и откомпилировать.

1. 10. Открыть окно симулятора. Построить диаграммы работы . Рекомендуемые интервалы времени:

для сигналов синхронизации – 20нс, информационных JK-входов J– 110нс с начальным уровнем 1 и K - 70 нс с начальным уровнем 0, , для s – входа при базовом уровне 1 короткий 0 от 150 до 170 нс, для r – входа при базовом уровне 1 короткий 0 от 30 до 50 нс.

Скопировать диаграммы в отчет.

Открыть Verilog HDL файл и записать программу 2.4, отражающую функционирование последовательного регистра на 8 разрядов. Сохранить файл, установить его старшим в иерархии и откомпилировать.

Пользуясь «Приложением 2», получить диаграммы при интервалах синхроимпульса – 20нс, данные – уровень «1» на интервалах от 10нс до 50 нс и от 130нс до 200нс.

Открыть новый Verilog HDL файл и записать программу 2.5, отражающую функционирование регистра-защелки на 4 разряда. Сохранить файл под именем модуля, установить его старшим в иерархии и откомпилировать.

Получить временные диаграммы для регистра-защелки, задав следующие параметры: синхронизация – 20нс; данные – d_in[0], d_in[2] – 35нс, d_in[1],d_in[3] – 50нс

Открыть новый Verilog HDL файл и записать программу 2.6, отражающую функционирование параллельного буферного регистра на 4 разряда. Сохранить файл под именем модуля, установить его старшим в иерархии и откомпилировать.

. Получить диаграмму работы устройства при следующих параметрах: синхронизация – 20нс; данные - d_in[0], d_in[2] – 35нс, d_in[1],d_in[3] – 50нс; ena – 170нс; rd – 200нс.

При получении временных диаграмм для каждого типа устройства результаты демонстрировать преподавателю.

Отчет должен содержать названия исследуемых устройств и программы работы устройств, подкрепленные проверкой на временной диаграмме.

Программа 2.1

module tr_rs

(input wire s,r,

output wire q,nq);

wire p,np;

assign p = !(s & np);

assign np = !(r & p);

assign q=p;

assign nq=np;

endmodule

Программа 2.2

module tr_d

(input wire clk,d,set,res,

output wire q);

reg p;

assign q=p;

always@ (negedge set, negedge res, posedge clk)

begin

if (!set)

p<=1'b1;

else if (!res)

p<=1'b0;

else if(clk)

p<=d;

end

endmodule

Программа 2.3

module tr_jk

(input wire clk, set, res, j, k,

output wire q);

reg p;

assign q=p;

always@ (negedge set, negedge res, posedge clk)

begin

if (!set)

p<=1'b1;

else if (!res)

p<=1'b0;

else if (clk)

case ({j,k})

2'b00: begin p<=p; end

2'b01: begin p<=1'b0; end

2'b10: begin p<=1'b1; end

2'b11: begin p<=!p; end

endcase

end

endmodule

Программа 2.4

module shift_rgstr

#(parameter N=8)

( input clk,

input d_in,

output d_out);

reg [N-1:0] d;

assign d_out = d[N-1];

always @ (posedge clk)

begin

d[N-1:1] <= d[N-2:0];

d[0] <= d_in;

end

endmodule

Программа 2.5

module latch_rgstr

#(parameter N=4)

(input [N-1:0] d_in,

input clk,

output [N-1:0]d_out);

reg [N-1:0]q;

assign d_out=q;

always@ (posedge clk)

begin

q<=d_in;

end

endmodule

Программа 2.6

module buf_rgstr

#(parameter N=4)

(input [N-1:0] d_in,

input clk, ena, res, rd,

output [N-1:0] d_out);

reg [N-1:0]w;

assign d_out=(rd)? (w) : (0);

always@ (posedge clk, negedge res)

begin

if (!res)

w<=0;

else if (clk)

begin

if (ena)

w<=d_in;

else

w<=w;

end

end

endmodule