Разработка

безопасного

программного

обеспечения

Раздел 1. Среды разработки и выполнения программ

Тема 1. Архитектура вычислительных систем

2/44

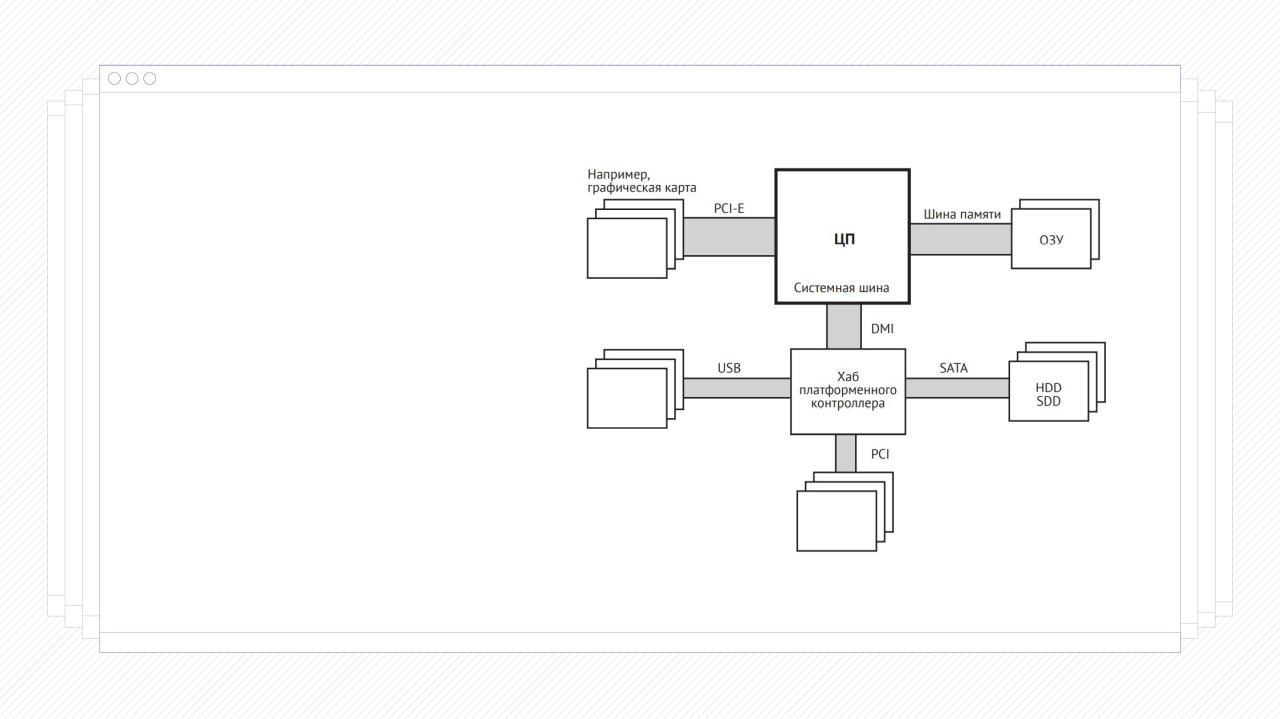

Основные

компоненты

архитектуры

компьютера

•Процессор (ЦП, центральный процессор)

•Системная шина (Front Side Bus – FSB)

•Северный мост

•Шина памяти

•Оперативная память

•Direct Media Interface - DMI

•Южный мост

•Внешние запоминающие устройства

Москва, осень 2021 г. |

Разработка безопасного программного обеспечения | Кафедра «Информационная безопасность» | © Московский технический университет связи и информатики |

3/44

Современная

архитектура

компьютера

• |

Процессор (ЦП, |

|

|

центральный процессор) с |

|

|

северным мостом |

|

• |

Системная шина (Front |

|

|

Side Bus – FSB) |

|

• |

Шина памяти |

|

• |

Оперативная память |

|

• |

Direct Media Interface - DMI |

|

• |

Хаб платформенного |

|

|

контроллера (южный |

|

|

мост) |

|

• |

Внешние запоминающие |

|

|

устройства |

Разработка безопасного программного обеспечения | Кафедра «Информационная безопасность» | © Московский технический университет связи и информатики |

Москва, осень 2021 г. |

||

4/44

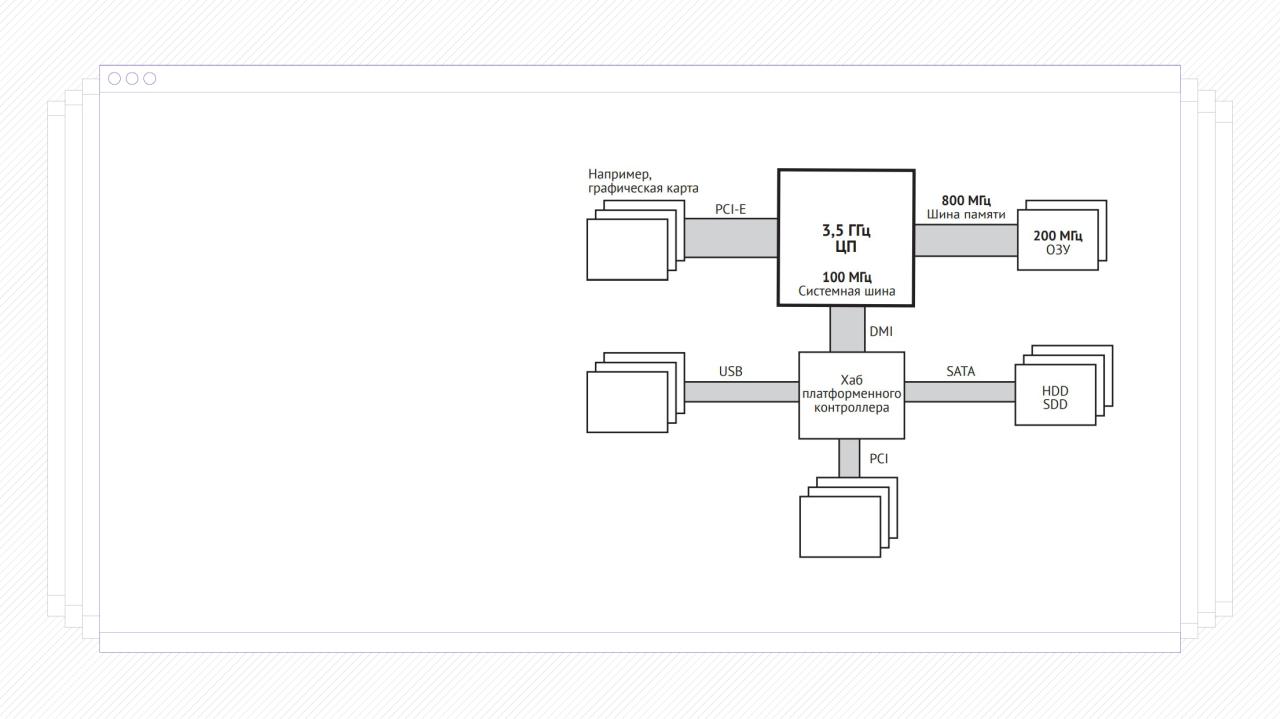

Современная

аппаратная архитектура с типовым тактовым сигналом

Москва, осень 2021 г. |

Разработка безопасного программного обеспечения | Кафедра «Информационная безопасность» | © Московский технический университет связи и информатики |

5/44

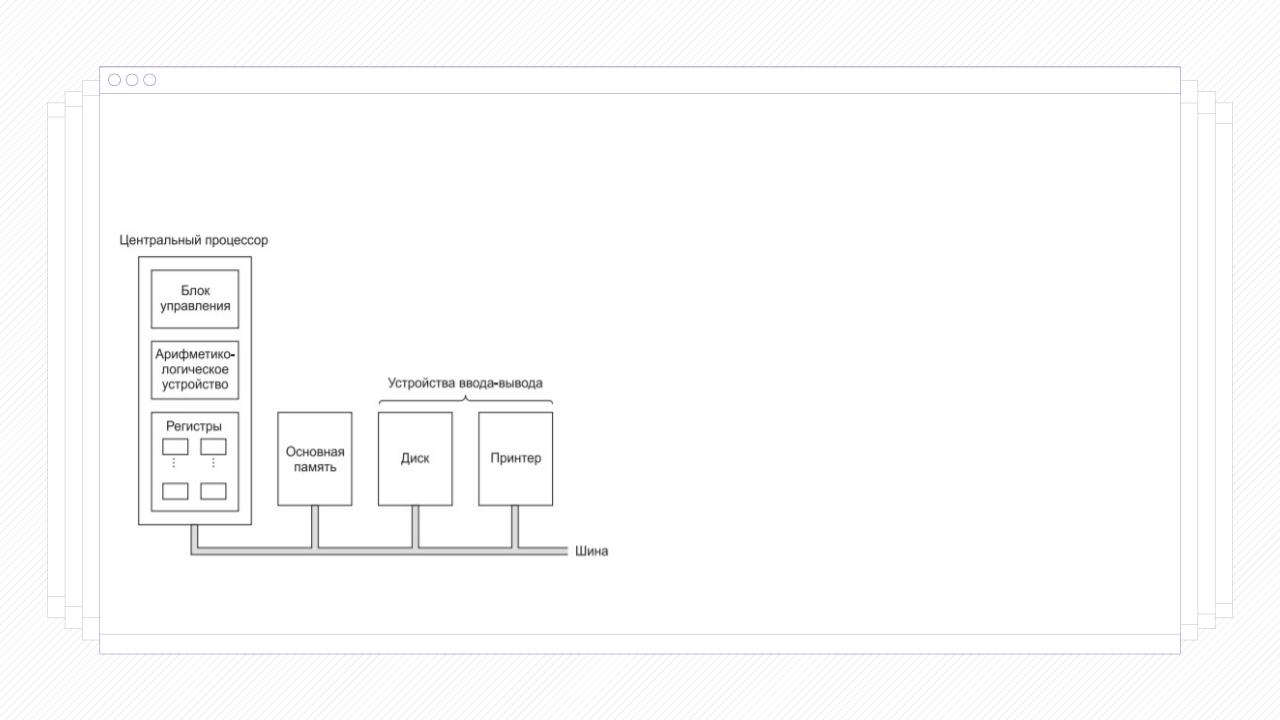

Процессор |

Определения |

|

Процессор – центральный |

|

вычислительный элемент любого |

|

компьютера, предназначенный для |

|

обработки чего-либо. |

|

Память – компонент компьютера, в |

|

котором хранятся программы и |

|

данные. |

|

Устройства ввода-вывода – служат |

|

соответственно для ввода |

|

информации в машину и вывода из |

|

нее, а также для обеспечения |

|

общения пользователя с ЭВМ. |

|

Шина – это несколько проводников, |

|

соединяющих несколько устройств. |

Москва, осень 2021 г. |

Разработка безопасного программного обеспечения | Кафедра «Информационная безопасность» | © Московский технический университет связи и информатики |

6/44

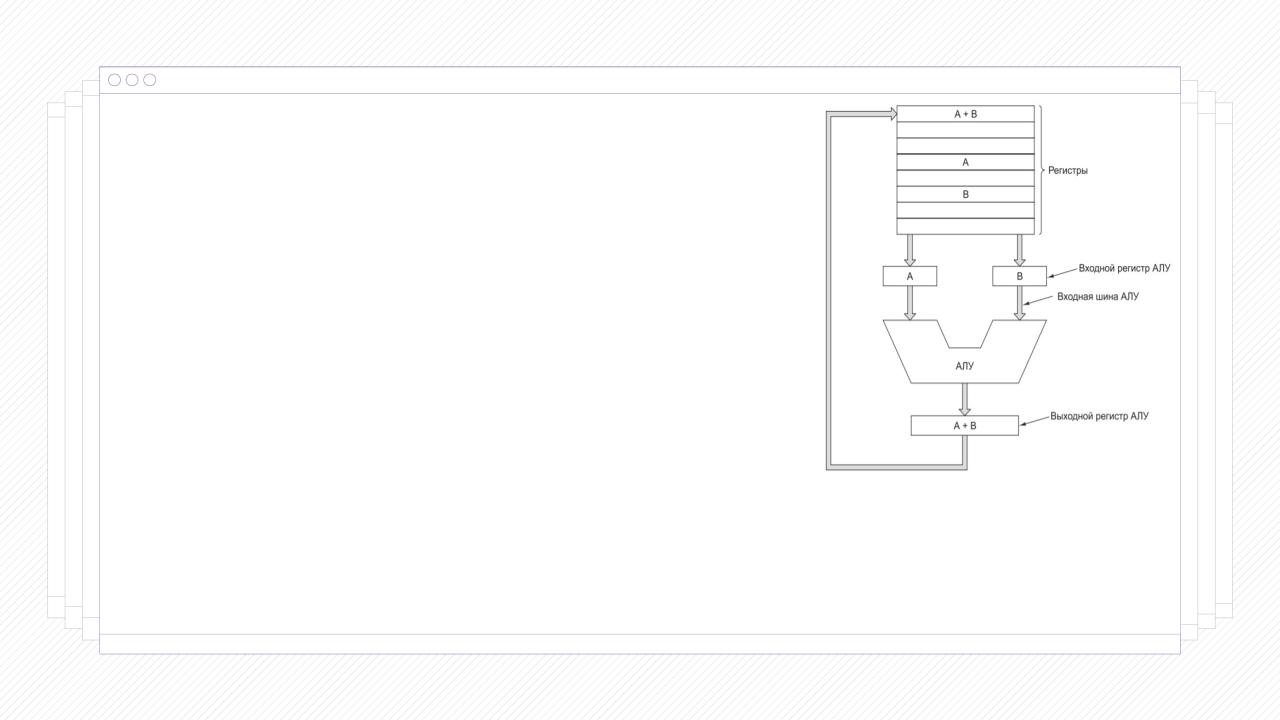

АЛУ (Арифметико-логическое устройство) -

реализует важную часть процесса обработки данных. Она заключается в выполнении |

|

набора простых операций. |

Операции АЛУ подразделяются на три основные |

|

|

|

категории: |

|

Арифметической операцией называют процедуру |

|

обработки данных, аргументы и результат которой |

|

являются числами (сложение, вычитание, умножение, |

|

деление). |

|

Логической операцией именуют процедуру, |

|

осуществляющую построение сложного высказывания |

|

(операции И, ИЛИ, НЕ). |

|

Операции над битами обычно подразумевают сдвиги в |

|

битах. |

Москва, осень 2021 г. |

Разработка безопасного программного обеспечения | Кафедра «Информационная безопасность» | © Московский технический университет связи и информатики |

7/44

Регистры

Последовательные или параллельные логические устройства, используемые для хранения n-разрядных двоичных чисел и выполнения преобразований над ними.

Элементарной ячейкой электронной памяти является триггер, способный сохранять 1 бит записанной в нем информации.

Классифицируются по следующим видам:

1.Регистры хранения

2.Регистры сдвига

Москва, осень 2021 г. |

Разработка безопасного программного обеспечения | Кафедра «Информационная безопасность» | © Московский технический университет связи и информатики |

8/44

Тракт данных

Большинство команд можно разделить на две группы: команды типа регистр-память и типа регистр- регистр.

Цикл тракта данных. |

|

||

Центральный процессор выполняет каждую команду |

|

||

за несколько шагов: |

|

|

|

1. Вызывает следующую команду из памяти и переносит ее |

|

||

в регистр команд; |

|

|

|

2. |

Меняет положение счетчика команд, который теперь |

|

|

должен указывать на следующую команду; |

|

||

3. |

Определяет тип вызванной команды; |

|

|

4. |

Если команда использует слово из памяти, определяет, |

Такая последовательность |

|

где находится это слово; |

шагов (выборка — |

||

5. |

Переносит слово, если это необходимо, в регистр |

декодирование — |

|

центрального процессора; |

исполнение) является основой |

||

6. |

Выполняет команду; |

|

работы всех компьютеров. |

7. |

Переходит к шагу 1, чтобы начать выполнение |

|

|

следующей команды |

Разработка безопасного программного обеспечения | Кафедра «Информационная безопасность» | © Московский технический университет связи и информатики |

||

Мо ква, осень 2021 г. |

|||

9/44

Hyper-Threading

Технология Intel® Hyper-Threading (Intel® HT) обеспечивает более эффективное использование ресурсов процессора, позволяя выполнять несколько потоков на каждом ядре.

Москва, осень 2021 г. |

Разработка безопасного программного обеспечения | Кафедра «Информационная безопасность» | © Московский технический университет связи и информатики |

Многоядерный процессор - |

10/ |

|

44 |

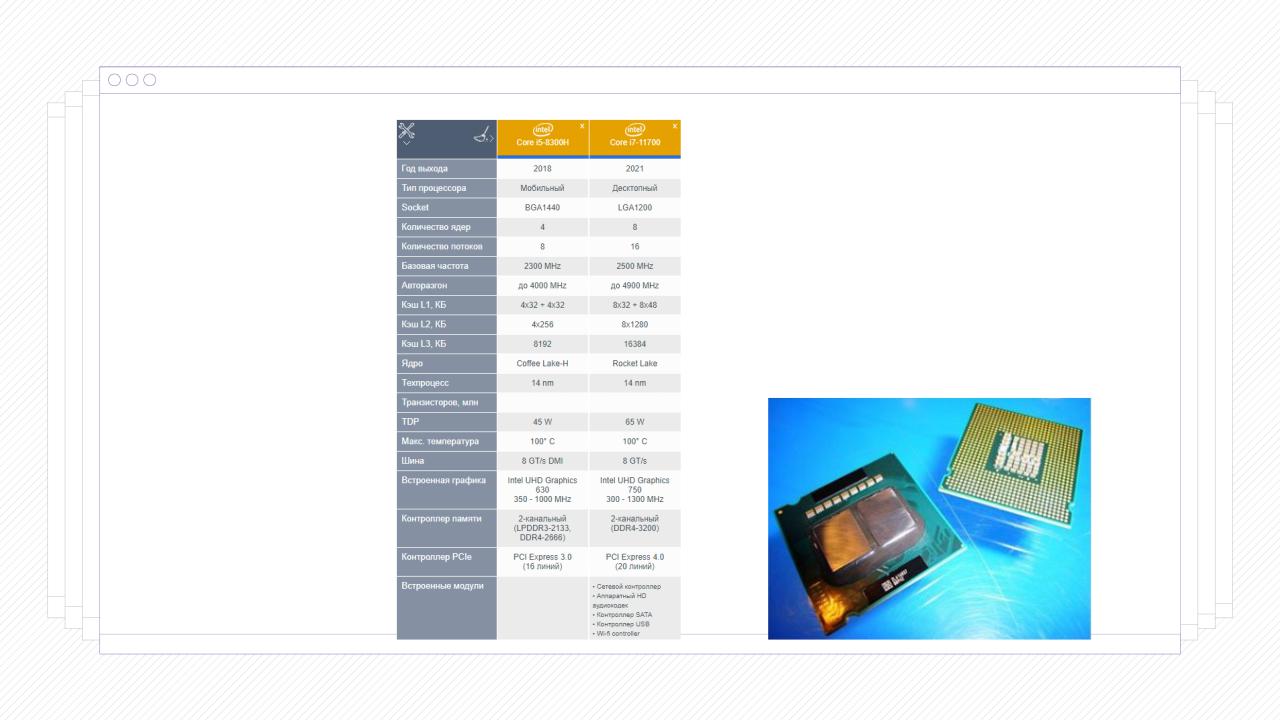

Сравнение

двух

многоядерных

процессоров

•Центральный процессор, содержащий два и более вычислительных ядра на одном процессорном кристалле или в одном корпусе.

•Ядро процессора – это система исполнительных устройств (набор АЛУ), предназначенных для обработки данных

Москва, осень 2021 г. |

Разработка безопасного программного обеспечения | Кафедра «Информационная безопасность» | © Московский технический университет связи и информатики |

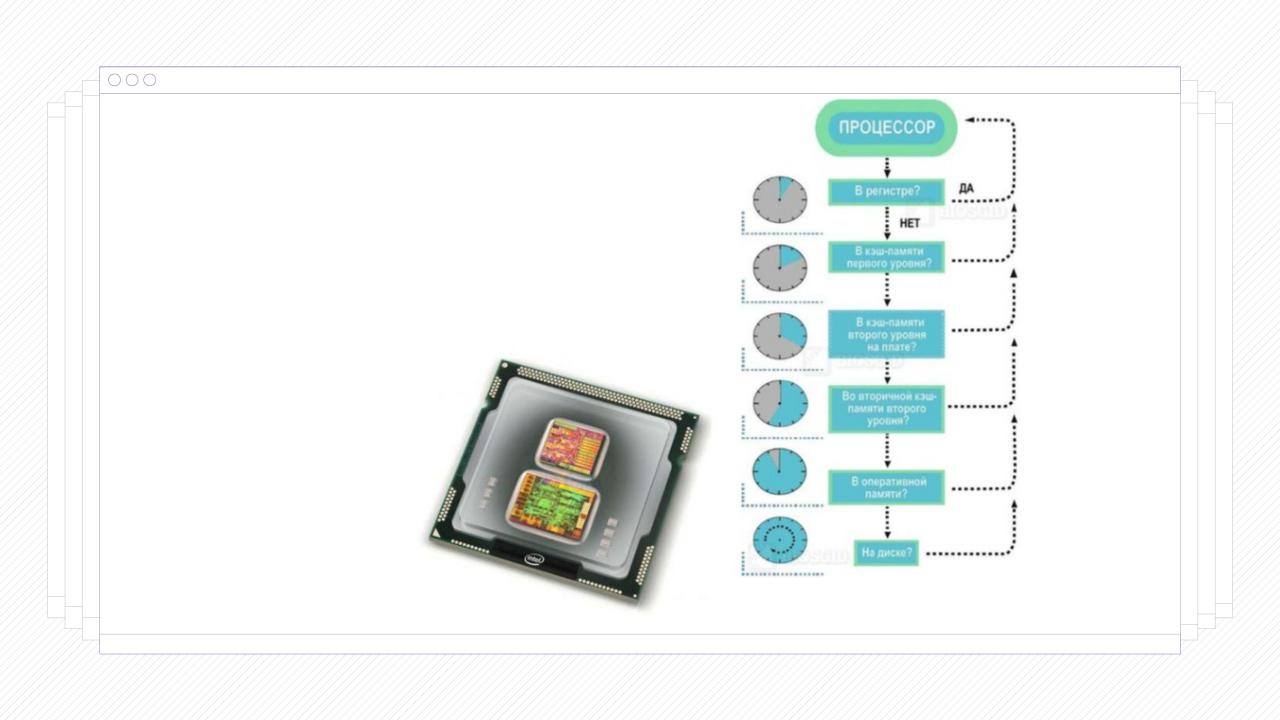

Кэш

Кэш-память – это высокоскоростная память произвольного доступа, используемая процессором компьютера для временного хранения информации. Она увеличивает производительность, поскольку хранит наиболее часто используемые данные и команды «ближе» к процессору, откуда их можно быстрее получить.

11/

44

Порядок

поиска

процессором информации в памяти

Москва, осень 2021 г. |

Разработка безопасного программного обеспечения | Кафедра «Информационная безопасность» | © Московский технический университет связи и информатики |

12/

44

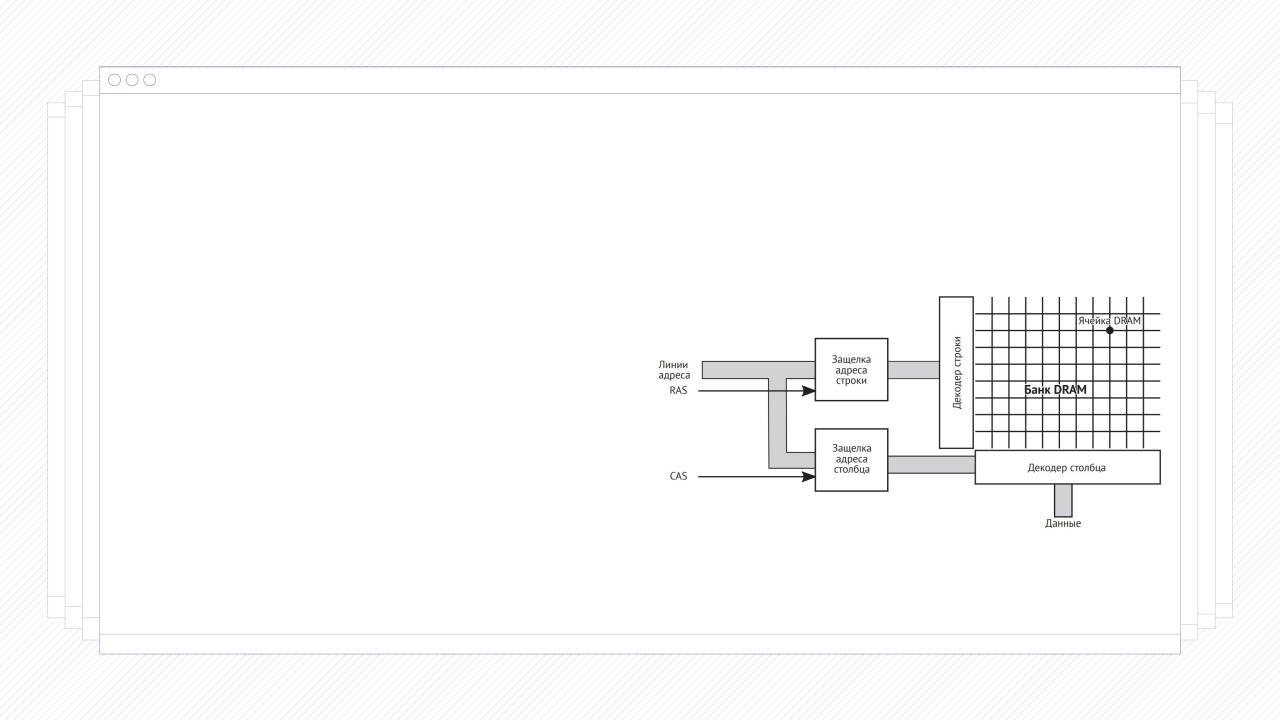

Пример микросхемы DRAM

•Ячейка DRAM, содержащая один бит данных, состоит из транзистора и конденсатора

•Ячейки группируются в банки DRAM

•Модули DRAM состоят из большого числа банков DRAM, организованных так, чтобы можно было обращаться к нескольким битам (составляющим одно слово) в одном такте

Москва, осень 2021 г. |

Разработка безопасного программного обеспечения | Кафедра «Информационная безопасность» | © Московский технический университет связи и информатики |

13/

44

Процессорный

кеш

•прозрачен с точки зрения архитектуры набора команд

•используются микросхемы SRAM

Москва, осень 2021 г. |

Разработка безопасного программного обеспечения | Кафедра «Информационная безопасность» | © Московский технический университет связи и информатики |