latypov_x51_p1

.pdfКАЗАНСКИЙ (ПРИВОЛЖСКИЙ)

ФЕДЕРАЛЬНЫЙ УНИВЕРСИТЕТ

ИИСТИТУТ ФИЗИКИ

КАФЕДРА РАДИОФИЗИКИ

Латыпов Р.Р.

Учебно-методическое пособие

Микроконтроллеры х51 архитектуры.

Начальное освоение

Казань 2012 г.

Печатается по решению Редакционно-издательского совета Института физики Казанского (Приволжского) Федерального Университета

Латыпов Р.Р. Методическое пособие «Микроконтроллеры х51 архитектуры. Начальное освоение». Казань, 2012. 34 с.

В настоящее пособие включены описание лабораторного макета и задания,

выполняемые в лаборатории, по курсам, связанным с изучением 8 битных микроконтроллеров. Целью работ является получение начальных практических навыков и умения работы с современными 8-разрядными микроконтроллерами, которые обсуждаются в лекционном курсе. В

описании приводятся сведения, необходимые для выполнения практических заданий. Лабораторный макет представляет собой плату начального освоения, серийно выпускаемую производителем микроконтроллера.

Пособие рекомендуется студентам института физики К(П)ФУ, обучающимся на специальностях «Радиотелекоммуникации», «Компьютерная электроника» и «Информационная безопасность».

Рецензент: доцент каф. радиоэлектроники, к. ф.-м. н. Насыров И.А.

Оглавление |

|

|

1. |

Введение ..................................................................................................................................... |

4 |

2. |

Микропроцессорное ядро CIP-51............................................................................................. |

6 |

|

2.1. Арифметико-логическое устройство ................................................................................ |

7 |

|

2.2. Устройство управления (CONTROL LOGIC).................................................................. |

7 |

|

2.3. Память данных.................................................................................................................... |

7 |

|

2.4. Блок регистров специальных функций ............................................................................ |

8 |

3. |

Система команд х51 совместимых микроконтроллеров ..................................................... |

10 |

|

3.1. Виды адресации ................................................................................................................ |

13 |

|

3.2. Арифметические операции.............................................................................................. |

14 |

|

3.3. Логические операции ....................................................................................................... |

14 |

|

3.4. Операции пересылки данных .......................................................................................... |

14 |

|

3.5. Битовые операции............................................................................................................. |

15 |

|

3.6. Операции ветвления ......................................................................................................... |

15 |

4. |

Микроконтроллер C8051F411 ................................................................................................ |

17 |

|

4.1. Обработка прерываний .................................................................................................... |

17 |

|

4.2. Сторожевой таймер .......................................................................................................... |

19 |

|

4.3. Порты ввода-вывода......................................................................................................... |

21 |

5. |

Директивы компилятора ......................................................................................................... |

25 |

6. |

Лабораторная установка C8051F411EB ................................................................................ |

26 |

|

6.1. Введение в IDE SILABS................................................................................................... |

27 |

|

6.1.1. Макроассемблер A51 фирмы Keil............................................................................ |

27 |

|

6.1.2. Оптимизирующий кросс-компилятор C51 фирмы Keil......................................... |

27 |

|

6.1.3. Компоновщик L51 ..................................................................................................... |

28 |

|

6.1.4. Отладчик..................................................................................................................... |

28 |

|

6.2. Запуск IDE Silabs и создание файла проекта ................................................................. |

28 |

|

6.3. Быстрый старт................................................................................................................... |

29 |

|

6.4. Запуск IDE Silabs и открытие файла готового проекта ............................................... |

30 |

|

6.5. Добавление файла с исходным текстом и его редактирование .................................. |

31 |

7. |

Задачи ....................................................................................................................................... |

32 |

|

7.1. Раздел 1.............................................................................................................................. |

32 |

|

7.2. Раздел 2.............................................................................................................................. |

33 |

8. |

Литература ............................................................................................................................... |

34 |

3

1. Введение

Микроконтроллерная техника является одной из наиболее динамично развивающихся областей современной вычислительной техники. Без микроконтроллеров сегодня немыслим ни один современный прибор. Микроконтроллеры широко используются в различных изделиях вычислительной, измерительной, лабораторной и научной техники; в системах управления промышленным оборудованием, транспорта и связи; в бытовой технике и других областях.

Сегодня в мире производится несколько десятков тысяч типов различных микроконтроллеров. Среди них особое место занимают так называемые х51совместимые микроконтроллеры, т.е. микроконтроллеры, совместимые с одним из первых типов микроконтроллеров - i8051. Не смотря на почти тридцатилетнюю историю своего существования, эти микроконтроллеры и сегодня занимают лидирующее место и являются «de facto» всемирным промышленным стандартом. x51-совместимые микроконтроллеры выпускаются практически всеми известными мировыми производителями: Intel, Atmel, Maxim-Dallas, Goal Semicondactor, Hyundai, Philips, Infineon, Temic, Winbond, ICSI, ISSI, Oki Semicondactor, Sharp, STT, Cypress, Texas

Instruments, STM, TDK, SiLabs и многими другими.

Популярность х51 совместимых микроконтроллеров обусловлена рядом причин, среди которых главенствующую роль играют:

удачная и «прозрачная» архитектура;

хорошая документированность – обилие разнообразной научно-технической литературы: рекомендаций по применению, книг, статей;

большое количество качественного и доступного программного обеспечения: компиляторов различных языков программирования: ASM51, C++, PL/M51, Fort51 и других, а также целый ряд дизассемблеров, программных отладчиков, эмуляторов и т.п.;

большое количество программ и библиотек для различных научно-технических задач;

разработчиками накоплен колоссальный опыт работы с этими микроконтроллерами, изучены многие особенности их поведения, выработаны приемы и способы отладки, накоплен опыт программирования.

Сравнительно недавно, в 1999 году, в клуб производителей х51-совместимых микроконтроллеров вошла фирма SiLabs [1,5,7]. Специалисты фирмы SiLabs кардинально изменили ядро своих новых х51-совместимых микроконтроллеров, что позволило им более чем на порядок увеличить производительность. Полученное ядро CIP-51, построенное по конвейерному принципу, до 70% инструкций выполняет за один период тактовой частот, что обеспечивает повышение пиковой производительности в 12 раз по сравнению со стандартным ядром i8051. Дополнительно это микропроцессорное ядро было оснащено не менее мощными аналого-цифровыми и цифро-аналоговыми узлами, расширенной периферией, усовершенствованными средствами внутрисистемного программирования и отладки.

В состав периферии микроконтроллеров фирмы SiLabs входят:

встроенная Flash память программ-данных (объемом от 8 до 128К);

встроенная дополнительная оперативная память (объемом от 1 до 8К);

расширенный обработчик прерываний (22 вектора у большинства микроконтроллеров);

модифицированная система защиты кода;

аппаратный охранный таймер WDT;

монитор питания;

4

встроенная развитая система тактирования, позволяющая микроконтроллеру работать как от внешнего генератора, так и со встроенным тактовым генератором, оснащенным кварцевым резонатором, конденсатором или вообще без дополнительных элементов с возможностью изменения источника тактирования «на лету».

интерфейсы UART, SMBus (I2C), SPI, CAN, USB;

один или два аналого-цифровых преобразователя (с разрядностью 8, 10,12 или 16 бит);

2 (1) аналоговых компаратора;

источник опорного напряжения;

до двух 12-разрядных цифро-аналоговых преобразователей;

Программирование и отладка микроконтроллеров фирмы SiLabs реализованы на интерфейсах JTAG или C2. Это позволяет не только быстро программировать Flash память, но и производить отладку программ в реальном времени.

5

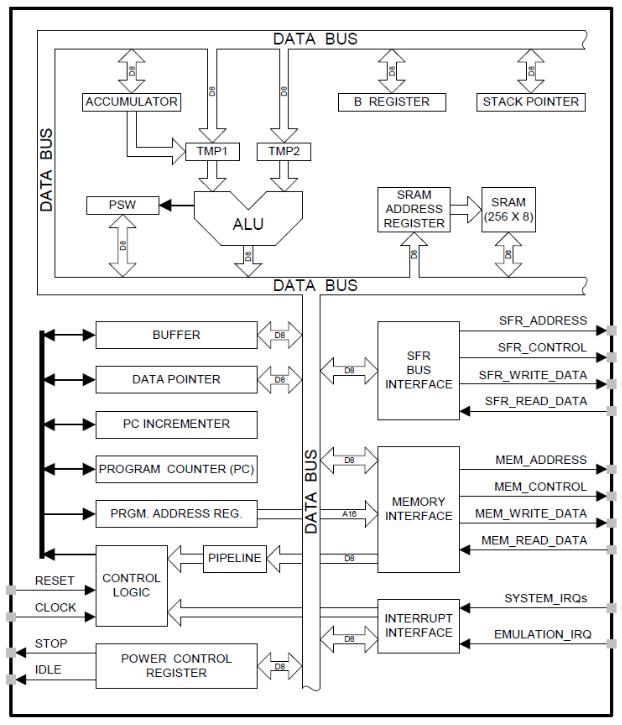

2. Микропроцессорное ядро CIP-51

Основу структурной схемы (рис. 1) микропроцессорного ядро CIP-51 образует внутренняя двунаправленная 8-битная шина (DATA BUS), которая связывает между собой основные узлы и устройства микроконтроллера: арифметико-логическое устройство (ALU), память данных (SRAM), блок регистров специальных функций, устройство управления (CONTROL LOGIC), а также все периферийные устройства микроконтроллера (некоторые из которых рассмотрены в разделе 4) [1].

Рис 1. Упрощенная блок-схема микропроцессорного ядра CIP-51

6

2.1. Арифметико-логическое устройство

Арифметико-логическое устройство (ALU) разрядностью 8-бит может выполнять арифметические операции сложения, вычитания, умножения и деления; логические операции И, ИЛИ, исключающее ИЛИ, а также операции циклического сдвига, сброса, инвертирования и т.п. К входам подключены программно-недоступные регистры TMP1 и TMP2, предназначенные для временного хранения операндов, схема десятичной коррекции и схема формирования признаков результата операции (PSW) [5,6,7,9].

Важной особенностью ALU является его способность оперировать не только байтами, но и битами. Отдельные программно-доступные биты могут быть установлены, сброшены, инвертированы, переданы, проверены и использованы в логических операциях. Эта способность достаточно важна, поскольку для управления объектами часто применяются алгоритмы, содержащие операции над входными и выходными булевыми переменными, реализация которых средствами обычных микропроцессоров сопряжена с определенными трудностями.

Для сохранения результатов вычисления и в качестве одного из операндов используется специальный регистр аккумулятор (А, ACCUMULATOR), так же в случае операций умножения и деления используется расширение аккумулятора – регистр В.

2.2. Устройство управления (CONTROL LOGIC)

Устройство управления (CU) на основе сигналов синхронизации (CLOCK) формирует машинный цикл, обеспечивает функционирование системы сброса (RESET), программного счетчика (PC), системы выбора команд и увеличения значения программного счетчика (PC INCREMENTER), управление питанием (POWER CONTROL REGISTER) и системой прерываний (INTERRUPT INTEFACE).

2.3. Память данных

Размер памяти данных(SRAM) составляет 256 байт, младшие 128 (по адресу) ячеек используются только как память данных, и обращение к ним может быть произведено любым способом адресации. Старшие 128 байт могут быть адресованы только косвенным образом, потому что делят адреса с регистрами специальных функций. На рис. 2 показана блочная структура памяти данных.

Адрес

0хFF |

|

Верхние 128 байт |

|

Регистры специальных |

|

|

|

|

|||

|

|

памяти RAM (только |

|

функций SFR (только |

|

0x80 |

|

косвенная адресация) |

|

прямая адресация) |

|

0x7F |

|

Память данных RAM |

|

|

|

|

|

|

|

|

|

0x30 |

|

байт адресуемая |

|

|

|

|

|

|

Нижние 128 байт |

||

0x2F |

|

|

|

||

|

Память данных RAM |

|

памяти RAM |

||

|

|

|

|||

0x20 |

|

бит адресуемая |

|

(прямая и косвенная |

|

|

|

|

адресация) |

||

0x1F |

|

Регистры общего |

|

||

|

|

|

|

||

|

|

|

|

|

|

0x00 |

|

назначения GPO |

|

|

|

|

|

|

|

|

|

|

Рис.2. Блочная структура памяти данных. |

||||

На рис. 3 более подробно изображены младшие 128 байт памяти. Это связано с тем, что организация этого блока памяти имеет ряд специально выделенных областей. Первая специальная область это – блок регистров общего назначения, состоящий из 4 банков и занимающий адреса с 0х00 до 0х1F. Банки адресов могут переключаться, т.е. в один момент времени активным может быть только один банк. В каждом банке присутствуют регистры от R0 до R7, к которым можно обращаться как по символическому имени, так и по прямому адресу. Вторая специальная область это – блок побитно адресуемых ячеек,

7

занимающий адреса с 0х20 до 0х2F. Внутри этого блока каждый бит имеет свой собственный адрес и обращение к нему можно производить отдельно от всего байта.

Адрес |

|

|

|

|

|

|

|

|

|

|

|

байта |

|

|

|

|

|

|

Адрес бита |

|

|

|

|

7F |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Память данных общего назначения RAM |

|

|||||||

|

|

|

|

|

|

|

байт адресуемая |

|

|

|

|

30 |

|

|

|

|

|

|

|

|

|

|

|

2F |

7F |

7E |

|

7D |

|

7C |

7B |

7A |

79 |

78 |

|

2E |

77 |

76 |

|

75 |

|

|

74 |

73 |

72 |

71 |

70 |

2D |

6F |

6E |

|

6D |

|

6C |

6B |

6A |

69 |

68 |

|

2C |

67 |

66 |

|

65 |

|

|

64 |

63 |

62 |

61 |

60 |

2B |

5F |

5E |

|

5D |

|

5C |

5B |

5A |

59 |

58 |

|

2A |

57 |

56 |

|

55 |

|

|

54 |

53 |

52 |

51 |

50 |

29 |

4F |

4E |

|

4D |

|

4C |

4B |

4A |

49 |

48 |

|

28 |

47 |

46 |

|

45 |

|

|

44 |

43 |

42 |

41 |

40 |

27 |

3F |

3E |

|

3D |

|

3C |

3B |

3A |

39 |

38 |

|

26 |

37 |

36 |

|

35 |

|

|

34 |

33 |

32 |

31 |

30 |

25 |

2F |

2E |

|

2D |

|

2C |

2B |

2A |

29 |

28 |

|

24 |

27 |

26 |

|

25 |

|

|

24 |

23 |

22 |

21 |

20 |

23 |

1F |

1E |

|

1D |

|

1C |

1B |

1A |

19 |

18 |

|

22 |

17 |

16 |

|

15 |

|

|

14 |

13 |

12 |

11 |

10 |

21 |

0F |

0E |

|

0D |

|

0C |

0B |

0A |

09 |

08 |

|

20 |

07 |

06 |

|

05 |

|

|

04 |

03 |

02 |

01 |

00 |

1F |

|

Банк 3 регистров общего назначения (R0-R7) |

|

||||||||

18 |

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

17 |

|

Банк 2 регистров общего назначения (R0-R7) |

|

||||||||

10 |

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

0F |

|

Банк 1 регистров общего назначения (R0-R7) |

|

||||||||

08 |

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

07 |

|

R7 |

|

|

|

|

|

|

|

|

|

06 |

|

R6 |

|

|

|

|

|

|

|

|

|

05 |

|

R5 |

|

|

|

|

|

|

|

|

|

04 |

|

R4 |

|

|

|

Банк 0 регистров общего назначения (по |

|||||

03 |

|

R3 |

|

|

|

|

|

умолчанию) |

|

|

|

02 |

|

R2 |

|

|

|

|

|

|

|

|

|

01 |

|

R1 |

|

|

|

|

|

|

|

|

|

00 |

|

R0 |

|

|

|

|

|

|

|

|

|

Рис. 3. Структура младших 128 байтов памяти данных

2.4. Блок регистров специальных функций

Блок регистров специальных функций (special function registers, SFRs) предоставляет доступ к периферийным узлам в х51-совместимых микроконтроллерах. Эти регистры (SFR) располагаются в прямо адресуемом адресном пространстве памяти данных - 0x80-0xFF. Для обеспечения совместимости между микроконтроллерами различных производителей некоторые SFR регистры располагаются во всех микроконтроллерах по одним и тем же адресам и имеют одинаковое функциональное назначение. Все вышесказанное в полной мере относится и к микроконтроллерам фирмы Silicon Laboratories, имеющим усовершенствованное ядро CIP-51. С помощью этих регистров осуществляется управление и обмен данными между ресурсами ядра CIP-51 и периферией.

Регистры с адресами, оканчивающимися на 0х0 или 0х8 (например, P0, TCON, P1, SCON, IE и т.д.) являются и бит-адресуемыми и байт-адресуемыми. Все остальные регистры SFR являются только байт-адресуемыми. Неиспользуемые адреса в адресном пространстве SFR зарезервированы. Использование этих адресов приводит к неопределенному результату и нежелательно. В таблице 1 приведены адреса стандартных регистров (SFR) для х51 архитектуры, а в таблице 2 – краткое описание каждого из них.

8

Таблица 1.

Стандартные регистры х51 МК

|

Название |

|

|

Адрес регистра |

|

Описание функционального назначения |

|

||||||||||||

|

регистра |

|

|

|

|

|

регистра |

|

|

|

|

|

|

|

|||||

|

ACC |

|

|

0xE0 |

|

|

Аккумулятор |

|

|

|

|

|

|

|

|||||

|

B |

|

|

0xF0 |

|

|

Регистр B |

|

|

|

|

|

|

|

|||||

|

DPH |

|

|

0x83 |

|

|

Старший байт указателя данных |

|

|

|

|||||||||

|

DPL |

|

|

0x82 |

|

|

Младший байт указателя данных |

|

|

|

|||||||||

|

P0 |

|

|

0x80 |

|

|

Выходной регистр Port 0 |

|

|

|

|

|

|||||||

|

PI |

|

|

0x90 |

|

|

Выходной регистр Port 1 |

|

|

|

|

|

|||||||

|

P2 |

|

|

0xA0 |

|

|

Выходной регистр Port 2 |

|

|

|

|

|

|||||||

|

P3 |

|

|

0xB0 |

|

|

Выходной регистр Port 3 |

|

|

|

|

|

|||||||

|

PSW |

|

|

0xD0 |

|

|

Слово состояния программы |

|

|

|

|||||||||

|

SP |

|

|

0x81 |

|

|

Указатель стека |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 2. |

|

|

|

|

|

|

Краткое описание стандартных регистров х51 МК |

|

|

|

||||||||||

Название |

|

|

|

|

|

|

|

|

|

|

Краткое описание |

|

|

|

|

|

|||

регистра |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ACC |

|

|

Регистр аккумулятора. Регистр используется при арифметических операциях. |

||||||||||||||||

B |

|

|

Регистр |

|

В. Дополнительный регистр, используемый как второй аккумулятор при |

||||||||||||||

|

|

|

арифметических операциях. |

|

|

|

|

|

|

|

|

|

|

|

|

||||

DPH |

|

|

Регистр старшего байта указателя данных. Старший байт 16-битного регистра указателя данных |

||||||||||||||||

|

|

|

DPTR, используемого для косвенной адресации оперативной памяти RAM и Flash памяти. |

||||||||||||||||

DPL |

|

|

Регистр младшего байта указателя данных. Младший байт 16-битного регистра указателя данных |

||||||||||||||||

|

|

|

DPTR, используемого для косвенной адресации оперативной памяти RAM и Flash памяти. |

||||||||||||||||

P0 |

|

|

Регистр двунаправленного порта 0. Биты 7-0: P0.[7-0] |

|

|

|

|

|

|||||||||||

|

|

|

При записи: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

0 - логический низкий уровень. |

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

1 - логический высокий уровень или высокоимпедансное состояние. |

|||||||||||||||

|

|

|

При чтении: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

0 - если соответствующий вывод установлен в логический 0. |

|

|

|

||||||||||||

|

|

|

|

1 - если соответствующий вывод установлен в логическую 1. |

|

|

|

||||||||||||

P1 |

|

|

Регистр порта 1. Чтение, запись аналогично порту 0. |

|

|

|

|

|

|||||||||||

P2 |

|

|

Регистр порта 2. Чтение, запись аналогично порту 0. |

|

|

|

|

|

|||||||||||

P3 |

|

|

Регистр порта 3. Чтение, запись аналогично порту 0. |

|

|

|

|

|

|||||||||||

PSW |

|

|

Регистр состояния |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

Бит 7 |

|

Бит 6 |

Бит 5 |

Бит 4 |

|

Бит 3 |

|

Бит 2 |

|

Бит 1 |

|

Бит 0 |

|

|||

|

|

|

Бит 7: CY - флаг переноса, устанавливается если результат последней арифметической операции |

||||||||||||||||

|

|

|

приводит к появлению переноса (Carry) или заема (Borrow). Сбрасывается в 0 после следующей |

||||||||||||||||

|

|

|

арифметической операции. |

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

Бит 6: Auxiliary Carry Flag - дополнительный флаг переноса, используемый при операции |

||||||||||||||||

|

|

|

десятичной коррекции. Сбрасывается в 0 после следующей арифметической операции. |

||||||||||||||||

|

|

|

Бит 5: User Flag 0 - пользовательский флаг 0 общего назначения. |

|

|

|

|||||||||||||

|

|

|

Биты 4-3: RS1-RS0 - Register Bank Select - биты выбора банка регистров. Биты выбирают один из |

||||||||||||||||

|

|

|

четырех банков регистров: |

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

00 - банк 0 с адресами 0x00-0x07 |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

01 - банк 1 с адресами 0x08-0x0F |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

10 - банк 2 с адресами 0x10-0x17 |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

11 - банк 3 с адресами 0x18-0x1F |

|

|

|

|||||||

|

|

|

Бит 2: OV - Overflow Flag - флаг переполнения, устанавливается в 1, если последняя |

||||||||||||||||

|

|

|

арифметическая операция вызвала перенос (при сложении), заем (при вычитании) или |

||||||||||||||||

|

|

|

переполнение (при умножении или делении). Сбрасывается в 0 после следующей |

||||||||||||||||

|

|

|

арифметической операции. |

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

Бит 1: User Flag 1 - пользовательский флаг 1 общего назначения. |

|

|

|

|||||||||||||

|

|

|

Бит 0: Parity Flag (только чтение) - бит четности. Устанавливается в 1, если сумма восьми битов в |

||||||||||||||||

|

|

|

аккумуляторе - нечетная, и обнуляется, если сумма четная. |

|

|

|

|

|

|||||||||||

SP |

|

|

Регистр указателя стека. Однобайтный регистр указателя стека содержит текущее значение |

||||||||||||||||

|

|

|

верхнего адреса стека. |

|

|

|

|

|

|

|

|

|

|

|

|

||||

9

3. Система команд х51 совместимых микроконтроллеров

Список команд ядра CIP-51 [1,3,4,8], количество байтов, занимаемое каждой командой, и количество тактов требуемых на выполнение, приведены в таблице 3. При составлении этой таблицы были приняты следующие умолчания:

фразу «прибавить регистр к A» следует понимать «прибавить содержимое регистра к содержимому аккумулятора»;

результаты любых действий заносятся в аккумулятор (А), если не указано иное;

регистр (Rn) – любой из 8 регистров R0-R7 выбранного в данный момент банка;

косвенно адресуемый байт (@Ri) – ячейка памяти, адрес которой записан в

регистре R0 или R1, может указывать на любой адрес памяти данных от 0х00 до 0хFF;

прямо адресуемый байт (direct) – это 8-битный адрес из адресного пространства памяти данных, от 0х00 до 0х7F он указывает на память данных, от 0х80 до 0xFF указывает на регистры специальных функций (SFR);

константа (#data) – непосредственно адресуемая 8-битная константа;

константа 16 бит (#data16) – непосредственно адресуемая 16-битная константа;

бит (bit) – прямо адресуемый бит из побитово адресуемого пространства или бит регистра специальных функций (SFR);

метка (rel) – 8-битная знаковая константа, служащая для реализации всех функций условных переходов, может принимать значения от -128 до +127;

11 битный адрес (addr11) – используется в командах ACALL и AJMP для коротких переходов в пределах 2кбайт памяти команд;

16 битный адрес (addr16) – полный адрес используется в командах LCALL и LJMP для переходов в любое место памяти команд.

Таблица.3.

Список команд CIP-51

№ |

Мнемоническое |

Краткое описание |

Кол-во |

Кол-во |

|

описание |

байтов |

тактов |

|||

|

|

||||

|

|

Арифметические операции (раздел 3.2) |

|

|

|

1 |

ADD A, Rn |

Прибавить регистр к A |

1 |

1 |

|

2 |

ADD A, direct |

Прибавить прямо адресуемый байт к A |

2 |

2 |

|

3 |

ADD A, @Ri |

Прибавить косвенно адресуемый байт к A |

1 |

2 |

|

4 |

ADD A, #data |

Прибавить константу к A |

2 |

2 |

|

5 |

ADDC A, Rn |

Прибавить регистра к A с учетом флага переноса |

1 |

1 |

|

6 |

ADDC A, direct |

Прибавить прямо адресуемый байт к A с учетом флага |

2 |

2 |

|

переноса |

|||||

|

|

|

|

||

7 |

ADDC A, @Ri |

Прибавить косвенно адресуемый байт к A с учетом |

1 |

2 |

|

флага переноса |

|||||

|

|

|

|

||

8 |

ADDC A, #data |

Прибавить константу к A с учетом флага переноса |

2 |

2 |

|

9 |

SUBB A, Rn |

Вычесть регистр из А с заемом из флага переноса |

1 |

1 |

|

10 |

SUBB A, direct |

Вычесть прямо адресуемый байт из А с заемом из |

2 |

2 |

|

флага переноса |

|||||

|

|

|

|

||

11 |

SUBB A, @Ri |

Вычесть косвенно адресуемый байт из А с заемом из |

1 |

2 |

|

флага переноса |

|||||

|

|

|

|

||

12 |

SUBB A, #data |

Вычесть константу из А с заемом из флага переноса |

2 |

2 |

|

13 |

INC A |

Инкрементировать А (увеличить на единицу) |

1 |

1 |

|

14 |

INC Rn |

Инкрементировать регистр |

1 |

1 |

|

15 |

INC direct |

Инкрементировать прямо адресуемый байт |

2 |

2 |

|

16 |

INC @Ri |

Инкрементировать косвенно адресуемый байт |

1 |

2 |

|

17 |

DEC A |

Декрементировать A (уменьшить на единицу) |

1 |

1 |

|

18 |

DEC Rn |

Декрементировать регистр |

1 |

1 |

|

19 |

DEC direct |

Декрементировать прямо адресуемый байт |

2 |

2 |

|

20 |

DEC @Ri |

Декрементировать косвенно адресуемый байт |

1 |

2 |

|

21 |

INC DPTR |

Инкрементировать регистр DPTR |

1 |

1 |

10