Лабораторная работа №1

Ввод-вывод данных, маскирование данных.

Цель работы – изучить варианты подключения простейших устройств ввода – вывода к МК АТ89S8253, способы маскирования данных.

Теоретическое введение

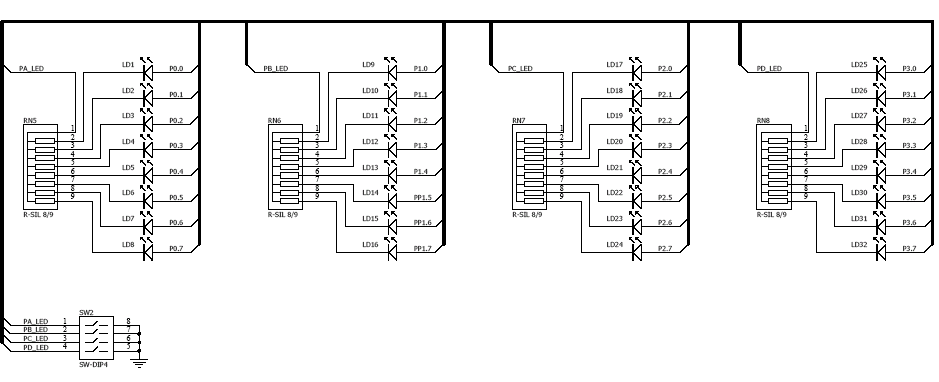

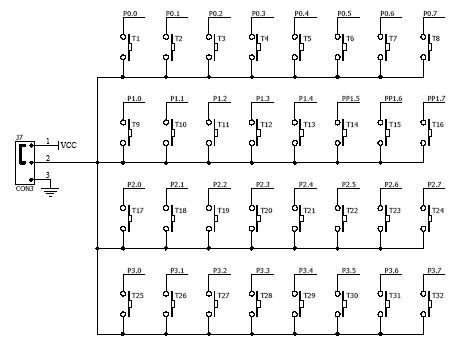

Порты ввода/вывода. Для подключения периферии МК имеет 4 8‑битных двунаправленных порта ввода/вывода, подключенных к внешним индикаторам и кнопкам как показано на рисунках 1 и 2.

Рисунок 1 схема подключения индикаторов-светодиодов

Рисунок 2 схема подключения кнопок.

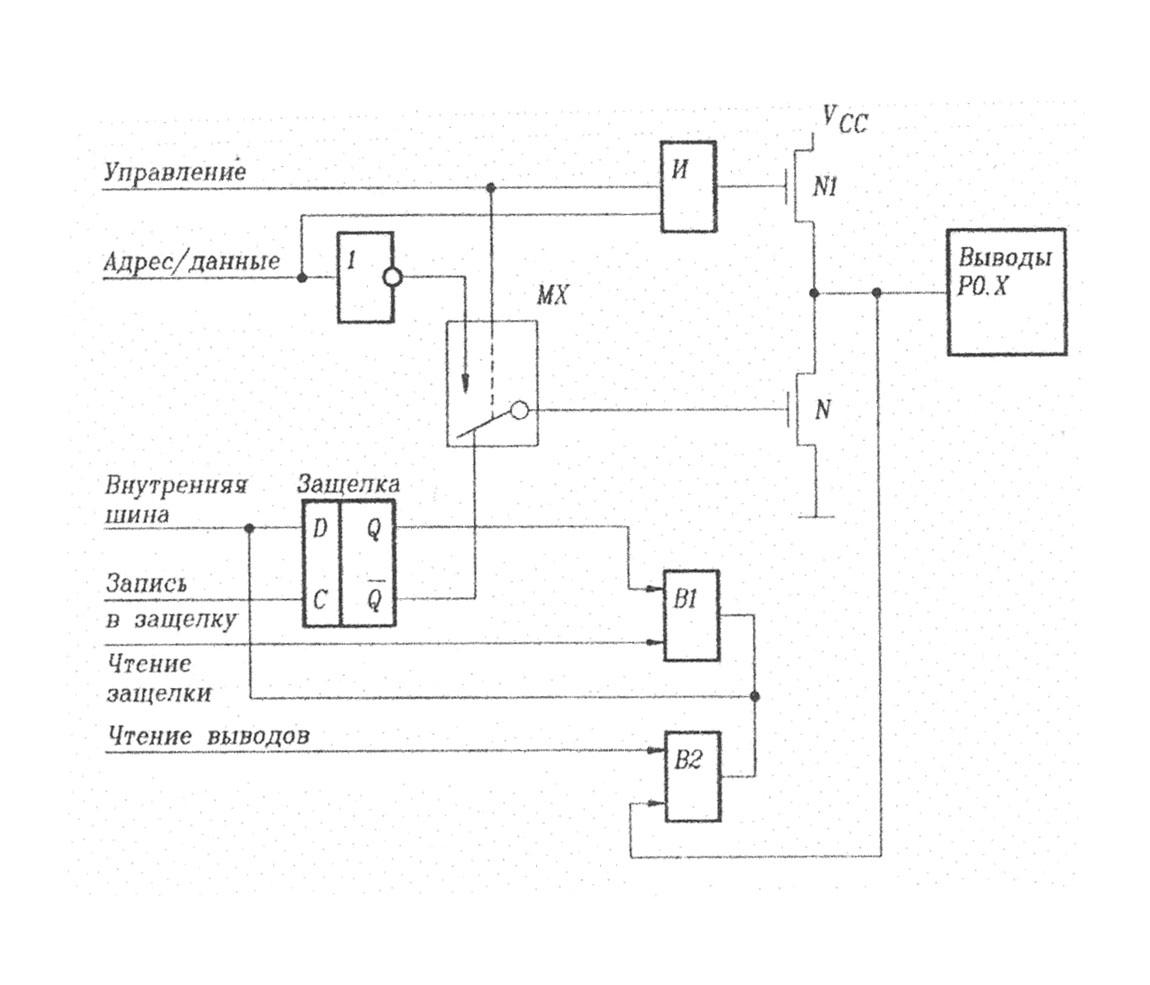

В данном МК нет регистра специального назначения, определяющего направление передачи информации, поэтому, направление определяется по сигналу записи, поступающему на фиксатор-защелку (см пример на Рис.3).

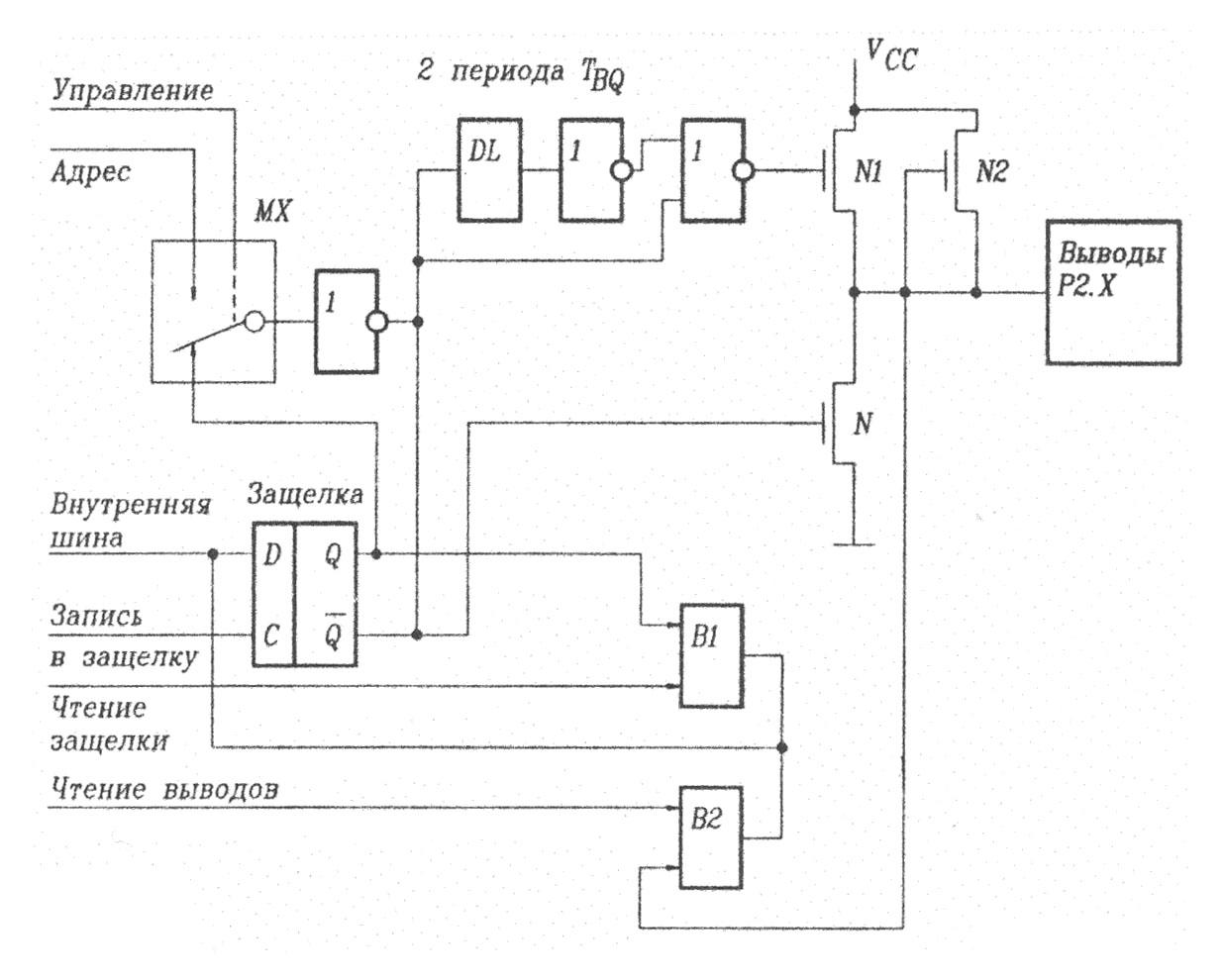

Рисунок 3. Схема электрическая порта 0 МК.

Порт Р0 не имеет внутренних подтягивающих резисторов. Транзистор N1 в выходном каскаде выводов порта Р0 открыт только тогда когда через эти выводы выдается «1» при обращениях к внешней памяти. Во всех других режимах работы транзистор N1 заперт. Таким образом, при использования Р0 в качестве выходного порта общего назначения, на его выводы устанавливают внешние подтягивающие резисторы для задания уровня «1». Запись «1» в защелку вывода порта Р0 закрывает транзистор N и при отсутствии внешнего подтягивающего резистора переводит выводы порта в высокоимпедансное состояние и они могут использоваться как входные. Каждый из выводов порта может работать независимо от других.

Все разряды фиксаторов-защелок (D-триггеров) портов Р0-Р3 по сбросу устанавливаются в «1». Если защелка вывода порта содержит «0», порт работает как выходной, если «1», то как входной.

Через Р0:

-

выводится младший байт адреса А0…А7 при работе с внешней памятью,

-

выдается и принимается байт данных,

-

задаются данные при программировании внутреннего ЭСППЗУ и читается содержимое внутренней памяти программ.

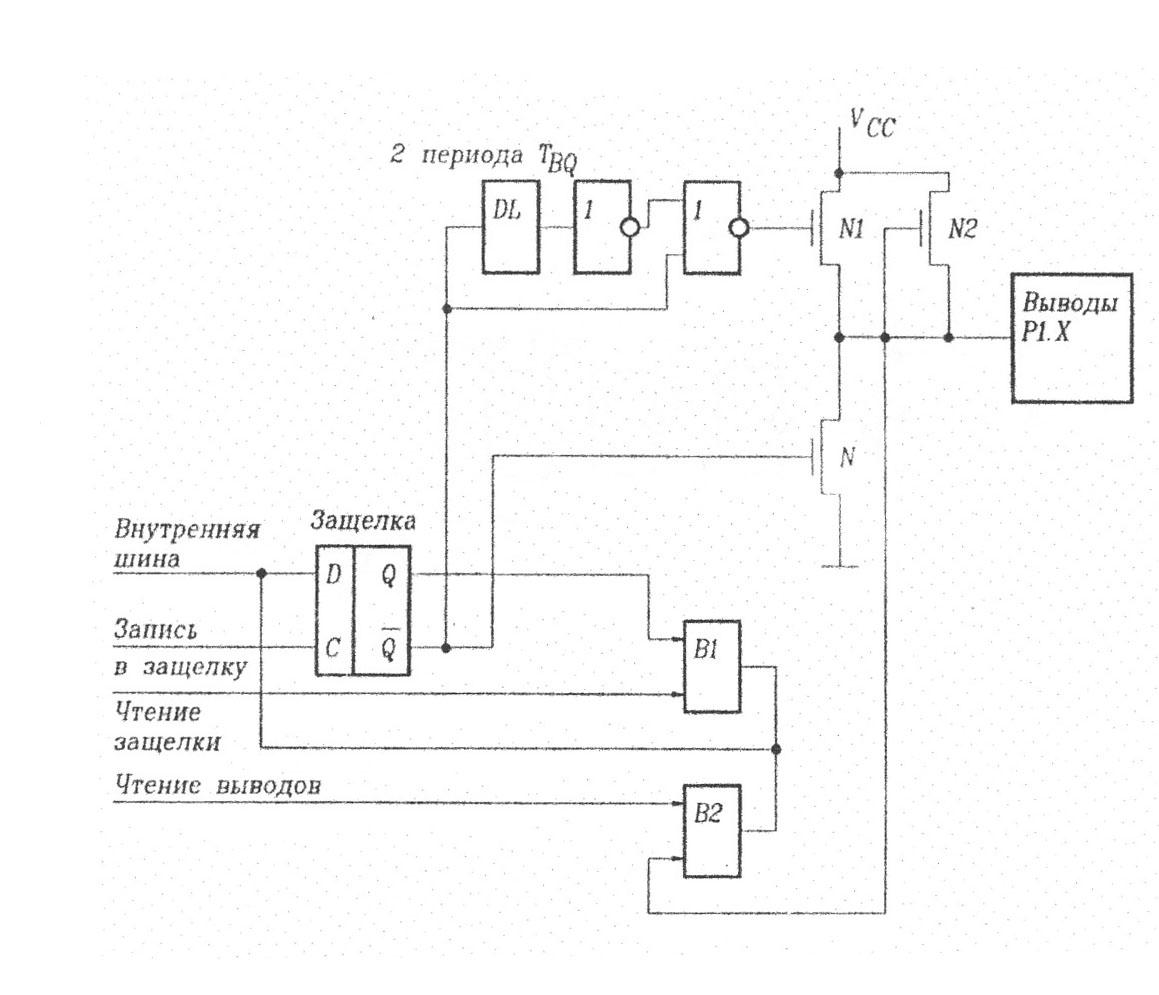

Ниже, на рисунках 4-6 приведены принципиальные схемы портов ввода/вывода микросхем серии МК51, построенных по n-МОП технологии. Микросхемы, построенные по КМОП-технологии (AT89S8253) отличаются от них только выходным каскадом (типом выходных транзисторов и способами их подключения), управляющая логика не меняется.

Порт Р1- двунаправленный TTL-совместимый порт ввода/вывода. Р1, как и порты Р2, Р3 имеет внутренние подтягивающие резисторы, подключенные к цепи питания и выполненные в виде транзисторов N2 (рисунки 4-6).

Рисунок 4. Электрическая схема порта Р1

Использование выходных каскадов позволяет снизить время переключения из состояния «0» в состояние «1» (за счет использования N1), увеличить выходной ток и снизить шумы. На рисунке 4 транзисторы N1 и N2 подключены к источнику питания, а N к общей шине.

Через Р1 задается младший байт адреса при программировании внутреннего ЭСППЗУ и при чтении внутренней памяти программ.

Порт Р2. Через этот порт:

-

выводится старший байт адреса А8-А15 при работе с внешней памятью программ и внешней памятью данных,

-

задается старший байт (А8-А14) адреса при программировании внутреннего ЭСППЗУ и при чтении внутренней памяти программ.

Рисунок 5. Электрическая схема порта Р2.

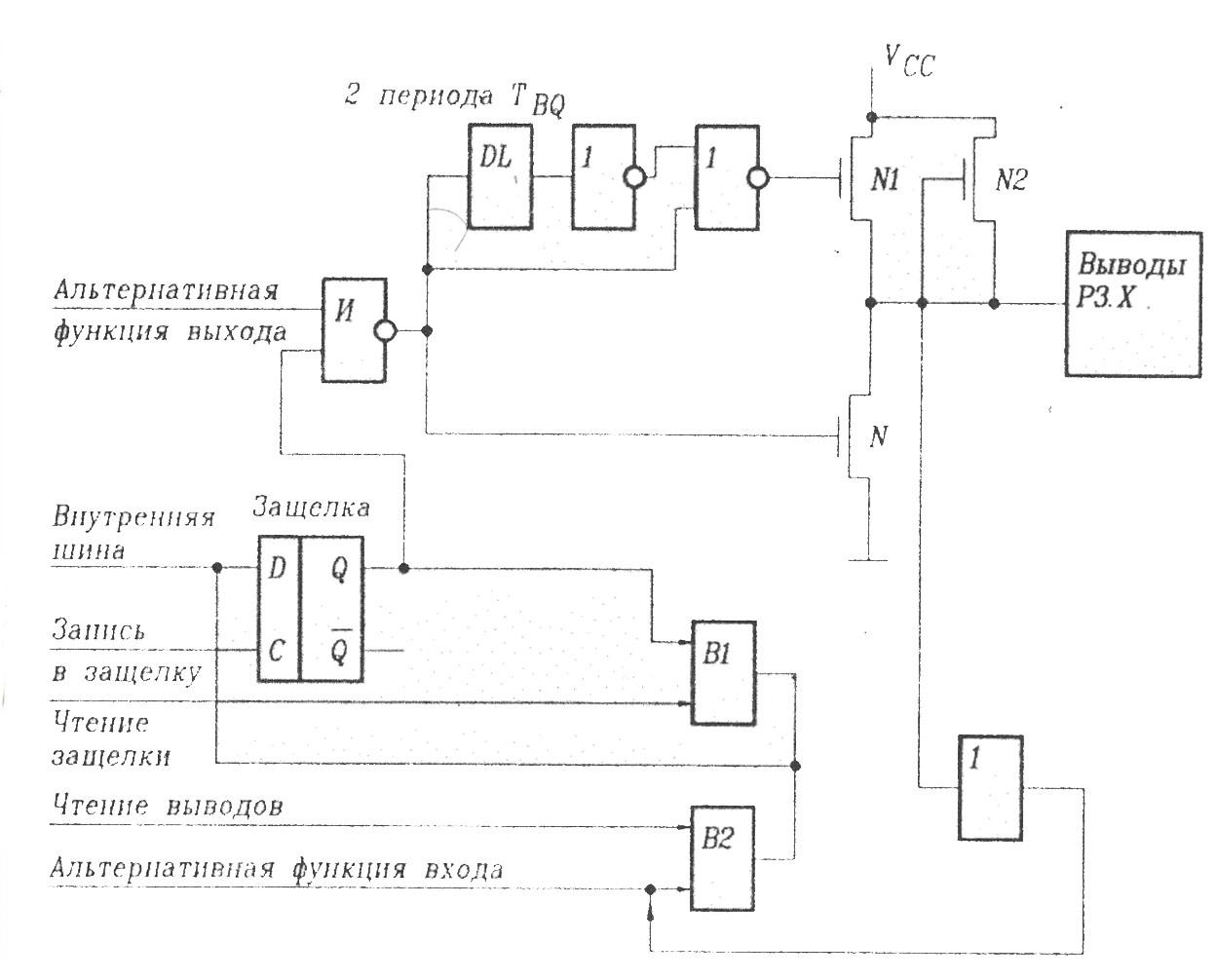

Порт Р3. Каждая линия Р3 кроме универсального назначения (линий ввода/вывода) имеет альтернативную функцию (см таблицу описания МК). Альтернативная функция реализуется, если в соответствующем этой линии разряде фиксатора-защелки записана «1» (см рисунок 6).

Рисунок 6. Электрическая схема порта Р3

Чтение и запись информации

Чтение данных организуется 2 типами команд: командами, считывающими информацию с выходов защелок и командами, считывающими информацию с внешних контактов выводов порта. Команды, считывающие информацию с выходов защелок, реализуют режим «чтение-модификация-запись», заключающийся в том, что команда считывает состояние защелки, если нужно, изменяет его и записывает результат обратно в защелку. Чтение состояния порта с выхода защелки позволяет исключить неправильную интерпретацию уровня напряжения на выводе порта. Например, если порт используется для управления базой n-p-n транзистора и в защелке записана «1» транзистор открывается. Если после того как транзистор откроется МК прочитает состояние внешнего контакта, то получит «0», так как это напряжение базы открытого транзистора. Если же считать состояние вывода из защелки, то получим правильный результат – «1».

Команды, работающие в режиме «чтение-модификация-запись»:

|

ANL |

Логическое И |

|

ORL |

Логическое ИЛИ |

|

XRL |

Исключающее ИЛИ |

|

CLR |

Очистка аккумулятора или бита |

|

CPL |

Инверсия аккумулятора или бита |

|

JBC |

Переход, если бит установлен и очистка этого бита |

|

INC |

Инкремент |

|

DEC |

Декремент |

|

DJNZ |

Декремент и переход, если не равно нулю |

|

MOV |

Пересылка |

|

SETB |

Установка бита |

Запись данных. При записи данных новое значение записывается в защелку в последней фазе машинного цикла команды. Однако, новое содержимое выводится на выходной контакт порта только в начальной фазе следующего машинного цикла

Маскирование данных.

Очень часто при написании программы требуется маскировать данные (накладывать маску). Маска – управляющий код, разрешающий/запрещающий отдельные разряды основного кода. Таким образом, маскирование – изменение некоторых разрядов (битов) числа.

Наиболее часто маскирование организуют с помощью следующих операций:

-

логическое «И» - умножение числа (в аккумуляторе) и маски. Очищает бит числа, если в соответствующем бите маски будет записан «0», и не изменяет его, если в бите маски записана «1». Обнуляет отдельные биты числа;

-

логическое «ИЛИ» - сложение числа (в аккумуляторе) и маски. Устанавливает бит числа в «1», если в таком же бите маски будет записана «1», не изменяет его, если в этом юите – «0». Применяется для установки отдельные битов в «1»;

-

Логическое «исключающее ИЛИ» числа (в аккумуляторе) и маски. Инвертирует содержание бита числа, если в соответствующем бите маски записана «1» и не изменяет его, если в этом бите - «0».

Пример маскирования чисел приведен в таблице 1:

Таблица 1

|

Операция (в 16-м коде) |

Число (двоичный код) |

Маска (двоичный код) |

Результат маскирования |

комментарий |

|

0x3A & 0xAC |

00111010 |

10101100 |

00101000 |

Логическое умножение байтов |

|

0x3A | 0xAC |

00111010 |

10101100 |

10111110 |

Логическое сложение байтов |

|

0x3A ^ 0xAC |

00111010 |

10101100 |

10010110 |

Логическое «исключающее ИЛИ» |

Проведение таких операций возможно как с содержимым аккумулятора и внутренними регистрами МК. В приведенной ниже программе дан пример маскирования отдельных битов.