- •Факультет Информационных Технологий Кафедра «Информатики и вычислительной техники»

- •Содержание

- •Глава 1. Введение

- •Техническое задание на курсовое проектирование

- •Цели курсового проектирования

- •Задачи курсового проектирования

- •Необходимые технические и программные средства:

- •Глава 2. Теоретические сведения

- •2.1 Организация компьютерных систем

- •2.2 Устройство процессора (классическая архитектура эвм)

- •2.3 Обзор существующих архитектур

- •2.4 Принципы проектирования процессоров

- •2.5 Система команд процессора

- •2.6 Организация устройств процессора

- •Глава 3. Исследуемые устройства

- •3.1 Обзор архитектуры mips

- •Глава 4. Проектирование

- •4.1 Описание устройства

- •4.2 Этапы проектирования

- •4.2.1 Описание формата и точного набора инструкций

- •4.2.2 Разработка комбинационных и последовательных блоков процессора

- •4.2.3 Разработка операционного устройства

- •4.2.4 Разработка устройства управления

- •4.3 Временные диаграммы

- •4.4 Расчет быстродействия

- •Глава 5. Заключение

- •5.1 Список литературы

4.2.2 Разработка комбинационных и последовательных блоков процессора

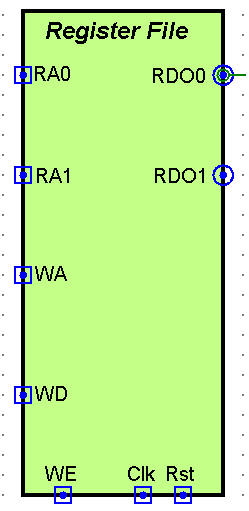

Разработка устройства началась с этапа проектирования регистрового блока. Блок состоит из 15 16-и битных регистров и одного константного нуля. Коммутация и выбор регистров происходит с помощью двух мультиплексоров и одного демультиплексора. Регистры имеют общие входы обнуления и записи данных. Выбор регистра для записи в него данных происходит путем подачи сигнала разрешения с демультиплексора. Регистровый блок имеет два отдельных выхода, для асинхронного считывания данных из регистров.

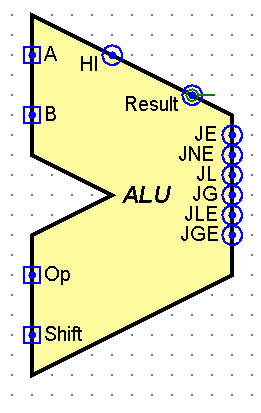

Арифметико-логическое устройство поддерживает 16 арифметических и логических операций. Данные поступают одновременно на все входы комбинационных схем АЛУ, выбор операции осуществляется переключением выходного мультиплексора. В АЛУ также присутствует схема сравнения двух операндов. Результат сравнения подается на шесть выходов (=, ≠, <, >, <=, >=). Вывод старшей части результата в операциях умножения и деления осуществляется переключением одноадресного мультиплексора. Выбор осуществляется нулевым битом операционного поля АЛУ.

4.2.3 Разработка операционного устройства

Так как тракт данных процессора является многотактным, появляется необходимость в дополнительных неархитектурных регистрах. В них записываются промежуточные значения после завершения такта.

Построение тракта данных операционного устройства начинается с добавления счетчика, модуля оперативной памяти, регистра инструкций и регистра данных.

После считывания очередной инструкции из оперативной памяти, она записывается в регистр инструкций. Далее инструкция разбивается на блоки битов в соответствии с форматом команд процессора. КОП передается в управляющее устройство, остальные данные проходят дальше по тракту данных и в зависимости от конкретного набора «Y» произойдет, например, запись или чтение из регистрового файла или преобразование данных в АЛУ или же запись нового значения в счетчик команд.

После завершения всех тактов текущей операции, будет выполнен переход к адресу следующей команды.

4.2.4 Разработка устройства управления

Разработка устройства управления началась с определения необходимой разрядности данных и адреса ПЗУ микрокоманд и ПЗУ дешифратора операций. После этого в схему был добавлен счетчик адреса и схема формирования адреса следующей микрокоманды. Принцип работы данного устройства управления прост. По нулевому адресу ПЗУ микропрограмм располагается микропрограмма выборки очередной команды из оперативной памяти. Данная микропрограмма выполняется всегда в начале каждого командного цикла. После выборки команды, ПЗУ микропрограмм адресуется ПЗУ дешифратора операций, на выходе которого формируется адрес смещения, указывающий на начало необходимой микропрограммы в ПЗУ микропрограмм. После выполнения микропрограммы снова происходит переход в нулевой адрес ПЗУ, где располагается микропрограмма выборки следующей команды или же, если текущая микропрограмма реализует условный переход, то в зависимости от результата проверки условия, будет произведен переход по адресу, находящемуся в адресной части микрокоманды (если условие ИСТИННО) или переход в нулевой адрес ПЗУ (если условие ЛОЖНО).

Формат микрокоманд устройства управления:

Операционная

микрокоманда Микрокоманда

условного перехода

0 |

Загрузка СЧ |

Сброс СЧ |

Y |

|

1 |

Загрузка СЧ |

Сброс СЧ |

X |

A |