- •Глава 1. Сборка процессора 8

- •Глава 2. Дешифратор и устройство управления 16

- •Глава 3. Реализация алгоритма 17

- •Глава 1. Сборка процессора.

- •– Архитектура команд

- •1.1.3 Команды 1 типа.

- •Проектирование шины и памяти озу.

- •1.3.1 Работа Алу

- •1.4.1 Регистры специального назначения

- •1.4.2 Регистры общего назначения

- •Глава 2. Выбор типа процессора и устроство управления с дешифратором.

- •2.1 Выбор типа процессора.

- •2.2 Устроство управления и дешифратор.

- •Глава 3. Реализация алгоритма.

- •3.1 Изменение процессора.

- •3.2 Решение задачи.

МИНЕСТЕРСТВО ЦИФРОВОГО РАЗВИТИЯ, СВЯЗИ И МАССОВЫХ КОММУНИКАЦИЙ РОССИЙСКОЙ ФЕДЕРАЦИИ

Ордена Трудового Красного Знамени федеральное государственное бюджетное учреждение высшего образования

«Московский технический университет связи и информатики»

Курсовая работа

«Создание процессора»

по дисциплине

«Введение в информационные технологии»

Выполнил: студент гр. БВТ2202

Дави говно, хочу быть лысым

.

Проверил: Симонов С.Е.

Москва, 2022 г.

СОДЕРЖАНИЕ

Введение 3

Глава 1. Сборка процессора 8

Архитектура команд 8

1.1.1 Команды 2 типа 8

1.1.2 Команды 3 типа 11

1.1.3 Команды 1 типа 12

Проектирование шины и памяти ОЗУ. 13

АЛУ 14

1.3.1 Работа АЛУ 14

1.3.2 Флаги 14

Регистры 15

1.4.1 Регистры специального назначения 15

1.4.2 Регистры общего назначения 16

Глава 2. Дешифратор и устройство управления 16

Выбор типа процессора. 16

Устроство управления и дешифратор. 18

Глава 3. Реализация алгоритма 17

Изменение процессора 17

Решение задачи 19

Вывод 20

Источники информации 21

Введение

История развития производства процессоров полностью соответствует истории развития технологии производства прочих электронных компонентов и схем.

Первым этапом, затронувшим период с 1940-х по конец 1950-х годов, было создание процессоров с использованием электромеханических реле, ферритовых сердечников (устройств памяти) и вакуумных ламп.

Вторым этапом, с середины 1950-х до середины 1960-х, стало внедрение транзисторов. Транзисторы монтировались уже на близкие к современным по виду платы, устанавливавшиеся в стойки.

Третьим этапом, наступившим в середине 1960-х годов, стало использование микросхем. Первоначально использовались микросхемы низкой степени интеграции, содержавшие простые транзисторные и резисторные сборки, затем, по мере развития технологии, стали использоваться микросхемы, реализующие отдельные элементы цифровой схемотехники (сначала элементарные ключи и логические элементы, затем более сложные элементы — элементарные регистры, счётчики, сумматоры), позднее появились микросхемы, содержащие функциональные блоки процессора — микропрограммное устройство, арифметическо-логическое устройство, регистры, устройства работы с шинами данных и команд.

Четвёртым этапом, в начале 1970-х годов, стало создание, благодаря прорыву в технологии, БИС и СБИС (больших и сверхбольших интегральных схем, соответственно), микропроцессора — микросхемы, на кристалле которой физически были расположены все основные элементы и блоки процессора.

Сейчас слова «микропроцессор» и «процессор» практически стали синонимами, но тогда это было не так, потому что обычные (большие) и микропроцессорные ЭВМ мирно сосуществовали ещё, по крайней мере, 10—15 лет, и только в начале 1980-х годов микропроцессоры вытеснили своих старших собратьев.

Как же работает процессор? Давайте разберемся сначала с основными компонентами процессора.

Информационная связь между устройствами компьютера осуществляется через системную шину (системную магистраль).

Шина – это кабель, состоящий из множества проводников. Количество проводников, входящих в состав шины, является максимальной разрядностью шины.

Системная шина, в свою очередь, представляет собой совокупность

шины данных, служащей для переноса информации;

шины адреса, которая определяет, куда переносить информацию;

шины управления, которая определяет правила для передачи информации;

Системная шина характеризуется тактовой частотой и разрядностью. Количество одновременно передаваемых по шине бит называется разрядностью шины.

Тактовая частота характеризует число элементарных операций по передаче данных в 1 секунду. Разрядность шины измеряется в битах, тактовая частота – в мегагерцах.

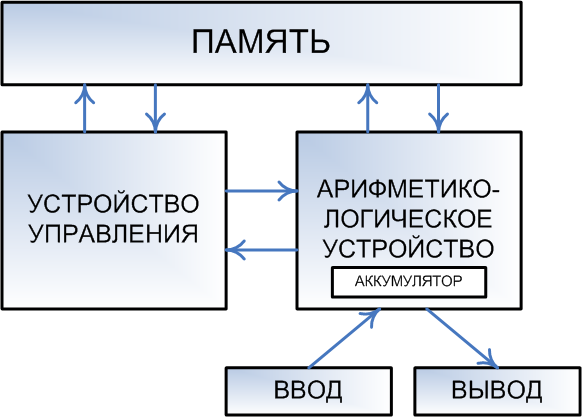

Устройство управления (УУ) формирует адрес команды, которая должна быть выполнена в данном цикле, и выдает управляющий сигнал на чтение содержимого соответствующей ячейки запоминающего устройства (ЗУ). Считанная команда передается в УУ. По информации, содержащейся в адресных полях команды, УУ формирует адреса операндов и управляющие сигналы для их чтения из ЗУ и передачи в арифметико-логическое устройство (АЛУ). После считывания операндов устройство управления по коду операции, содержащемуся в команде, выдает в АЛУ сигналы на выполнение операции. Полученный результат записывается в ЗУ по адресу приемника результата под управлением сигналов записи. Признаки результата (знак, наличие переполнения, признак нуля и так далее) поступают в устройство управления, где записываются в специальный регистр признаков. Эта информация может использоваться при выполнении следующих команд программы, например команд условного перехода.

Устройство ввода позволяет ввести программу решения задачи и исходные данные в ЭВМ и поместить их в оперативную память. В зависимости от типа устройства ввода исходные данные для решения задачи вводятся непосредственно с клавиатуры, либо они должны быть предварительно помещены на какой-либо носитель (дисковый накопитель).

Устройство вывода служит для вывода из ЭВМ результатов обработки исходной информации. Чаще всего это символьная информация, которая выводится с помощью печатающих устройств или на экран дисплея.

Запоминающее устройство или память – это совокупность ячеек, предназначенных для хранения некоторого кода. Каждой из ячеек присвоен свой номер, называемый адресом. Информацией, записанной в ячейке, могут быть как команды в машинном виде, так и данные.

Обработка данных и команд осуществляется посредством арифметико-логического устройства (АЛУ), предназначенного для непосредственного выполнения машинных команд под действием устройства управления. АЛУ и УУ совместно образуют центральное процессорное устройство (ЦПУ). Результаты обработки передаются в память.

Дешифратор команд позволяет процессору расшифровать данные из шины, тем самым улучшить работу ЦПУ, упрощая ее работу доп. возможностями. Он преобразует n-разрядный двоичный код в логический сигнал, появляющийся на том выходе, десятичный номер которого соответствует двоичному коду. Число входов и выходов в так называемом полном дешифраторе связано соотношением m=2**n, где n- число входов, а m— число выходов. На неполном же дешифраторе число выходов меньше, чем максимальное возможное количество.

Всего есть 2 основных архитектуры процессора – Гарвардская и архитектура Фон Неймона. Главное их отличие это принцип совместного хранения команд и данных в памяти компьютера.

Гарвардская

архитектура была

разработана Говардом Эйкеном в конце

1930-х годов в Гарвардском университете

с целью увеличить скорость выполнения

вычислительных операций и оптимизировать

работу памяти. Она характеризуется

физическим разделением памяти команд

(программ) и памяти данных. В ее оригинальном

варианте использовался также отдельный

стек для хранения содержимого программного

счетчика, который обеспечивал возможности

выполнения вложенных подпрограмм.

Каждая память соединяется с процессором

отдельной шиной, что позволяет одновременно

с чтением-записью данных при выполнении

текущей команды производить выборку и

декодирование следующей команды.

Благодаря такому разделению потоков

команд и данных и совмещению операций

их выборки реализуется более высокая

производительность, чем при архитектуры

Фон Неймона.

Архитектура фон неймона характеризуется использованием общей оперативной памяти для хранения программ, данных, а также для организации стека. Для обращения к этой памяти используется общая системная шина, по которой в процессор поступают и команды, и данные.

Это позволяет данной архитектуре получить несколько преимуществ:

Наличие общей памяти позволяет оперативно перераспределять ее объем для хранения отдельных массивов команд, данных и реализации стека в зависимости от решаемых задач. Таким образом, обеспечивается возможность более эффективного использования имеющегося объема оперативной памяти в каждом конкретном случае применения.

Использование общей шины для передачи команд и данных значительно упрощает отладку, тестирование и текущий контроль функционирования системы, повышает ее надежность.

Свой процессор же процессор я создал на архитектуре Фон Неймона и попробовал сделать без регистрового файла. Он облегчает работу и улучшает производительность процессора, но кажется не обязательным для понимания работы процессора, как и устройство ввода. Также отказ от регистрового файла сильно облегчит создание УУ и дешифратора, что позволило объединить их в один блок. Общая структура моего процессора такая:

Основные принципы работы процессора:

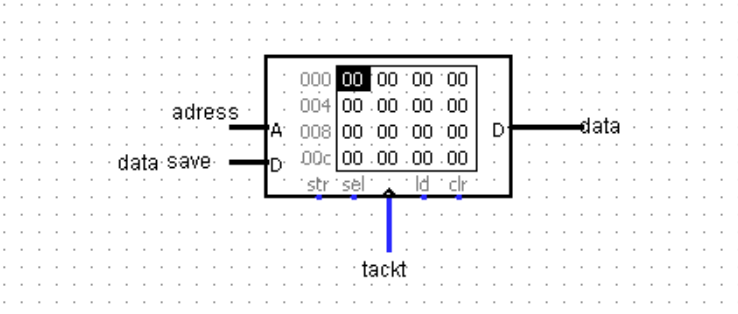

В ОЗУ хранятся команд, адреса и данные.

На вход address со счетчика или другого устройства поддается номер ячейки адреса, в которой храняться данные. Вход tackt позволяет записать данные из data save по в address если на подается 1. Выход данных обозначается data.

Счетчик же обновляется при изменении тактового генератора и других команд.

Из data идет шина данных в специальные регистры, которые управляют АЛУ и другими элементами (о них позже) и в регистр temp. Эти два регистра работают по разному фронту, поэтому после подачи команд и адреса в спец. регистры происходит изменение адресса в ОЗУ и данные попадают в temp, а после в АЛУ.

Со следующим тактом все команды выполняются (например результат из АЛУ записывается в аккумулятор, результаты из аккумулятора выводатся в регистр вывода и т.д.) и счетчик переключается с помощью тактового генератора на другой адрес в ОЗУ, чтобы выполнить следующую команду.

Запись на регистры, а значит и выполнение

тех или иных команд зависят от фронта

их работы. Передний фронт означает, что

запись происходит при смене сигнала с

0 на 1, а задний с 1 на 0, поэтому адресса

и команды не записываются в темп и не

идут дальше как числа для АЛУ. На схеме

каждый регистр подписан по какому фронту

он работает (p – передний,

z – задний)