Sbornik_PLIS

.pdf

На рисунке 2.17. представлены настройки Force Clock, в которых нас интересуют:

Signal Name– имя переменной (сигнала) значение которой мы задаем Leading Edge Value– передний фронт импульса

Trailing Edge Value – задний фронт импульса

Cancel after Time Offset– длительность этой установки

Period–период, с которым будут меняться значения Leading Edge Value и Trailing Edge Value

Для переключателя SW0 выставим Force Constant

Рис. 2.18. Настройки Force Constant

На рисунке 2.18. представлены настройки Force Constant, в которых нас интересуют:

Signal Name – имя переменной (сигнала) значение которой мы задаем ForcetoValue – значение константы

Cancel after Time Offset– длительность этой установкиForceClock

Для оставшихся переключателей SW1, SW2, SW3 установим с такими же значениями, как и на рисунке 2.17, но с периодами 2us, 5us и 1us соответ-

ственно. |

|

|

|

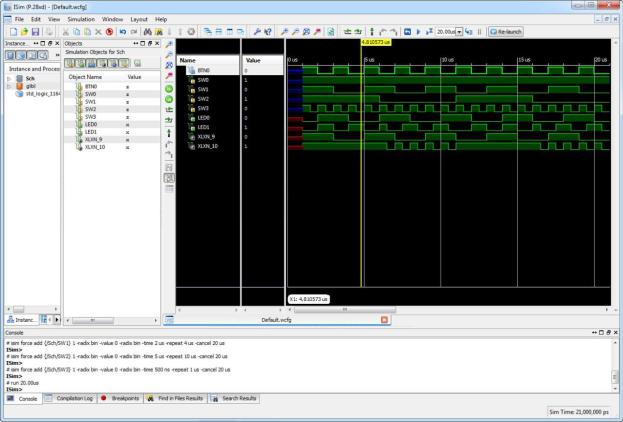

После |

запуска |

симуляции |

кнопкой Run All в верхнем меню |

должна |

получиться |

диаграмма, |

как на рисунке 2.19. |

Перетаскивая желтый флажок можно наблюдать значение переменных в

выбранный момент времени. |

|

Также можно сбросить симуляцию кнопкой Restart |

и выбрать другие |

значения Force Constant/ Force Constant для переменных.

Посмотрев работу цифрового устройства в режиме симуляции, окно симулятора iSim можно закрыть и перейти к следующему этапу проектирования.

31

Рис. 2.19. Симуляция проекта

2.2.4Создание связи с выводами отладочной платы

Впредыдущей лабораторной работе был рассмотрен способ создания связывающего файла Implementation Constraints File с помощью приложения

Plan Ahead (пункт 2.2.3).

Это не единственный способ создания такого файла. Наиболее быстрый, но менее наглядный способ это ручное создание такого файла.

Для этого в окне иерархии проекта (Вкладка Design слева сверху) нажать правой кнопкой и создать новый источник (New Source).

Впоявившемся окне мастера выбрать Implementation Constraints File и задать ему имя (Рис. 2.20). Чаще всего его называют pins (выводы), но название не принципиально. Главное, чтобы файл такого типа в проекте был только один.

После завершения создания файл откроется в редакторе (точно таком же, как и модули VHDL) и он будет пуст.

Синтаксис связывания имеет следующий вид: NET "Имя_Маркера" LOC = "Вывод_на_плате";

Если внимательно посмотреть на плату, рядом с каждым элементом есть его обозначение в виде БУКВА_ЦИФРЫ.

Соответственно, описание всех связей маркеров будет выглядеть так:

NET "SW0" LOC = "A10";

NET "SW1" LOC = "D14";

NET "SW2" LOC = "C14";

32

NET "SW3" LOC = "P15";

NET "LED0" LOC = "U18";

NET "LED1" LOC = "M14";

NET "BTN0" LOC = "N4";

Это всё, что должен содержать в себе Implementation Constraints File для данной работы.

Рис. 2.20. Создание Implementation Constraints File

2.2.5 Создание конфигурационного файла

Создание конфигурационного файла подробно описано в пункте 2.2.4

2.2.6 Конфигурирование отладочной платы

Конфигурирование отладочной платы подробно описано в пункте 2.2.5

3. Методические указания

Общие сведения о языке программирования VHDL. Базовая структура VHDL-файла.

Проекты цифровых устройств (ЦУ), созданные с помощью VHDL, имеют (как правило) иерархическую структуру. Каждый автономный проектируемый модуль (субблок проектируемого ЦУ) имеет строго определенный интерфейс взаимодействия с другими модулями и точную спецификацию внутреннего устройства проектируемого модуля.

Спецификации модулей VHDL-проектов могут использовать или математические алгоритмы, описывающие их работу, или описание аппаратной структуры проектируемого модуля. Таким образом описание модуля может

33

иметь поведенческую или структурную форму. Модель, отражающая объект проектирования в форме правил преобразования входных данных в выходные называется поведенческой (behavioral). Поведенческая форма позволяет описывать систему в терминах того, что она делает (а не в терминах элементов, компонентов и соединений между ними). Поведенческая форма может быть булевым выражением, описанием межрегистровых пересылок или описанием в алгоритмической форме. Поведенческая форма определяет зависимость между входными и выходными сигналами.

Сигналы являются отдельным классом объектов языка VHDL, отличным от классов переменных и констант, достаточно традиционных для языков высокого уровня. Понятие сигнала не имеет аналогов в языках программирова-

ния типа FORTRAN, С, PASCAL и др [1].

Цифровые системы работают во времени, преобразуя и передавая сигналы. Естественно, что понятие сигнала является базовым в языке описания аппаратуры — языке VHDL. Сигналы являются абстракцией, представлением в модели на VHDL состояния проводников в структуре цифрового устройства.

В модели устройства на языке VHDL воздействия, изменяющие состояние сигнала, принимают форму присваивания значения сигналу. Последовательные операторы присваивания значения сигналу имеют следующий синтаксис:

name<=[delay__mechanism] (value_expression [after time_expression]),

где конструкции в квадратных скобках носят необязательный характер. Оператор присваивания значения сигналу (указывается именем name)

включает в себя как определение нового значения сигнала (задается выражением value_expression), так и определение момента времени, в который сигнал примет это новое значение (задается конструкцией after time_expression). Время изменения значения сигнала, задаваемое в этом операторе, определяется относительно модельного времени. В момент запуска модели модельное время равно 0. Когда выполняется оператор присваивания нового значения сигналу, указанное в нем время (определяется выражением time_expression после after) добавляется к текущему модельному времени; этим и определяется момент модельного времени, при наступлении которого сигнал примет новое значение.

Пример присваивания значений сигналу:

clk<='l' after t,'0' after 2*t; out1 <= inp1

Проект любого ЦУ на языке VHDL – это, прежде всего программа, которая содержит ключевые и зарезервированные слова. Эти слова не могут использоваться как имена сигналов или как идентификаторы. В языке VHDL ключевые слова, зарезервированные слова и определяемые пользователем идентификаторы нечувствительны к регистру.

Строки и комментарии в VHDL-программе начинаются с двух смежных дефисов (--) и при компиляции игнорируются компилятором так же, как символы конца строки и пробелы.

34

VHDL – это строго типизированный язык. Это означает, что все программные элементы данных (константа, переменная, сигнал) должны явно объявляться с обязательным указанием типа элемента. Кроме того, в отличие от других строго типизированных языков, не допускаются операции над разнотипными элементами без предварительного преобразования типов.

Вязыке VHDL (как и в классических языках программирования) из ключевых, зарезервированных слов и других лексических элементов строятся образования, которые принято называть операторами. Оператор, в языке VHDL, начинается с ключевого слова и заканчивается символом точки с запятой (;).

Вязыке VHDL операторы с точки зрения их функционального программного назначения (как при поведенческой, так и при структурной методологии описания проектов) принято делить на две основные группы:

Операторы объявления программных элементов данных и их типов, компонентов проектируемого ЦУ, их интерфейсов и архитектур, пользовательских типов, а также функций и процедур.

Выполняемые операторы.

Кроме основных операторов в языке VHDL принято выделять еще одну группу операторов, которую называют вспомогательными операторами передачи управления.

С точки зрения конструктивного устройства операторы обеих групп принято подразделять на два класса:

Простые (однострочные) операторы. Простой оператор представляет собой текстовую запись, располагающуюся, как правило, на одной строке, которая не содержит других операторов.

Составные (многострочные) операторы. Составной оператор пред-

ставляет собой текстовую запись, занимающую, как правило, много строк, которая содержит другие операторы.

Вструктуре языка VHDL имеется два фундаментальных оператора (составные по своему конструктивному устройству), которые поддерживают принцип системного проектирования. Принцип системного проектирования предполагает, что любое проектируемое ЦУ рассматривается как автономная подсистема, которая должна иметь:

идентификатор (т. е. должна быть объявлена);

способность взаимодействовать с другими проектируемыми подсистемами посредством своего интерфейса (входных/выходных портов);

описание внутренней структуры или алгоритма функционирования. Такими фундаментальными операторами в языке VHDL являются опера-

торы:

entity...is end entity...;

architecture...is end architecture...;

35

Как для всякого алгоритмического языка, для языка VHDL определена естественная последовательность выполнения исполняемых операторов. Это

– последовательность выполнения в порядке записи операторов программы. Операторы управления последовательностью действий позволяют про-

граммно изменять эту естественную последовательность, устанавливать зависимость хода выполнения программы от значений обрабатываемых данных. Такие операторы называются управляющими. Среди управляющих операторов – оператор условия if, оператор выбора case, оператор ожидания wait, операторы цикла loop, next, exit и др. Эти операторы называются последовательными [3,4].

Проект ЦУ, или его компонент, описанный с помощью языка VHDL, хранится в файле, который обычно снабжается расширением *.vhd.

Представленный в виде VHD-файла проект ЦУ может содержать другие объекты (подсистемы), которые в таком случае являются подчиненными компонентами системы верхнего уровня.

Любой компонент, независимо от того, является ли он автономным либо подчиненным компонентом, или же системой верхнего уровня, в свою очередь является совокупностью интерфейса (entity) и архитектуры

(architecture).

В объявлении интерфейса (entity declaration) содержится объявление портов (ports declaration) проектируемого компонента с внешним миром. Объявление портов проектируемого компонента определяет внешние входные и выходные интерфейсные сигналы, в то время как архитектура представляет собой набор таких взаимосвязанных программных элементов, как подчиненные компоненты, операторы process, операторы параллельных вычислений, последовательные операторы, подпрограммы. В типичном проекте содержится несколько таких взаимосвязанных объектов, предназначенных для выполнения преобразований, в ходе которых и обеспечивается собственно требуемая функциональность проекта.

4.Контрольные вопросы

1.Что такое язык VHDL?

2.Какова технология проектирования цифровых систем с использованием

VHDL?

3.Поясните принципы интерпретации поведения дискретных устройств средствами моделирования.

4.Что называют проектом на языке VHDL?

5.Какую структуру имеют проекты, созданные на языке VHDL?

6.Что означает понятие «иерархическая структура проекта»?

7.Каковы формы описания модулей VHDL-проектов?

8.Поясните понятие «сигнал» в языке VHDL. Чему соответствует сигнал в логической схеме?

36

9.Чем сигнал отличается от переменной. Как записывается оператор назначения сигналов? Как записывается оператор присвоения значений перемен-

ной?

10.В какой части VHDL-кода необходимо указывать тип сигнала, который декларируется?

11.Где в описаниях на языке VHDL могут быть использованы операторы присвоения значений переменной и операторы назначения сигналов?

12.Что такое параллельный процесс? В каких состояниях бывают параллельные процессы?

13.Что означает строгая типизация языка VHDL?

14. Приведите классификацию типов данных языка VHDL.

15.Какие значения могут принимать данные типа bit? Какие операции определены на этом типе данных?

16.Для чего служит тип переменных time? Приведите пример записи временной константы этого типа. Какие операции определены над этим типом данных?

17.Что такое компонент языка VHDL? Каковы особенности декларации компонента?

18. Управляющие операторы языка VHDL. Привести пример использования этих операторов.

19.Поясните работу симулятора iSim.

20.С помощью временных диаграмм поясните принцип работы своего ЦУ.

5.Литература

1.Суворова Е. А., Шейнин Ю. Е. Проектирование цифровых систем на

VHDL. — СПб.: БХВ-Петербург, 2003. – С. 31-38, 73-86.

2.Тарасов И.Е. Разработка цифровых устройств на базе ПЛИС Xilinx с применением языка VHDL. – М.: Горячая линия-Телеком. – 2005. – С. 99115.

3.Бабак В.П. VHDL: справочное пособие по основам языка / В.П. Бабак, А.Г. Корченко, Н.П. Тимошенко, С.Ф. Филоненко и др. – М.: Издательский дом «Додэка-XXI», 2008.

4.Грушвицкий Р.И. Проектирование систем на микросхемах с программируемой структурой: учебное пособие для ВУЗов / Р.И. Грушвицкий, А.Х. Мурсаев, Е.П. Угрюмов. – СПб.: БХВ-Петербург, 2006. – С.373-451.

37

ПРИЛОЖЕНИЕ 2.1

Листинг файла demo_vhdl.vhd

----------------------------------------------------------------------------------

--Company:

--Engineer:

--Create Date: 13:00:29 04/24/2013

--Design Name:

--Module Name: demo_vhdl - Behavioral

--Project Name:

--Target Devices:

--Tool versions:

--Description:

--

--Dependencies:

--Revision:

--Revision 0.01 - File Created

--Additional Comments:

--

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

--Uncomment the following library declaration if using

--arithmetic functions with Signed or Unsigned values --use IEEE.NUMERIC_STD.ALL;

--Uncomment the following library declaration if instantiating

--any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity demo_vhdl is

Port ( inp1 : in STD_LOGIC; inp2 : in STD_LOGIC; inp3 : in STD_LOGIC; inp4 : in STD_LOGIC; out1 : out STD_LOGIC; out2 : out STD_LOGIC);

end demo_vhdl;

architecture Behavioral of demo_vhdl is

begin

out1 <= inp1 and inp2; out2 <= inp3 or inp4;

end Behavioral;

Листинг файла button.vhd

----------------------------------------------------------------------------------

--Company:

--Engineer:

--Create Date: 13:06:34 04/24/2013

--Design Name:

--Module Name: button - Behavioral

--Project Name:

--Target Devices:

--Tool versions:

38

--Description:

--Dependencies:

--Revision:

--Revision 0.01 - File Created

--Additional Comments:

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

--Uncomment the following library declaration if using

--arithmetic functions with Signed or Unsigned values

--use IEEE.NUMERIC_STD.ALL;

--Uncomment the following library declaration if instantiating

--any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity button is

Port ( btn : in STD_LOGIC; i1 : in STD_LOGIC;

i2 : in STD_LOGIC;

o1 : out STD_LOGIC;

o2 : out STD_LOGIC); end button;

architecture Behavioral of button is

begin

process(btn, i1, i2) begin

if btn = '1' then o1 <= not i1; o2 <= not i2;

else

o1 <= i1;

o2 <= i2; end if;

end process;

end Behavioral;

39

ЛАБОРАТОРНАЯ РАБОТА №3

1. Цель работы

Изучение системы автоматизированного проектирования (САПР) Xilinx ISE Web Pack. Изучение языка VHDL и реализация на ПЛИС цифровой схемы последовательного типа с использование как графического редактора и базы готовых элементов, так и модулей на языке описания аппаратуры

VHDL.

2.Задания для выполнения лабораторной работы

2.1Предварительная подготовка к выполнению лабораторной работы

1.Изучить описание к данной лабораторной работе и рекомендованную литературу.

2.Ознакомиться со средствами и методами программирования на языке

VHDL.

3.Используя сведения, полученные при подготовке, написать листинг программы, описывающей заданное устройство на языке VHDL. Данные для проектирования устройства можно получить у преподавателя или взять из Таблицы 3.1 (номер варианта уточнить у преподавателя). Подобрать вариант установки для значений переменных (констант) для выполнения симуляции так, чтобы отразить все возможные состояния разрабатываемого устройства и записать их в отчет.

4.Подготовить ответы на контрольные вопросы, приведенные в данном описании лабораторной работы.

5.Подготовить письменный отчет принятой на кафедре формы. Отчет должен содержать:

-титульный лист принятой на кафедре формы;

-номера лабораторной работы, варианта работы и формулировку цели работы;

-исходные данные выполняемого варианта;

-домашний расчет (схему, листинг программы, значения переменных и констант);

-результат выполнения работы (схема, временные диаграммы);

-краткие выводы по работе.

2.2Выполнение исследований в лаборатории

Разделы выполнения лабораторной работы:

2.2.1.Создание проекта

2.2.2.Проектирование цифрового устройства

2.2.3.Создание связи с выводами отладочной платы

2.2.4.Создание конфигурационного файла

2.2.5.Конфигурирование отладочной платы

Выполнение:

2.2.1Создание проекта

40