Sbornik_PLIS

.pdf

Если появится окно о сохранении изменений схемы, то нужно ответить

«Yes» (Рис. 1.13):

Рис. 1.13. Сохранение изменений в проекте

Следующее окно уведомляет, что данный процесс создаст Implementation Constraints File и свяжет его с текущим проектом. Нужно ответить тоже

«Yes» (Рис. 1.14):

Рис. 1.14. Уведомление о создании Implementation Constraints File

Запустится программа Plan Ahead, главное окно которой представлено на рисунке 1.15

Рис. 1.15. Главное окно программы Plan Ahead

11

Для привязывания выводов к плате нас интересует только нижняя часть окна – I/O Ports.

В этом вкладке представлены все наши маркеры, их типы (input, output) и другая информация. В блоке Site для каждого маркера нужно выбрать вывод, который указан на отладочной плате рядом с каждым элементом.

После выбора выводов вкладка I/O Ports должна иметь следующий вид

(Рис. 1.16):

Рис. 1.16. Вкладка I/O Ports

После выбора всех выводов нужно сохранить изменения, выбрав в меню

File – Save и закрыть программу Plan Ahead.

В окне проекта, в иерархии к нашей схеме добавился файл с расширением

*.ucf (Рис. 1.17)

Рис. 1.17. Implementation Constraints File

2.2.4. Создание конфигурационного файла

Всё готово для начала синтезирования устройства и подготовки файла, которым будет сконфигурирована ПЛИС в отладочной плате.

Для этого в окне процессов нужно дважды кликнуть на процессе Generate Programming File.

Этот процесс запустит всю необходимую цепочку процессов и при успешном выполнении создаст готовый конфигурационный файл. Если в

12

списке всех процессов (и особенно напротив процесса Generate Programming File) нет красных иконок, то создание прошло успешно. Пример успешного выполнения показан на рисунке 1.18

Рис. 1.18. Успешное создание конфигурационного файла

Успешно создав конфигурационный файл осталась финальная стадия – конфигурирование отладочной платы.

2.2.5. Конфигурирование отладочной платы

Для этих целей существует программа iMPACT из набора ISE Web Pack. Её можно запустить, дважды нажав на процессе Manage Configuration pro-

ject (Рис. 1.19)

Рис. 1.19 Запуск программы iMPACT

13

После запуска процесса откроется главное окно программы iMPACT (Рис.

1.20):

Рис. 1.20. Главное окно программы iMPACT

Здесь в рабочей области нужно кликнуть правой кнопкой и выбрать Initialize Chain или нажать CTRL+I.

В рабочей области появится ПЛИС и предложат выбрать конфигурационный файл. Нужно ответить Yes и выбрать файл с расширением *.bit, который расположен в папке проекта (Рис. 1.21)

Рис. 1.21. Выбор конфигурационного файла

На следующее окно с вопросом «Attach SPI or BPI PROM» нужно ответить No.

В последующем окне (Рис. 1.22) нажать OK.

14

Рис. 1.22. Настройки конфигурирования устройства

Конфигурационный файл будет привязан к ПЛИС, о чем говорит надпись с названием файла под изображением схемы (Рис. 1.23)

Рис. 1.23. Привязанный конфигурационный файл

И осталось направить это в плату, сделав двойной клик по надписи Program, слева.

Об успешной загрузке файла в отладочную плату оповестят надпись Program Succeeded в окне iMPACT (Рис. 1.24)

Рис. 1.24. Оповещение об успешном конфигурировании

И так же светодиод DONE (Рис. 1.25) на отладочной плате.

Рис. 1.25. Светодиод DONE

15

После загрузки конфигурационного файла следует проверить работоспособность программы с помощью переключателей SW0, SW1 и SW2 и светодиодов LD0 и LD1.

Повторить выполнение п.2.2.1 – п.2.2.5 лабораторной работы для своего варианта задания, создав новый проект, выполнив проектирование устройства, создав конфигурационный файл и загрузив его в ПЛИС. Для проверки работоспособности программы использовать четыре переключателя (SW0, SW1, SW2, SW3) и один светодиод (LD0). Убедиться, что работа программы соответствует заданному варианту и продемонстрировать ее преподавателю.

3. Методические указания

Любая логическая функция нескольких переменных однозначно задается в виде таблицы истинности, в левой части которой выписаны все возможные наборы значений её аргументов x1, …, xn, а правая часть представляет собой столбец значений функций, соответствующих этим наборам. Набор значений переменных, на котором функция принимает значение f = 1, называется единичным набором функции f; множество всех единичных наборов – единичным множеством функции f. Аналогично набор значений, на котором f = 0, называется нулевым набором функции f, а множество нулевых наборов

– нулевым множеством. В общем случае таблица истинности для функции от n переменных должна иметь 2n строк.

Логический элемент в электронных схемах – это устройство, реализующее ту или иную логическую функцию. При этом логические сигналы 0 и 1 задаются разными уровнями напряжения.

Логические схемы состоят из логических элементов, осуществляющих логические операции.

Логическая схема, которая полностью описывается булевыми выражениями или таблицами истинности, называется комбинационной схемой. Таким образом, комбинационная схема – схема, в которой значения входных переменных в текущий момент времени полностью определяют значения выходных переменных.

Набор логических элементов, достаточный для построения любой сколь угодно сложной логической схемы, называется функционально полным. Функционально полным является набор элементов И, ИЛИ, НЕ. Из этого набора можно исключить некоторые элементы без нарушения функциональной полноты. В частности, функционально-полным считается набор из двух элементов И и НЕ, ИЛИ и НЕ.

Синтез комбинационной логической схемы предусматривает построение структурной схемы устройства, т. е. определение состава необходимых логических элементов и соединения между ними, при которых обеспечивается преобразование входных цифровых сигналов в выходные в соответствии с заданными условиями работы устройства. В процессе синтеза обычно подразумевается необходимость минимизации затрат на реализацию устройства.

Для разработки структуры многовходовой логической схемы в заданном базисе применяют следующий алгоритм:

16

–составляется таблица истинности;

–по таблице истинности составляется булева функция в виде совершенной дизъюнктивной нормальной форме;

–используя правила булевой алгебры, карты Карно или другие способы минимизации, функция (если возможно) упрощается;

–полученное выражение приводят к заданному базису, применяя правило де Моргана. Если в качестве базы заданы элементы И-НЕ, правило де Моргана применяется к дизъюнкции, если ИЛИ-НЕ – к конъюнкции [1].

Для домашнего расчета таблица истинности строится по Таблице 1.1 следующим образом: входы Х1-Х4 одинаковы для всех вариантов, а выход Y* выбирается в соответствии с номером варианта.

Таблица 1.1 Варианты для выполнения домашнего расчета

X1 |

X2 |

X3 |

X4 |

Y1 |

Y2 |

Y3 |

Y4 |

Y5 |

Y6 |

Y7 |

Y8 |

Y9 |

Y10 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

В качестве примера расчета рассмотрите пример из раздела «Синтез логических устройств в базисах И-НЕ, ИЛИ-НЕ» [1 стр. 63-65].

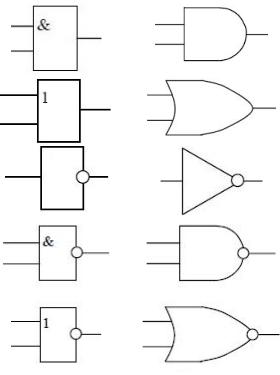

Для изображения логических схем всегда используются условные графические обозначения элементов, описывающие только выполняемую элементами функцию и не зависящие от его схемы. В настоящее время в мире существует несколько общепринятых стандартов условных обозначений. Наиболее распространенными являются американский стандарт milspec 806В и стандарт МЭК 117-15 А, созданный Международной Электротехнической Комиссией. Часто в литературе используются также обозначения в европейской системе DIN. В отечественной литературе условные обозначения элементов в основном соответствуют ГОСТ 2.743-91.

17

При выполнении домашнего задания синтезированную схему в отчете следует изобразить по ГОСТ, однако схемный ввод производится в соответствии с американским стандартом.

Таблица 2

Условное графическое обозначение логических элементов

Логический |

ГОСТ |

milspec 806В |

элемент |

|

|

И |

|

|

|

|

|

ИЛИ |

|

|

|

|

|

НЕ |

|

|

|

|

|

И-НЕ |

|

|

|

|

|

ИЛИ-НЕ |

|

|

|

|

|

4.Контрольные вопросы

1.Перечислите способы задания логических функций

2.Перечислите основные законы алгебры логики.

3.Что называют функционально полным базисом? Что называют минимальным базисом?

4.Каковы канонические формы представления логических функций?

5.Принцип построения комбинационных цифровых устройств на основе логических уравнений.

6.Для чего используется минимизация логических функций?

7.Перечислите методы минимизации логических функций и дайте их краткую характеристику.

8.Как производится синтез логических устройств в базисах И-НЕ, ИЛИ-НЕ?

9.Каковы общие свойства программируемых логических интегральных схем (ПЛИС)?

10.Перечислите основные характеристики ПЛИС.

11.Какова структура и особенности ПЛИС с архитектурой FPGA?

12.Каковы основные этапы проектирования устройств на ПЛИС?

18

13.Поясните последовательность проектирования цифровых устройств в графическом редакторе.

14.Опишите назначение основных элементов отладочного набора для ПЛИС

Xilinx Spartan.

15.Каков порядок работы с САПР ISE?

16. Какова структура и функции «Навигатора (менеджера) проектов»? 17.Поясните графический способ представления схемных решений. Каково-

назначение файла с расширением *.sch?

18.Поясните способы создания связей с выводами отладочной платы. Опишите назначение файла с расширением *.ucf.

19.Опишите назначение пакета iMPACT.

20.Каково назначение файла с расширением *.bit?

5.Литература

1.Калабеков Б. А. Цифровые устройства и микропроцессорные системы. –

М.: Радио и связь. – 2003. – С. 4-18, 34-70.

2.Сперанский B.C. Сигнальные микропроцессоры и их применение в системах телекоммуникаций и электроники. – М.: Горячая линия-Телеком, 2008. С.119-137.

3.Тарасов И.Е. Разработка цифровых устройств на базе ПЛИС Xilinx с применением языка VHDL. –М.: Горячая линия-Телеком. – 2005. – С.8-41, 63-98.

ЛАБОРАТОРНАЯ РАБОТА №2

1. Цель работы

Целью работы является изучение системы автоматизированного проектирования (САПР) Xilinx ISE WebPack, ознакомление с основами языка VHDL и реализация на ПЛИС логической схемы комбинационного типа с использованием функционала графического редактора и модулей на языке описания аппаратуры VHDL.

2.Задания для выполнения лабораторной работы

2.1Предварительная подготовка к выполнению лабораторной работы

1.Изучить описание к данной лабораторной работе и рекомендованную литературу.

2.Ознакомиться с основами языка программирования VHDL.

3.Используя сведения, полученные при подготовке, написать листинг программы, описывающей заданное устройство на языке VHDL. Данные для проектирования устройства можно получить у преподавателя или взять из Таблицы 2.1 (номер варианта уточнить у преподавателя). Из Таблицы 2.2 переписать свой вариант установки для значений переменных для выполнения симуляции.

19

4.Подготовить ответы на контрольные вопросы, приведенные в данном описании лабораторной работы.

5.Подготовить письменный отчет принятой на кафедре формы. Отчет должен содержать:

-титульный лист принятой на кафедре формы;

-номера лабораторной работы, варианта работы и формулировку цели работы;

-исходные данные выполняемого варианта;

-домашний расчет (схему, листинг программы);

-результат выполнения работы (схема, временные диаграммы);

-краткие выводы по работе.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 2.1 |

||||

|

Варианты для создания устройства demo_vhdl |

|

|

|

|

|

||||||||||||||||

№ |

|

|

|

|

|

Входы |

|

|

|

|

|

|

Выходы |

|

|

|||||||

вар. |

inp1 |

|

inp2 |

|

inp3 |

|

inp4 |

|

inp5 |

|

out1 |

|

out2 |

|

out3 |

|

|

|||||

1. |

НЕ |

|

|

ИЛИ |

|

|

И |

|

|

+ |

|

+ |

|

+ |

|

|

|

|||||

2. |

|

|

ИЛИ |

|

|

|

|

|

И-НЕ |

+ |

|

+ |

|

- |

|

|

|

|||||

3. |

|

И |

|

|

|

ИЛИ-НЕ |

|

|

+ |

|

+ |

|

- |

|

|

|

||||||

4. |

ИЛИ |

|

|

|

И |

|

|

НЕ |

+ |

|

+ |

|

+ |

|

|

|

||||||

5. |

ИЛИ |

|

НЕ |

|

|

И |

|

|

+ |

|

+ |

|

+ |

|

|

|

||||||

6. |

|

И |

|

|

|

|

ИЛИ |

|

|

+ |

|

+ |

|

- |

|

|

|

|||||

7. |

ИЛИ-НЕ |

|

|

|

И |

|

|

НЕ |

+ |

|

+ |

|

+ |

|

|

|

||||||

8. |

ИЛИ |

|

НЕ |

|

|

И-НЕ |

+ |

|

+ |

|

+ |

|

|

|

||||||||

9. |

|

И |

|

ИЛИ-НЕ |

|

|

- |

+ |

|

+ |

|

- |

|

|

|

|||||||

10. |

ИЛИ |

|

|

|

И |

|

|

- |

+ |

|

+ |

|

- |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 2.2 |

||||

|

Варианты установки значений переменных , мкс |

|

|

|

|

|

||||||||||||||||

№ |

BTN0 |

|

|

SW1 |

|

SW2 |

|

SW3 |

|

SW4 |

||||||||||||

вар. |

DC |

|

Т |

|

STO |

|

T |

STO |

|

T |

|

STO |

|

T |

|

STO |

|

|

T |

|||

1. |

50 |

5 |

|

0 |

|

5 |

0 |

|

10 |

|

0 |

|

15 |

5 |

|

20 |

||||||

2. |

50 |

10 |

|

0 |

|

10 |

0 |

|

15 |

|

0 |

|

20 |

5 |

|

25 |

||||||

3. |

50 |

20 |

|

0 |

|

15 |

0 |

|

20 |

|

0 |

|

25 |

5 |

|

5 |

||||||

4. |

25 |

5 |

|

0 |

|

20 |

0 |

|

25 |

|

0 |

|

5 |

5 |

|

10 |

||||||

5. |

25 |

10 |

|

0 |

|

25 |

0 |

|

5 |

|

0 |

|

10 |

5 |

|

15 |

||||||

6. |

25 |

20 |

|

10 |

|

5 |

10 |

|

10 |

|

0 |

|

15 |

5 |

|

20 |

||||||

7. |

20 |

5 |

|

10 |

|

10 |

10 |

|

15 |

|

0 |

|

20 |

5 |

|

25 |

||||||

8. |

20 |

10 |

|

10 |

|

15 |

10 |

|

20 |

|

0 |

|

25 |

5 |

|

5 |

||||||

9. |

20 |

20 |

|

10 |

|

20 |

10 |

|

25 |

|

0 |

|

5 |

- |

|

- |

||||||

10. |

50 |

25 |

|

10 |

|

25 |

10 |

|

5 |

|

0 |

|

10 |

- |

|

- |

||||||

Обозначения: DC – Duty Cycle; T – Period; STO – Starting Time Offset

Примечание: Для всех переключателей установить:

Cancel after Time Offset – 100мкс

20