- •Министерство цифрового развития, связи и массовых коммуникаций Российской Федерации

- •Проектирование цифрового устройства

- •Создание схемы

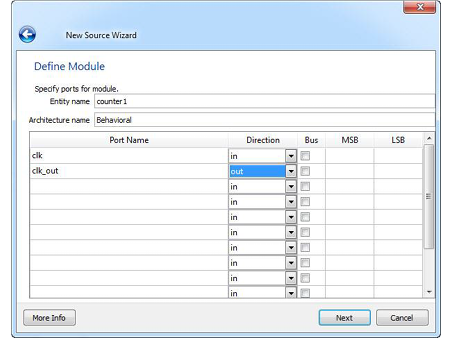

- •Настройки модуля counter 1, 2

- •Модули counter1 и counter2 на схеме

- •Настройки модуля to_leds

- •Добавление модуля to_leds на схему

- •Переименование шины

- •Двоичные вычитающие асинхронные счётчики

- •Алгоритм работы

Министерство цифрового развития, связи и массовых коммуникаций Российской Федерации

Ордена Трудового Красного Знамени федеральное государственное бюджетное образовательное учреждение высшего образования

МОСКОВСКИЙ ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ СВЯЗИ И ИНФОРМАТИКИ

(МТУСИ)

Факультет "Радио и телевидение"

Кафедра "Радиотехнические системы"

Лабораторная работа № 3

по дисциплине микропроцессорные устройства

Выполнил студент гр. БРМ1902:

Обама Х.С.

Бонсэн Й.Ф.

Проверил Д.Н.Шубин

Цель работы

Изучение системы автоматизированного проектирования (САПР) Xilinx ISE Web Pack. Изучение языка VHDL и реализация на ПЛИС цифровой схе-мы последовательного типа с использование как графического редактора и базы готовых элементов, так и модулей на языке описания аппаратуры VHDL.

Выполнение

Проектирование цифрового устройства

Модули counter1 и counter2 понижают скорость внутреннего счетчика с разной скоростью.

Мультиплексор M2_1 в зависимости от положения переключате-ля SW0 выбирает, какая скорость счетчика будет использоваться. ·

Модуль to_leds выполняет функцию бинарного счетчика, кото-рый выводит своё состояние на 8 светодиодов и при нажатии кнопки RESET на следующем такте обнуляет счетчик.

Создание схемы

Настройки модуля counter 1, 2

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

- Uncomment the following library declaration if using

- arithmetic functions with Signed or Unsigned values

--use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if instantiating

-- any Xilinx primitives in this code.

--library UNISIM;

-use UNISIM.VComponents.all;

entity counter1 is

Port ( clk : in STD_LOGIC;

clk_out : out STD_LOGIC);

end counter1;

architecture Behavioral of counter1 is

begin

process(clk) variable counter: integer := 0; variable flag: boolean := False;

begin

if clk'event and clk = '1' then

if counter = 50000000 then

counter := 0;

flag := not flag;

else

counter := counter + 1;

end if;

if flag = True then

clk_out <= '1';

else

clk_out <= '0';

end if;

end if;

end process;

end Behavioral;

Для модуля counter2 текст программы выглядит так же кроме этой строки

if counter = 25000000 then

Модули counter1 и counter2 на схеме

Настройки модуля to_leds

Область объявления портов бу-дет выглядетьтак:

entity to_leds is

Port ( clk : in STD_LOGIC;

btn_res : in STD_LOGIC;

led : out STD_LOGIC_VECTOR (7 downto 0));

end to_leds;

Следующий немаловажный шаг – добавление библиотек. В этом модуле потребуются дополнительные библиотеки, и верхняя область файла будет иметь следующий вид:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

И основная часть кода:

process(clk, btn_res)

variable cnt: STD_LOGIC_VECTOR (7 downto 0) := "00000000"; -- 8-битная

-- переменная счетчика

begin

if clk'event and clk = '1' then -- На переднем фронте сигнала

if cnt = (cnt'range => '1') or btn_res = '0' then -Если значение -- счетчик 11111111 или кнопка в состояние 0

cnt := "00000000"; -- Сбросить счетчик else -- Если нет, то

cnt := cnt + 1; -- Увеличение счетчика на 1

end if;

led <= cnt; -- Вывод на светодиоды состояние счетчика

end if;

end process;

Примечание: строка btn_res = '0' может показаться необычной, так как в обычном состоянии не нажатая кнопка выдает 0, а нажатая 1. Но в данной работе используется кнопка RESET на плате, значения которой инвертиро-ваны.