VHDL lection

.pdf

Основы VHDL

Основы VHDL

вторникник,, 2424 ноябряноября 20092009 гг..

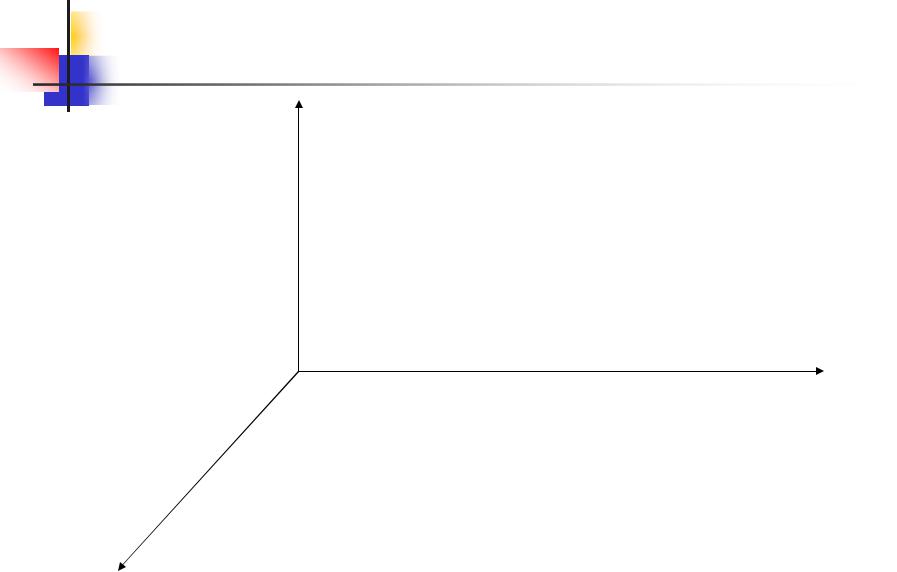

Уровни описания РЭА

Уровни описания РЭА

системный уровень

уровень вычислительных процессов

функционально-логический уровень

схемотехнический уровень

компонентный уровень

Функционально-логический уровеньровень

подуровень функционирования ЭВМ

подуровень устройств (узлов) ЭВМ

регистровый подуровень

вентильный уровень

Требования к HDL

Требования к HDL

стандартность;

многоаспектность и иерархичность;

пригодность для восприятия человеком и обработки на ЭВМ.

Аспекты описания РЭА

Аспекты описания РЭА

функциональный (реализуемая функция, алгоритм)

временной (задержки, время отклика)

структурный (типы и связи компонент)

ресурсный (число вентилей, площадь кристалла)

надёжностный (время наработки на отказ)

конструктивный (вес, габариты)

стоимостной и т.д.

Степень детализации аспектовпектов

Степень детализации аспектовпектов

Поведение

Команды

Алгоритмы устройств

Микрооперации

Булевы функции

Фронты сигналов

Микротакты

Такты

Переключатели |

Вентили |

узлы Базовые |

Регистры |

Микросхемы |

Устройства |

ВС и ЭВМ |

Структура

Время

HDL как язык программированиявания

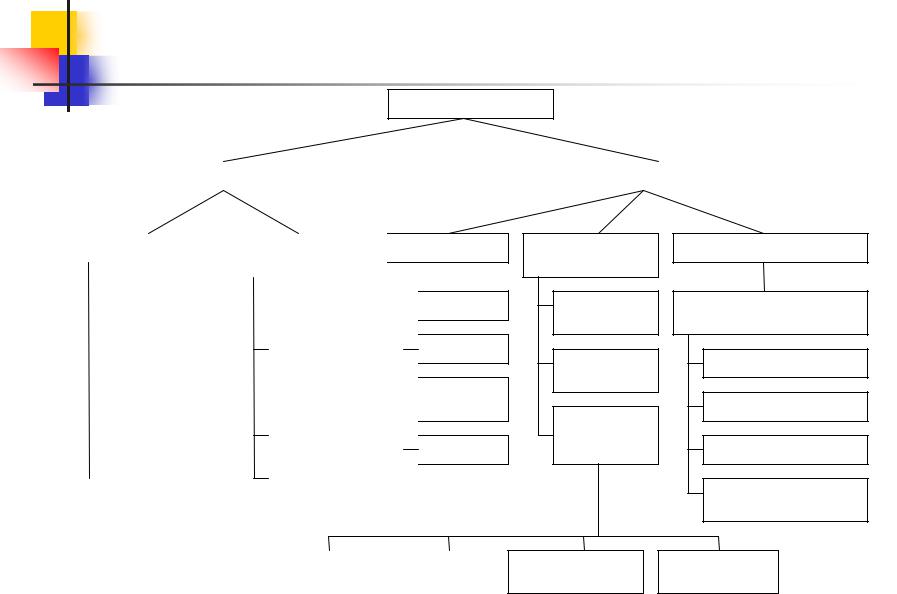

Компоненты VHDL

Общеалгоритмический компонент |

|

Проблемно-ориентированный компонент |

|

|

|

|

|

Типы данных |

|

|

Последовательные |

|

|

Типы данных |

|||||

|

|

|

|

|

|

|

|

операторы |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

Целые |

|

|

|

Присваивание |

|

|

|

Физические |

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

Действительные |

|

|

|

Условие |

|

|

|

Логические |

|||

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

Символьные |

|

|

|

Выбор |

|

|

|

Ограниченные |

||

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

Перечислимые |

|

|

|

Повторение |

|

|

|

Подтипы |

||

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

Агрегаты |

|

|

|

Вызов |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

подпрограмм |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

Массивы, строки |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Записи |

|

Параллельные |

|

|

|

Оператор |

|

||

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

операторы |

|

|

|

process |

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Описание поведения во времени

Категория signal

Представление

задержек

Представление

параллельных

процессов

Охраняемые блоки и выражения

Структурное описание

Структурное архитектурное тело

Описание вхождений

Описание конфигураций

Параметры настройки

Оператор условной генерации

Операторы ожидания событий

VHDL

VHDL

Языки описания аппаратуры (Hardware Descriptionn LanguageLanguage,,

HDL) позволяют описывать блоки в первую очередь на функциональнологическом уровне, наибольшее распространение имеют на регистровом и вентильном подуровнях и при описании узлов ЭВМ. Проекты на языках HDL могут быть использованы и для решения задач системного уровня проектирования. Кроме того, специальные расширения, например, VHDL-AMS могут рассматриваться как промежуточный подуровень описания между вентильным подуровнем функциональнологического уровня и схемотехническим уровнем, что даёт возможность моделировать не только цифровую, но и аналоговую аппаратуру.

Язык VHDL (Very high speed integrated circuit Hardware DescriptionDescription

Language — язык описания сверхскоростных БИС) был разработан международной группой по заданию Министерства обороны США в начале 80-х годов с целью обеспечения единообразного понимания подсистем различными проектными группами.

Структура проекта

Структура проекта

Проект в системе проектирования на основе VHDL представляется совокупностью иерархически связанных текстовых фрагментов, называемых проектными модулями. Различают первичные и вторичные проектные модули, при этом:

<первичный модуль>::= <декларация сущности> | <декларация пакета>

| <декларация конфигурации>

<Вторичный модуль>::= <архитектурное тело> | <тело пакета>

Сущности и архитектурыры

Сущности и архитектурыры

Декларация сущности (entity) определяет имя проекта и его интерфейс, т.е. порты и параметры настройки.

Архитектурное тело сущности описывает тем или иным образом функционирование устройства и (или) его структуру.

Каждой сущности сопоставляется одно или несколько архитектурных тел. Несколько вторичных модулей, соответствующих одному первичному, составляют набор возможных альтернативных реализаций объекта, представленного первичным модулем.

Например, одной сущности может соответствовать несколько архитектурных тел, отличающихся степенью детализации описания и даже алгоритмом преобразования данных.