- •Глава 3. Однокристальные микроконтроллеры семейства mcs51

- •Микропроцессоры и микроконтроллеры

- •Микроконтроллеры семейства mcs51

- •А. Общие характеристики и назначение выводов

- •Б. Организация памятимикроконтроллера

- •В. Таймеры-счетчики мк

- •Г. Приемо-передатчик

- •Д. Системапрерываний микроконтроллера

- •Е. Системакоманд мк

- •3.3. Супервизорные схемы

Б. Организация памятимикроконтроллера

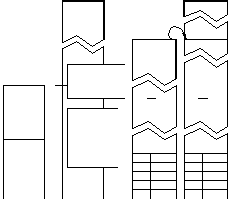

Микроконтроллер максимально в своем составе имеет четыре зоны памяти (рис. 3.4):

-

резидентную память про-

FFh

100h

FFh

FFFFh FFFFh

PC>FFFh

0FFFh 0FFFh

По всей зоне

MOVX A,@DPTR

MOVX @DPTR,A

грамм объемом 4кБ;

- резидентную память данных объемом 256 байт, из которых младшие 128 байт доступны пользователю как операнды, в старших адресах резидентного ОЗУ располо- жены регистры специальныхфункций, управляющие ре-

SFR

80h 7Fh

Резидентная память данных

до FFH MOVX A,@R0 MOVX A,@R1

MOVX @R0,A MOVX @R1,A

EA=1

Векторы прерыв.

23h T1+R1

1Bh TF1

EA=0

Векторы прерыв.

23h T1+R1

1Bh TF1

сурсами МК (см. табл. 3.2);

внешнюю память про- грамм объемом до 64кБ;

внешнюю память дан- ных объемом до 64кБ.

Резидентная опера- тивная память. Составляет

РПД

13h 0Bh 03h

IE1 TF0 IE0

13h 0Bh 03h

IE1 TF0 IE0

256 байт и делится на две

равные по объему зоны: па- мять пользователя или рези-

Резидентная

Внешняя

Резидентная Внешняя

дентная память данных с

оперативная

память память память

адресами от нуля до 7Fh и

память

данных

программ

программ

РОП

ВПД

РПП ВПП

зону регистров специальных

Рис. 3.4. Организация памяти

функций (SFR), обзор кото-

рых

приведен

в табл.

3.2

–

3.5. В первых 32-х байтах резидентной памяти данных расположены 4-е банка регист- ров общего назначения по восемь регистров R0…R7 в каждом. Выбор того или иного банкаосуществляетсяустановкой специальныхбитов врегистреPSW (см. табл. 3.4).

В резидентной памяти данных доступны различные комбинации подразумевае- мой (MOV R2,A; переслать из аккумулятора в Rn), непосредственной (MOV A,#data; переслать константу #data аккумулятор) , прямой (MOV adr1,adr2; переслать из ячейки adr1 в adr2)и косвенной адресации через регистры R0 и R1 (MOV @R0,A; переслать из аккумулятора в ячейку, адрес которой в R0). Подробно различные способы адресации приведенны в разделе 3.2.Ж. ВзонеSFR доступна только прямаяадресация.

В резидентном ОЗУ размещен и стек МК. По умолчанию после сброса указатель стека принимает значение 07h и программно может быть установлен на любую зону младших 128 байт (0…07Fh).

Особый интерес представляет зона резидентной памяти данных из шестнадцати ячеек (байт) от 20h до 2Fh. Это зона так называемого битового процессора. Содержа- щиеся здесь 128 бит допускают отдельную адресацию. В системе команд МК преду- смотрены специальные команды битового процессора. Они позволяют устанавливать и сбрасывать отдельные биты, проверять различные условия и делать переходы (см. 3.2.Ж). Это очень удобно при написании управляющихпрограмм.

В верхних 128 байтах расположены регистры специальных функций RSF, управ- ляющие ресурсами МК. Они были кратко рассмотрены в предыдущем разделе (см. табл. 3.2) и будут по мере надобности рассматриваться более подробно далее. Отдельные ре- гистры этой группы также имеют побитную адресацию, что позволяет эффективно управлять ресурсами.

Значения адресов битов резидентной памяти данных приведены в таблице 3.7.

Таблица 3.7.

|

Адрес байта |

старший бит D7 |

|

|

|

|

младший бит D0 | ||

|

2Fh |

7F |

7Е |

7D |

7С |

7В |

7А |

79 |

78 |

|

2Еh |

77 |

76 |

75 |

74 |

73 |

72 |

71 |

70 |

|

2Dh |

6F |

6Е |

6D |

6С |

6В |

6А |

69 |

68 |

|

2Сh |

67 |

66 |

65 |

64 |

63 |

62 |

61 |

60 |

|

2Вh |

5F |

5Е |

5D |

5С |

5В |

5А |

59 |

58 |

|

2Аh |

57 |

56 |

55 |

54 |

53 |

52 |

51 |

50 |

|

29h |

4F |

4Е |

4D |

4С |

4В |

4А |

49 |

48 |

|

28h |

47 |

46 |

45 |

44 |

43 |

42 |

41 |

40 |

|

27h |

3F |

ЗЕ |

3D |

ЗС |

ЗВ |

ЗА |

39 |

38 |

|

26h |

37 |

36 |

35 |

34 |

33 |

32 |

31 |

30 |

|

25h |

2F |

2Е |

2D |

2С |

2В |

2А |

29 |

28 |

|

24h |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

|

23h |

IF |

IE |

ID |

1С |

1В |

1А |

19 |

18 |

|

22h |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

|

21h |

0F |

0Е |

0D |

0С |

0В |

0А |

09 |

08 |

|

20h |

07 |

06 |

05 |

04 |

03 |

02 |

01 |

00 |

|

1Fh 18h |

БАНК_3 | |||||||

|

17h 10h |

БАНК_2 | |||||||

|

0Fh 08h |

БАНК_1 | |||||||

|

07h 00h |

БАНК_0 | |||||||

Значения адресов адресуемых битов зоны регистров специальных функций RSF

приведены втаблице3.8.

Таблица 3.8.

|

Адрес байта |

старший бит D7 |

|

младший бит D0 |

Регистр | ||||||

|

0F0H |

F7 |

F6 |

F5 |

F4 |

F3 |

F2 |

F1 |

F0 |

B | |

|

0Е0Н |

E7 |

E6 |

E5 |

E4 |

E3 |

E2 |

E1 |

E0 |

ACC | |

|

0D0H |

CY AC F0 RS1 RS0 |

OV |

- |

P |

PSW | |||||

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 | |||

|

0B8Н |

- - PT2 PS PT1 |

PX1 |

PT0 |

PX0 |

IP | |||||

|

- |

- |

BD |

BC |

BB |

BA |

B9 |

B8 | |||

|

0B0H |

B7 |

B6 |

B5 |

B4 |

B3 |

B2 |

B1 |

B0 |

P3 | |

|

0A8H |

EA |

- - ES ET1 |

EX1 |

ET0 |

EX0 |

IE | ||||

|

47 |

46 |

45 |

44 |

43 |

42 |

41 |

40 | |||

|

0A0Н |

A7 |

A6 |

A5 |

A4 |

A3 |

A2 |

A1 |

A0 |

P2 | |

|

098Н |

SM0 |

SM1 SM2 REN TB8 |

RB8 |

TI |

RI |

SCON | ||||

|

9F |

9Е |

9D |

9С |

9В |

9А |

99 |

98 | |||

|

090Н |

97 |

96 |

95 |

94 |

93 |

92 |

91 |

90 |

P1 | |

|

088H |

TF1 |

TR1 TE0 |

TR0 |

IE1 |

IT1 |

IE0 |

IT0 |

TCON | ||

|

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 | |||

|

080Н |

87 |

86 |

85 |

84 |

83 |

82 |

81 |

80 |

P0 | |

Резидентная память программ размещена на кристалле, имеет объем 4 кБ и предназначена для хранения кодов программ. Она может быть запрограммирована при изготовлении (масочное ПЗУ), у пользователя (РПЗУ с ультрафиолетовым стиранием) или совсем отсутствовать в зависимости от исполнения МК. Следует отметить, что объ- ем резидентной памяти программ у современных МК достигает десятков килобайт, па- мятьс УФ стиранием всешире вытесняется флешпамятью.

Начинается память программ с нулевой ячейки. После сброса микроконтроллера

в счетчике команд устанавливается нуль и он считывает код нулевой ячейки, по ней оп- ределяет длину команды, считывает ее и выполняет предписанную инструкцию. Обыч- но здесь располагается команда безусловного перехода на начало исполняемой про- граммы LJMP <Адрес программы>.

Начиная с ячейки 3h до 23h, расположены векторы прерываний. На каждый век- тор отведено 8 байт. В них располагают команды перехода в подпрограмму обработки соответствующего прерывания. Источники прерываний по каждому из векторов приве- дены в таблице 3.9.

Таблица 3.9.

|

Источник прерывания |

Вектор |

|

Внешнее прерывание INT0 |

0003h |

|

Таймер/счетчик Т/С 0 |

000Bh |

|

Внешнее прерывание INT1 |

0013 h |

|

Таймер/счетчик Т/С 1 |

001Вh |

|

Последовательный порт |

0023h |

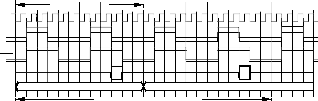

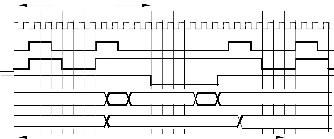

На рис. 3.5 представлен цикл работы с резидентной памятью программ и рези- дентной памяти данных при проведении операций, в которых нет обращения к внешней памяти данных, например, арифметико-логических, передачи управления или записи в порт или чтения с выводов, либо защелок порта.

Машинный

цикл

S1 S2 S3

S4 S5 S6

S1 S2

S3 S4

S5 S6 S1 S2

BQ P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

ALE

PME

Р0,

Р1,

Р2,

Р3.

Din Din

Старые данные на выводе Новые данные на выводе

Команда MOV Порт, Источник

Рис. 3.5. Работа с внутренней памятью программ и внутренней памятью данных

Считы- вание с выводов порта.

Запись в порт

Машинный цикл выполнения команды состоит из шести шагов, а каждый шаг включает два такта внутреннего генератора. Если подключен кварцевый резонатор на номинальную частоту в 12 МГц, то машинный цикл длится одну микросекунду. В каж- дом цикле дважды активизируются выводы ALE и PME, хотя для выполнения перечис- ленных ранее команд (инструкций) нужды в этом нет. Считывание информации с выво- да порта или защелки осуществляется во второй половине шестого шага, команда счи- тывания длится один машинный цикл. Команда записи в порт длится два машинных цикла, новые данные навыводах появляются в начале второго циклакоманды.

Внешняя память программ имеет адресное пространство до 64 кбайт. Она так- же предназначена для хранения программ и в процессе работы МК доступна только для чтения. Обращение к внешней памяти программ осуществляется, если на вывод ЕА` (External Address) подан ноль, или, если содержимое счетчика программ превышает ад- рес в 4кБ (0FFFh, см. рис. 3.4). Здесь, по тем же адресам, что и у резидентной памяти расположены векторы прерываний (см. табл. 3.9). Пользователь может комбинировать внешнюю и резидентную память программ в зоне до 4кБ, управляя выводом ЕА` через один из выводов первого порта микроконтроллера, поскольку нулевой и второй порты используютсяпри чтенииинструкцийиз внешнейпамятипрограмм.

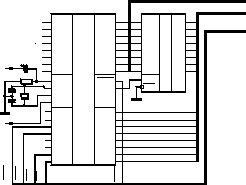

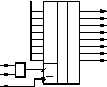

Аппаратная организация внешней шины МК для подключения памяти программ и памяти данных, о которой будет рассказано позже, приведено нарис. 3.6.

+5B C3

P1.0 MC P1.1 P1.2 P1.3

P1.4 P1.5 P1.6

P0.0

D0

P0.1

D1

P0.2

D2

P0.3

D3

P0.4

D4

P0.5

D5

P0.6

D6

D0 Di0 D1 Di1 D2 Di2 D3 Di3 D4 Di4 D5 Di5 D6 Di6

RGDI0 А0

DI1 А1 DI2 А2 DI3 А3 DI4 А4 DI5 А5 DI6 А6

Шина данных

Шина

адресов

Шина управления

C1, C2 - 30pF C3 - 10mkF R1 - 8,2K

P1.7

P0.7 D7 D7 Di7

DI7 А7

R1

C1 BQ

C2

RST BQ2 BQ1

EA P3.0

INT0 INT1 WR

RD

PME ALE

P2.0

STB OE

А8

+5B или 0В

P3.1 P3.2 P3.3 P3.4 P3.5 P3.6 P3.7

P2.1 P2.2 P2.3 P2.4 P2.5 P2.6 P2.7

А9

А10 А11 А12 А13 А14 А15

Рис. 3.6. Организация внешней шины.

PME

Частота работы МК определяется кварцевым резонатором BQ, подключенным к выводам BQ1 и BQ2. Конденсатор С3 с резистором R1 обеспечивают автоматический сброс МК при включении питания. Поскольку исходно конденсатор не заряжен, при включении питания на вывод RST подается сигнал логической единицы, спадающий до нуля при заряде конденсатора через резистор R1. Постоянная времени RС –цепочки выбрана так, чтобы обеспечить надежный сброс МК. К соответствующим выводам пор- та Р3 подключена линия управления, передающая сигналы чтения и записи во внеш- нюю память данных RD`и WR`, сигнал выборки из внешней памяти программ РМЕ` и два внешних прерывания INT0`, INT1`. Шина адресов формируется портами Р0 и Р2. Младшая часть адреса передается через порт Р0 и фиксируется в регистре защелке RG c помощью сигнала фиксации младшей части адреса, передаваемого выводом ALE. Для этих целей подойдет любой статический регистр, например, рассмотренный нами ранее ИР22. Старшая часть адреса передается через специализированный под эту опе- рацию порт Р2. Данные передаются ичитаются из МКчерез портР0.

На

рис.

3.7.

представлено

подключение

к внешней

шине

схе-

AO D0

|

|

AO |

PROM |

D0 |

|

|

A1 |

D1 | |||

|

A1 |

D1 | |||

|

A2 |

D2 | |||

|

A2 |

D2 | |||

|

A3 |

D3 | |||

|

A3 |

D3 | |||

|

A4 |

D4 | |||

|

A4 |

D4 | |||

|

A5 |

D5 | |||

|

A5 |

D5 | |||

|

A6 |

D6 | |||

|

A6 |

D6 | |||

|

A7 |

D7 | |||

|

A7 |

D7 | |||

|

A8 |

| |||

|

A8 |

| |||

|

A9 | ||||

|

A9 | ||||

|

A10 | ||||

|

A10 | ||||

|

A11 | ||||

|

A11 | ||||

|

A12 | ||||

|

A12 | ||||

|

ME | ||||

|

OE Upr CS | ||||

|

5B | ||||

|

| ||||

|

|

P

+

мы РПЗУ. Никакой дополнительной логики для этого не требуется. Вывод CS микросхемы подключается или к земле, если микросхема РПЗУ одна. В противном случае нужно использовать дешифратор адреса ДША, выбирающий нужную микросхему из массива памяти. Позже мы познакомимся с разработкой таких устройств.

Цикл обращения к внешней памяти программ при чтении из нее управляющих инструкций без обращения к внешней памяти дан- ных приведен на рис. 3.8. В первом шаге каждого машинного цикла по порту Р0 считывается инструкция (inC) и затем на него выстав- ляется младшая часть адресаследующей (PCL). При этом становит-

к ДША

Рис. 3.7.

ся активным сигнал ALE и по его спаду фиксируется в регистре за- щелке (рис. 3.6). Старшая часть адреса(PCН) передается через порт Р2 и во внешней фиксации не нуждается.

Затем считывается следующая инструкция и так далее. За машинный цикл считывается два байта команд. Параллельно идет и выполнение. Если команда однобайтовая, лишние считанные коды игнорируются и вводятся сновав очередном машинномцикле.

Машинный

цикл

S1 S2 S3 S4

S5 S6

S1 S2

S3 S4

S5 S6 S1 S2

BQ P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

ALE

PME

|

P0 inC |

PCL |

|

inC |

PCL |

|

inC |

PCL |

|

inC |

PCL |

|

inC |

PCL |

|

P2 |

|

PCH |

|

|

PCH |

|

|

PCH |

|

|

PCH |

|

PCH |

Рис. 3.8. Работа с внешней памятью программ без обращения к внешней памяти данных

Из циклограммы видно, что при подключении внешней памяти программ, ис- пользовать порты Р0 и Р2 для ввода-вывода как порты общего назначения не удастся, поскольку они практически полностью заняты обслуживанием шины.

Внешняя память данных адресуется 16-и разрядным адресом и может составлять до 64 кБ (рис. 3.4). В этой зоне доступна только косвенная адресация. В зоне до 255 байт она возможна через регистры R0 и R1, по всей памяти применимы команды:

MOVX A,@DPTR ;записать в аккумулятор содержимое ячейки, адрес которой

;содержится в регистре указателе данных DPTR

MOVX @DPTR,A ;записать в ячейку, адрес которой содержится в регистре

;указателе данных DPTR, содержимое аккумулятора.

Обращение

к внешней

памяти

программ

осуществляет-

AO D0

|

|

AO |

RAM |

D0 |

|

|

A1 |

D1 | |||

|

A1 |

D1 | |||

|

A2 |

D2 | |||

|

A2 |

D2 | |||

|

A3 |

D3 | |||

|

A3 A4 |

D3 D4 | |||

|

A4 |

D4 | |||

|

A5 |

D5 | |||

|

A5 |

D5 | |||

|

A6 |

D6 | |||

|

A6 |

D6 | |||

|

A7 |

D7 | |||

|

A7 |

D7 | |||

|

A8 |

| |||

|

A8 |

| |||

|

A9 | ||||

|

A9 | ||||

|

A10 | ||||

|

A10 | ||||

|

A11 | ||||

|

A11 | ||||

|

A12 | ||||

|

A12 | ||||

|

D | ||||

|

OE W/R CS | ||||

|

R | ||||

|

| ||||

|

|

R

W

к

ДША

ся через внешнюю шину, формируемую портами Р0 и Р2 (см. рис. 3.6). Аппаратное подключение схем ОЗУ внешней памяти программ показано на рис. 3.9. Видно, что никакой дополни- тельной логики для подключения типовой схемы статического ОЗУ не требуется. Потребуется лишь дешифратор адреса, если подключаемых схем в массиве внешней памяти данных более одной.

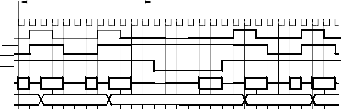

На рис. 3.10. показана циклограмма работы с внешней памятью данных при чтении инструкций из резидентной памя- ти программ. Команда MOVX длится два машинных цикла, причем, во втором цикле формируется сигнал на линии чтения или записи и периодичность сигналов ALE и PME нарушается. Данные, выставляются из МК на шину данных при записи в

последней трети сигнала WR. При реализации операции чтения из внешней памяти, схе- ма ОЗУ обязана выставить информацию на шину также к последней трети сигнала RD, посколькуименно вэто время данныефиксируются микроконтроллером черезпорт Р0.

Машинный

цикл

S1 S2

S3 S4

S5 S6

S1 S2 S3

S4 S5

S6 S1 S2

BQ P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

ALE

PM E

WR RD

P0

Состояние защелок

A0-7

Состояние защелок

Dout Din

Состояние защелок

P2 Состояние защелок

A8-15

Команда записи - чтения

Состояние защ елок

Рис. 3.10. Работа с внутренней памятью программ с обращ ением к внешней памяти данных

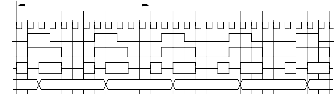

На рис. 3.11. показанациклограмма обращенияквнешней памятиданных при чтении инструкций извнешней памяти программ. Как видно из рисунка, и в этом слу- чае нарушается периодичность сигналов ALE и PME порты Р0 и Р2 использовать в ка- честве портов ввода-вывода общего назначения нельзя.

Машинный

цикл

S1 S2 S3 S4

S5 S6

S1 S2

S3 S4

S5 S6 S1 S2

BQ P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

P1 P2

ALE

PME WR RD

P0

inC PCL

inC

A0-7

Dout Din

PCL inC PCL

P2 PCH A8-15 PCH PCH

Рис. 3.11. Работа с внешней памятью программ с обращением к внешней памяти данных

На

рис.

3.12

показано

подключение

к внешней

D0 DI0 RG DI0 D1

шине регистра, служащего для выдачи сигналов дис-

D2 D3 D4 D5 D6

D7

DI1

DI2 DI3 DI4 DI5 DI6

DI1

DI2 DI3 DI4 DI5 DI6

кретного управления. Этот регистр будет иметь неко-

торый адрес или зону адресов в адресном простран- стве внешних данных. Для активации регистра необ- ходим дешифратор адреса, выделяющий его при про-

WR

К объектам управления

к ДША 1

Разрешение

DI7 DI7

STB OE

ведении операций чтения-записивовнешнююпамять

MOVX. Сигнал разрешения, подаваемый на вывод

ОЕ` запрещает выдачу сигналов с регистра сразу по- сле включения микроконтроллера. После включения

Рис. 3.12. Регистр для выдачи

сигналов дискретного управления

питания содержимое регистра неопределенно. Если подключить его вывод ОЕ` к порту общего назначе- ния Р1, то все биты этого порта при сбросе МК будут на

К объектам контроля

RD

к ДША 1

in BF out D0

1 1

2 2 D1

3 3 D2

4 4 D3

OE

1 1 D4

2 2 D5

3 3 D6

4 4 D7

OE

высоком уровне и содержимое регистра на объект вы- ставлено не будет. Выводы регистра будут в Z- состоянии. После завершения программы установки на- чального состояния объекта управления, соответствую- щий бит порта Р1 можно обнулить и выдать содержимое регистра на объект управления. По циклограмме записи во внешнюю память убедитесь в правильности функцио- нирования предложенного динамического регистра.

Рис. 3.13. Буфер для приема сигналов дискретного контроля

Для проведения сигналов дискретного контроля, помимо свободных портов ввода-вывода МК, можно ис-

пользовать подключенные к внешней шине буферы

A MS

A14 0

A13 0 1

A12 1 2

2 3

A15 V 4

RD 5

WR 1 6

7

8XXXh

9XXXh AXXXh BXXXh CXXXh DXXXh EXXXh FXXXh

(рис. 3.13). При проведении операции чтения из внеш- ней памяти данных буфер подключит датчики объекта управления к шине и содержимое сразу восьми линий будетсчитано в МК.

Здесь также необходим дешифратор, активизи- рующий выводыОЕ` буфера.

К буферам и регистрам

Рис. 3.14. Простейший дешифратор адреса

Устройство такого дешифратора приведено на

рис. 3.14. За основу взят уже знакомый нам дешифра- тор ИД7 3х8. Дешифратор реализует неполную дешиф- рацию, выделяя каждому регистру или буферу не один,

а целую группу адресов. Это конечно не экономно с точки зрения расходования адрес- ного пространства, но вполне приемлемо для локальных контроллеров. Здесь мы под 8 регистров или буферов использовали старшие 32 кБ адресов внешней памяти данных и можем проводить до 64 ДУ или ДК, что для локального контроллера более чем доста- точно, как, скорее всего будет и достаточно оставшихся младших 32 кБ адресов. Пред- ложенный дешифратор уже стробируется сигналами чтения и записи, поэтому ячейки ИЛИ на рис. 3.13 и 3.12 можно (и лучше) исключить и сигнал с дешифратора подавать непосредственно на входы синхронизации регистров или разрешения выдачи буферов. Так задержка сигнала будет короче. Умейте оценивать эти задержки. Здесь нужно про- верить, когда сработает дешифратор и подаст сигнал на буфер или регистр. В парамет- рах каждой микросхемы бываетприведено время задержки сигнала tзад. Суммарное время задержки будет складываться из задержки ячейки ИЛИ дешифратора (рис. 3.14), задержки самого дешифратора 1533ИД7 и задержки открытия буфера и составит в сумме около 40мкс. Это составит не более одного такта при частоте 12 МГц и с хоро- шим запасом допустимо относительно появления данных при записи или чтении (см. рис. 3.10, 3.11) как при работе с резидентной или внешней памяти программ.