3510

.pdf

out1_de := in_rsvd; WHEN "01" =>

out2_de := in_rsvd; WHEN "10" =>

out3_de := in_rsvd; WHEN "11" =>

out4_de := in_rsvd; WHEN OTHERS =>

NULL; END CASE;

END IF;

c_uint := out1_de OR L_1; out1 <= c_uint;

b_c_uint := out2_de OR R_0; out2 <= b_c_uint;

c_c_uint := out3_de OR L_3; out3 <= c_c_uint;

d_c_uint := out4_de OR R_2; out4 <= d_c_uint;

END PROCESS demux; END rtl;

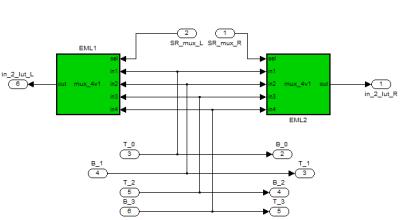

Рис.3.29. Соединительный блок С1. Подключение МС из вертикального трассировочного канала ко второму входу LUT-

таблицы (in_2_lut_l или in_2_lut_r)

161

Рис.3.30. Маршрутизатор трассировочных ресурсов

Пример 5. M-файл мультиплексора 4 в 1 входящего в состав

соединительного блока C1

function out = mux_4v1(sel, in1, in2, in3, in4)

hdl_fm = fimath(...

'RoundMode', 'floor',...

'OverflowMode', 'wrap',...

'ProductMode', 'FullPrecision', 'ProductWordLength', 32,...

'SumMode', 'FullPrecision', 'SumWordLength', 32,...

'CastBeforeSum', true);

out = fi(0, 0, 1, 0, hdl_fm); switch (uint8(sel))

case 0,

162

out = fi(in1, 0, 1, 0, hdl_fm); case 1,

out = fi(in2, 0, 1, 0, hdl_fm); case 2,

out = fi(in3, 0, 1, 0, hdl_fm); case 3,

out = fi(in4, 0, 1, 0, hdl_fm);

end

Пример.6. Код языка VHDL дешифратора 5 в 1 используемого в маршрутизаторе

LIBRARY ieee;

USE ieee.std_logic_1164.all; USE ieee.numeric_std.all; ENTITY EML1_block IS

PORT (

sel : IN std_logic_vector(2 DOWNTO 0); in1 : IN std_logic;

in2 : IN std_logic; in3 : IN std_logic; in4 : IN std_logic; in5 : IN std_logic;

out_rsvd : OUT std_logic); END EML1_block;

ARCHITECTURE rtl OF EML1_block IS

BEGIN

EML1_block : PROCESS (sel, in1, in2, in3, in4, in5) BEGIN

out_rsvd <= '0'; CASE sel IS

WHEN "000" => out_rsvd <= in1;

WHEN "001" => out_rsvd <= in2;

WHEN "010" =>

163

out_rsvd <= in3; WHEN "011" =>

out_rsvd <= in4; WHEN "100" =>

out_rsvd <= in5; WHEN OTHERS =>

NULL; END CASE;

END PROCESS EML1_block; END rtl;

Продемонстрирована возможность использования системы визуально-иммитационного моделирования

Matlab/Simulink с приложением Simulink HDL Coder для разработки архитектуры академической ПЛИС типа ППВМ с одноуровневой структурой межсоединений и технологией соединений single-driver на уровне системы. Разработанная архитектура ПЛИС обеспечивает однотипность трассировочность ресурсов по всей площади кристалла.

164

4. ПРОЕКТИРОВАНИЕ МИКРОПРОЦЕССОРНЫХ ЯДЕР ДЛЯ РЕАЛИЗАЦИИ В БАЗИСЕ ПЛИС

4.1.Проектирование учебного процессора для реализации

вбазисе ПЛИС с помощью конечного автомата

Микропроцессорные ядра представляют важный класс вычислительных заготовок, так как от их качеств, в основном, зависят основные технические и потребительские свойства систем на кристалле. Эти заготовки различаются по степени гибкости настройки под условия потребителя как программные (―мягкие‖ описанные на языке HDL), жесткие (логическая схема) и аппаратные (―твердые‖ маски под определенную технологию). Программные заготовки можно легко подстраивать к условиям нового проекта, обладают высоким быстродействием и они независимы от технологии. Их реализация в ПЛИС (например, 8-разрядное микропроцессорное ядро PicoBlaze для реализации в базисе ПЛИС семейств Spartan и Virtex) позволяет ускорить процесс разработки микропроцессорных систем. Наиболее важными потребительскими свойствами вычислительных заготовок процессоров являются: повторяемость, быстрoдействие, аппаратурные затраты.

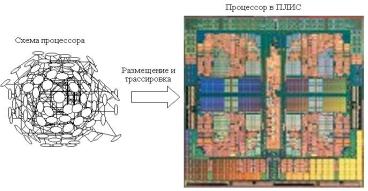

Путем несложной перенастройки ―мягкой‖ заготовки можно получить ряд модификаций микроконтроллера с различным сочетанием объема памяти, периферийных устройств, источников прерывания и т.п. Такой процессор можно реализовать в ПЛИС различных фирм. Опиcание модели на VHDL позволяет не только сделать ее перенастраиваемой и независимой от технологии, но и выполнять ее моделирование и синтез на симуляторах и средствах синтеза различных фирм. На рис.4.1 показано отображение процессора в ПЛИС.

165

Рис.4.1. Отображение схемы процессора в базисе ПЛИС

Рассмотрим систему команд синхронного процессора, реализованного с помощью конечного автомата, с циклом работы в два такта. При разработке системы команд процессора, используется слабое кодирование. В табл.4.1 представлена система команд процессора с синхронной архитектурой.

Процессор способен работать с синхронным ОЗУ. Это обеспечивается использованием оператора case, который используется в ветви оператора if при детектировании атрибута переднего фронта синхроимпульса clk и позволяет организовать цикл работы в два такта.

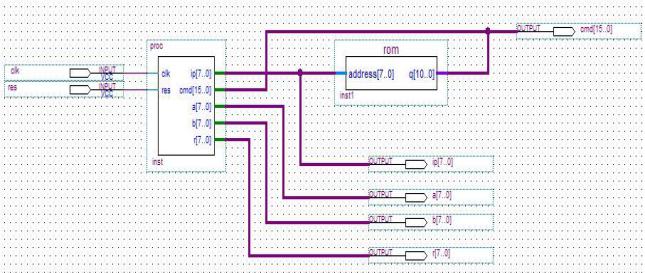

Реализуем процессор в ПЛИС фирмы Altera APEX20KE как с асинхронным ПЗУ (мегафункция LPM_ROM). На рис.4.2 показана тестовая схема управляющего автомата процессора в графическом редакторе САПР ПЛИС Quartus II версии 2.0. На рис.4.3 показано содержимое конфигурационного файла ПЗУ.

В описание процессора на языке VHDL добавлен асинхронный сброс регистров А, В и счетчика команд на регистре ip (врезка 1). Декодирование переменной-селектора cmd осуществляется с помощью оператора case. Оператор преобразования типов conv_integer(cmd) переводит вектор в десятичное число отдельных кодов.

166

167

Рис.4.2. Тестовая схема микропроцессорного ядра в графическом редакторе САПР ПЛИС Quartus II версии 2.0 с использованием управляющего автомата с циклом работы в два такта на языке VHDL и асинхронного ПЗУ (мегафункция LPM_ROM)

Таблица 4.1 Система команд процессора с синхронной архитектурой

Код операции |

Мнемоника |

|

Описание |

|

|

|

0 |

NOP |

Нет операции |

|

|

|

|

01xxH |

JMP |

Безусловный переход по адресу, |

||||

|

|

заданному |

младшим |

байтом |

||

|

|

команды |

|

|

|

|

02xxH |

JMPZ |

Переход по адресу, заданному |

||||

|

|

младшим байтом команды, если |

||||

|

|

содержимое регистра A равно нулю |

||||

03xxH |

CALL |

Вызов подпрограммы по адресу, |

||||

|

|

заданному |

младшим |

байтом |

||

|

|

команды |

|

|

|

|

04xxH |

MOV A,xx |

Непосредственная |

загрузка |

в |

||

|

|

регистр A значения, заданного |

||||

|

|

младшим байтом команды |

|

|

||

05xxH |

MOV B,xx |

Непосредственная |

загрузка |

в |

||

|

|

регистр B значения, заданного |

||||

|

|

младшим байтом команды |

|

|

||

0600H |

RET |

Возврат из подпрограммы |

|

|

||

0601H |

MOV A,B |

Загрузка в регистр A значения, |

||||

|

|

содержащегося в регистре B |

|

|

||

0602H |

MOV B,A |

Загрузка в регистр B значения, |

||||

|

|

содержащегося в регистре A |

|

|

||

0603H |

XCHG A,B |

Обмен местами |

значений |

в |

||

|

|

регистрах A и B |

|

|

|

|

0604H |

ADD A,B |

Сложение значений в регистрах A и |

||||

|

|

B, результат помещается в A |

|

|

||

0605H |

SUB A,B |

Вычитание значений в регистрах A |

||||

|

|

и B, результат помещается в A |

|

|||

0606H |

AND A,B |

Побитное логическое И значений в |

||||

|

|

регистрах A и B, результат |

||||

|

|

помещается в A |

|

|

|

|

0607H |

OR A,B |

Побитное |

логическое |

ИЛИ |

||

|

|

значений в регистрах A и B, |

||||

|

|

результат помещается в A |

|

|

||

0608H |

XOR A,B |

Побитное |

|

логическое |

||

|

|

ИСКЛЮЧАЮЩЕЕ ИЛИ значений |

||||

|

|

в регистрах A и B, результат |

||||

|

|

помещается в A |

|

|

|

|

|

|

168 |

|

|

|

|

При каждом допустимом значении кода команды, происходят различные действия, которые состоят в назначении регистрам новых значений в соответствии с описанием команд. Счетчик команд (регистр) не обновляется автоматически, поэтому в каждом варианте кода команды, присваивание счетчику нового значения, указывается явно. Процессор ограничивается двумя регистрами общего назначения (A и В). Процессор имеет указатель инструкций ip и регистр r (стек), для хранения адреса, с которого произошел вызов подпрограммы, поддерживает минимальный набор команд: команда пересылки ―регистр - регистр‖; команды непосредственной загрузки; команда безусловного перехода к новому адресу; команды перехода по условию; набор арифметико-логических операций. Пример 1 показывает управляющий автомат на языке VHDL.

Наиболее сложными являются команды передачи управления JMP и JMPZ, и команда обращения к подпрограммам CALL и команда возврата из подпрограммы RET. Временные диаграммы на рис.4.4 демонстрируют принцип работы управляющего автомата с асинхронным ПЗУ при отработке команд CALL (0305H) и RET (0600H). При нормальной последовательности работы процессора отрабатываються регистровые команды. Последовательно загружаются регистры А и В. В регистр А загружается число 1D (1H), а в регистр В, число 17D (11H). По команде 0305H происходит запись содержимого счетчика команд ip в регистр r (2D) и загрузка в счетчик команд числа 5D. Таким образом, процессор начнет выполнять подпрограмму хранящуюся в ПЗУ с адреса 5H. По указанному адресу извлекается регистровая команда 0403H. Происходит загрузка в регистр A числа 3H, командой 0404Р загрузка числа 4H. Следющей командой с кодом 0604Н произойдет сложение содержимых регистров с сохранением результата в регистре А (число 21D). Далее будут отработаны команды 0406Н и 0407Н. По команде

169

возврата из подпрограммы 600Н произойдет изменение содержимого счетчика с 10D на 2D+1D, т.е. на 3D.

library ieee;

use ieee.std_logic_1164.all; use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all; entity proc is

port (ip: inout std_logic_vector(7 downto 0);

cmd: inout std_logic_vector(15 downto 0); clk,res: in std_logic;

a: inout std_logic_vector(7 downto 0); b,r: inout std_logic_vector(7 downto 0));

end proc;

architecture a of proc is signal stage: std_logic; begin

process(clk) begin

if (res = '1') then

a<="00000000";

b<="00000000"; ip <="00000000";

elsif clk'event and clk='1' then case stage is

when '0'=> stage<='1'; when others=> stage<='0'; case conv_integer(cmd) is when 0=> ip <= ip+1;

when 256 to 511 =>ip<=cmd(7 downto 0); when 512 to 767 =>if conv_integer(a)=0

then ip<=cmd(7 downto 0); else ip<=ip+1;

end if; when 768 to 1023 =>r<=ip; ip<=cmd(7 downto 0);

when 1024 to 1279 => a<=cmd(7 downto 0); ip<=ip+1; when 1280 to 1535 => b<=cmd(7 downto 0); ip<=ip+1;

170