2831

.pdf3. Порядок выполнения лабораторной работы

3.1.Предварительное задание

3.1.1.По конспекту лекций и литературным источникам, например [3-5], изучите материал о составлении СДНФ логической функции и ее преобразовании.

3.1.2.По материалам п. 2.1, конспекту лекций и литературным источникам изучите назначение, принципы построения

ифункционирования шифраторов.

3.1.3. Составьте заготовку отчета как указано в начале пособия.

3.1.4. Изобразите функциональное представление шифратора, запишите формулу соотношения количества входов и выходов и составьте таблицу, определив по этой формуле 14 значений а

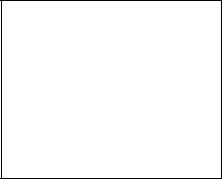

Таблица 6

n |

3 |

4 |

… |

16 |

a |

… |

… |

… |

… |

3.1.5.Составьте в письменной форме план эксперимента по исследованию бесприоритетного (факультативного) шифратора 7х3 на базе логических микросхем: разработайте в соответствии с (3.2) его принципиальную схему, подберите соответствующую элементную базу (см. приложения), выберите расположение компонентов на стенде. Разметьте схему как описано в разделе «Подготовка к выполнению лабораторной работы».

3.1.6.Перенесите в отчет таблицу функционирования этого шифратора. Дополните таблицу снизу, проанализировав зна-

чения A2, A1, A0 и А10 при трех различных комбинациях

двух или нескольких совместных перекрывающихся и неперекрывающихся входных воздействий (например, указанных в п. 2.2,1). Подготовьте объяснение этих результатов. Данная таблица входит в план первого эксперимента работы.

41

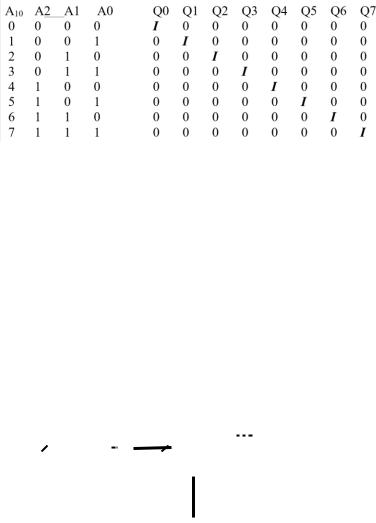

3.1.7. Перенесите в отчет принципиальную схему, приведенную на рис. 19, в дробной маркировке проводов в жгуте указывайте только числители. Под схемой оставьте место для ее дополнения примерно десятью инверторами.

3.1.8. По конспекту лекций и справочникам (например, [5- 9]) изучите функциональные возможности шифраторов, выпускаемых в интегральном исполнении, т.е. в виде готовых микросхем. Занесите в отчет УГО микросхемы ИВ1 и ее таблицу истинности. Объясните с помощью таблицы назначение выводов 5, 14, 15 микросхемы.

3.1.9.Перенесите в отчет принципиальную схему, приве-

денную на рис. 20, изменив размещение сигналов на выходах ИВ1 и логики так, чтобы старшие разряды (А3, А2) располагались над младшими. Присвойте имена всем промежуточным связям (желательно в соответствии с выводимыми сигналами, например, 1А0…1А2, 1G и т.д.), указав их на схеме.

3.1.10.Для исследования схемы выберите 4 входа младшего шифратора (обязательно включая Х0) и 3 входа старшего (отметьте их на схеме). По аналогии с п. 3.1.5, 3.1.6 составьте на основе этой схемы таблицу (план эксперимента) по исследованию приоритетного шифратора 16х4 на двух микросхемах ИВ1, содержащую следующие столбцы: наименования входа или входов Xi#, состояние выходов G каждого шифратора и схемы в целом, выходные коды А (А3…А0) и их десятичные эквиваленты для дальнейшей экспериментальной проверки. Строки таблицы должны содержать следующие серии опытов:

1) без входных сигналов (все входы на пассивном уровне) – 1 опыт;

2)с подачей активного уровня на один из выбранных входов каждого шифратора, начиная с Х0, – 7 опытов;

3)с одновременной подачей двух или более сигналов на младший шифратор – 3 опыта;

4)с одновременной подачей двух или более сигналов на старший шифратор – 3 опыта;

5)с одновременной подачей двух сигналов на разные ИВ1

–4 опыта.

42

3.2.Рабочее задание

3.2.1.Предъявите преподавателю все материалы, подготовленные при выполнении предварительного задания, устраните обнаруженные им ошибки.

3.2.2.Доработайте под руководством преподавателя схему, перенесенную в отчет с рис. 3.3, таким образом, чтобы выполнялись задачи, указанные выше при ее анализе. Подсчитайте расход микросхем на ее реализацию.

3.2.3.Запустите на ПК программу VirtualPCB, наберите в редакторе разработанную вами схему для реализации факультативного шифратора. Входы схемы подключите к линиям поля ввода, выходы А – к линиям поля индикации.

3.2.4.Проверьте результат ввода, как указано выше, в ча-

стности проверьте отображение всех выходных сигналов в

поле индикации; если какого-то имени нет, удалите связь и создайте ее снова. Сохраните схему под именем ЛР3_1.

3.2.5.Установите выбранные вами микросхемы в колодки согласно правилу, приведенному выше, включите питание стенда и щелкните «Соединиться с устройством». Подавая активные сигналы (лог. ˶0") на входы шифратора согласно плану

эксперимента, наблюдайте результаты по показаниям в поле индикации, сверяя их с подготовленной таблицей истинности. В случае несоответствия найдите ошибку в таблице соединений или в коммутации, сохраните исправленную схему. После завершения эксперимента проведите анализ полученных результатов и сформулируйте выводы, занеся их в отчет.

3.2.6. Щелкните «Отсоединиться», выключите питание стенда и удалите элементы и связи. Наберите схему для исследования приоритетного шифратора 16х4 на двух микросхемах ИВ1. Верхнюю линию поля ввода обозначьте L1. К последующим линиям поля ввода подключите 7 входов схемы, выбранных в п. 3.1.9, остальные – к линии L1. К линиям поля индикации подключите выходы А3…А0, G, а также выходы G# обоих шифраторов.

43

3.2.7. Проверьте результат ввода, как указано выше. Сохраните схему под именем ЛР3_2.

3.2.8. Проведите исследование по предварительно подготовленной таблице (п. 3.1.10).

3.2.9. Подготовьте отчет, оформив его в соответствии с требованиями п. 1.4 "Общих положений".

4.КОНТРОЛЬНЫЕ ВОПРОСЫ

1.Дайте описание процедуры составления СДНФ и СКНФ логической функции и их минимизации.

2.Приведите определение шифратора и двоичного шифратора.

3.Подсчитайте, сколько выходов будут иметь шифраторы с 10, 20, 30 входами.

4.Опишите различия в функционировании шифраторов, синтезированных способами 2.2.1, 2.2.2 и 2.2.3, назовите причину этих различий, перечислите преимущества и недостатки каждого варианта.

5.Запишите СДНФ функций A1, A2 классической реализации рассмотренного шифратора.

6.Запишите выражения для функций A1, A2 приоритетной реализации рассмотренного шифратора.

7.Объясните принцип построения и функционирования переработанной вами схемы трехразрядного приоритетного шифратора, пользуясь полученной таблицей его состояний, приведите перечень (кодировку) элементов, необходимых для его создания.

8.Изложите сведения о функциональных возможностях приоритетных шифраторов, существующих в интегральном исполнении.

9.Дайте словесное описание работы ИВ1, пользуясь составленной вами таблицей истинности.

44

Лабораторная работа № 4

ИССЛЕДОВАНИЕ КОММУТАТОРОВ ИНФОРМАЦИОННЫХ ПОТОКОВ

1.Цель работы

1.1.Изучить принципы функционирования мультиплексоров и демультиплексоров.

1.2.На примере схемы полного трехразрядного коммутатора получить практические навыки разработки функциональных узлов цифровой электроники.

2.Теоретические сведения

2.1.Определение коммутаторов информационных потоков

Определим одноканальные коммутаторы информационных потоков как комбинационные устройства, имеющие x инфор-

мационных входов, y выходов, m адресных входов для выбора источника входной информации и n адресных входов для вы-

бора одного из выходов и выполняющие передачу информации

с одного выбранного двоичным адресным кодом входа на единственный выход, выбранный вторым адресным кодом.

Номер выбранного входа равен десятичному значению кода АМ, номер выбранного выхода – значению кода АD. Графическое (функциональное) обозначение такого коммутатора будет иметь вид, приведенный на рис. 21.

I |

x |

DI |

MX- |

DO |

y |

Q |

|

|

|||||

|

DMX |

|

||||

|

|

|

|

|

|

|

AM |

m |

AM |

|

|

|

|

|

|

|

|

|

||

n |

|

|

|

|

||

AD |

AD |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

||

|

|

|

|

|

|

|

Рис. 21

В общем случае коммутаторы информационных потоков могут иметь также входы Е разрешения ввода, входы ОЕ раз-

45

решения вывода информации и входы/выходы других специальных сигналов. Коммутаторы информационных потоков могут быть многоканальными, в этом случае все группы входов или выходов управляются общими сигналами адреса и общими или раздельными сигналами Е, ОЕ. Количество адресных входов (разрядность коммутатора m, n) в зависимости от количества информационных входов/выходов определяется соотношениями

m = int (log2x), n = int (log2y). |

(6) |

Коммутаторы с m = log2x, n = log2y называют полными, |

|

а с m > log2 x (т.е. x < 2m), n > log2y – неполными. |

|

Разновидность коммутаторов информационных |

потоков, |

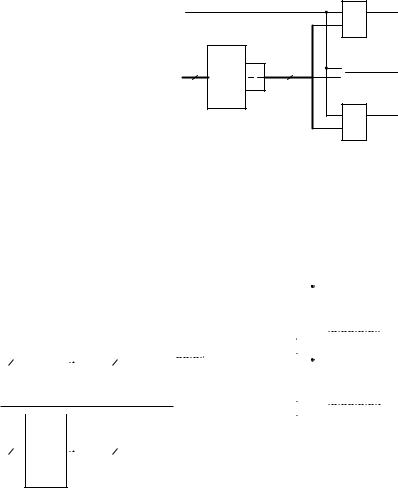

которые имеют несколько информационных входов и один выход (многоканальные – несколько выходов) и которые обеспечивают передачу информации на выход со входа, выбранного адресным кодом, называют мультиплексорами, а также муль- типлексорами-селекторами (или просто коммутаторами). Соответственно функциональное обозначение на УГО имеет вид MUX, MX или MS. Если обозначить информационный поток на входе 0 как I0, на входе 1 как I1, и т.д., а сигнал на выходе как Q, то, например, таблица функционирования мультиплексора 8-1 будет иметь вид, приведенный в табл.7.

Неполные мультиплексоры обычно не используются.

Разновидность коммутаторов информационных потоков, которые имеют один информационный вход (многоканальные – несколько входов) и несколько выходов и которые обеспечи-

Таблица 7

А10 |

А2 |

А1 |

А0 |

Q |

0 |

0 |

0 |

0 |

I0 |

1 |

0 |

0 |

1 |

I1 |

2 |

0 |

1 |

0 |

I2 |

3 |

0 |

1 |

1 |

I3 |

4 |

1 |

0 |

0 |

I4 |

5 |

1 |

0 |

1 |

I5 |

6 |

1 |

1 |

0 |

I6 |

7 |

1 |

1 |

1 |

I7 |

вают передачу информации с входа на выход, выбранный адресным кодом, называют демультиплексорами. Их функциональное обозначение на УГО – DMX. Если обозначить инфор-

46

мационный поток на входе как I, а сигналы на выходах как Q0...Q7, то таблица функционирования демультиплексора 1-8 будет иметь вид (табл. 8)

Таблица 8

Неполные демультиплексоры используются, например, для получения сигналов, соответствующих десятичной цифре (n=10) или для опознавания адреса устройства (минимальное значение n=1).

2.2. Функциональные схемы коммутаторов

Рассмотрим функциональную схему (логическую структуру) полного мультиплексора, имеющего m адресных входов. Его рабочая функция реализуется сочетанием трех более простых функций: дешифрации адресной комбинации, логического ключа и логического объединения (рис. 22).

I0 |

|

|

|

|

|

|

|

|

|

DI |

1 |

|

|

1 |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

IK |

|

|

|

|

|

|

|

|

|

|

|

E |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

DC |

|

|

2m |

|

|

|

|

|

|

|

|

|

|

|

АД |

|

|

m |

|

|

|

|

|

|

|

|

|

|

|

|

Q |

|||

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I |

m |

|

|

|

|

|

|

|

|

|

|

DI |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

2 |

-1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

E |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

Рис. 22 |

|

|

|

|

|

|

||||

47

Работа дешифратора описана в литературе, например [4-13]. |

|||||||||

Функцию ключа обычно выполняют схемы И, поскольку I & 1 = |

|||||||||

=I, I & 0 = 0. Функция объединения выполняется схемой ИЛИ. |

|||||||||

В совокупности эти функциональные узлы обеспечивают задан- |

|||||||||

ную |

функцию |

устройства |

– |

передачу |

на выход |

сигналов |

|||

с выбранного входа. |

|

|

|

|

|

||||

Функциональная схема полного одноканального демульти- |

|||||||||

плексора, имеющего n адресных входов, выглядит аналогично. |

|||||||||

Его рабочая функция реализуется сочетанием функций дешиф- |

|||||||||

рации адресной комбинации и логического ключа (рис. 23). |

|||||||||

В |

списке |

литерату- |

|

|

|

& |

|

||

ры [4, 5, 10, |

12] |

приве- |

I |

|

|

Q0 |

|||

|

|

|

|||||||

дены |

иные |

функци- |

|

|

|

|

|

||

ональные схемы |

муль- |

|

|

DC |

|

|

|||

типлексоров |

и демуль- |

|

|

|

|

||||

|

n |

|

n |

|

|||||

типлексоров. Они полу- |

АD |

|

2 |

|

|||||

|

|

|

|

||||||

|

|

|

|

|

|||||

чены |

в результате |

раз- |

|

|

|

|

|

||

вертывания дешифрато- |

|

|

|

& |

n |

||||

|

|

|

|

Q2 -1 |

|||||

ра до уровня логических |

|

|

|

|

|

||||

элементов, а также объ- |

|

|

Рис. 23 |

|

|||||

единения |

выходных |

|

|

|

|||||

|

|

|

|

|

|||||

элементов И дешифратора и логических ключей мультиплексо- |

|||||||||

ра или демультиплексора. |

|

|

|

|

|

||||

Исходя из схем, приведенных на рис. 22, 23, функциональ- |

|||||||||

ную схему коммутатора, включающего MX+DMX, можно пред- |

|||||||||

ставить в виде, изображенном на рис. 24. |

|

|

|||||||

I0 |

|

|

|

|

|

|

|

|

& |

|

|

1 |

|

|

|

|

& |

|

Q0 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

Ij |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

DC |

|

|

2m |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

m |

AM |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

АM |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

QK |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

I m- |

1 |

|

|

|

|

& |

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

n |

|

|

|

|

|

|

|

|

& |

|

Q |

m |

|||

|

|

|

|

|

AD |

|

|

|

|

|

|

|

|

|

|

|

||||||

АD |

|

|

|

n |

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

2 -1 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 24

48

2.3. Реализации коммутаторов информационных потоков

Мультиплексоры и демультиплексоры могут быть аппаратно реализованы на логических элементах, на программируемой логике и в виде специальных микросхем. Например, простейший мультиплексор 2-1, реализованный на основе логических элементов типов ЛН и ЛР, будет иметь вид, приведенный на рис. 25.

Использование ПЛМ для реализации коммутаторов (см. п. 2.1) возможно, но нецелесообразно, поскольку в настоящее

время в составе различных серий |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

ТТЛ выпускается множество за- |

I0 |

|

|

|

|

|

|

& |

1 |

|

|

|

|

|

|||||||

конченных |

интегральных |

схем |

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

мультиплексоров |

и |

демуль- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

типлексоров |

различной |

разряд- |

I1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

Q |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

ности, |

имеющих к тому же те |

|

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

|||||

или |

иные |

дополнительные |

A |

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

1 |

|

|

1 |

|

|

|

|

|

|

|

|

|||||||||

функции |

(перевод |

в третье со- |

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

стояние, |

запрет |

и т.д.). |

УГО, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

схемы |

и функциональные |

воз- |

|

|

|

|

|

Рис. 25 |

|||||||||||||

можности этих микросхем при- |

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

ведены в литературе. В качестве демультиплексоров используются микросхемы дешифраторов со входом (входами) разрешения. На этот вход и подается входной информационный поток. Следует обратить внимание на то, что выходы дешифраторов/демультиплексоров обычно инверсные, соответственно на невыбранных выходах (если нет третьего состояния) сохраняется потенциал лог. ˶1". Многоканальные демультип-

лексоры (напр., ИД4) могут использоваться как одноканальные с увеличением разрядности, если соответствующим образом скоммутировать их входы.

Полные многоразрядные коммутаторы (m n разрядов) строят в виде каскадного соединения m-разрядного мультиплексора и n-разрядного демультиплексора.

49

2.4. Дополнительные возможности мультиплексоров

К дополнительным возможностям MX можно отнести: каскадирование; построение устройств, сдвигающих код в смежные разряды; построение на базе MX комбинационных устройств. Последняя возможность подробно рассмотрена в конспекте лекций и литературе [5,8]. Соответствующий материал следует внимательно изучить для дальнейшего использования в ходе лабораторной работы.

3. Порядок выполнения лабораторной работы

3.1. Предварительное задание

3.1.1. По литературе [4-13] и разделу 2 ознакомьтесь с назначением, УГО, принципом действия и функциональными схемами мультиплексоров и демультиплексоров.

3.1.2.Составьте заготовку отчета согласно разделу "Общие положения". Из справочной литературы или конспекта лекций перенесите в нее УГО и функциональные схемы микросхем К555ИД7 (дешифратор-демультиплексор) и К555КП7 (мультиплексор), разберитесь в назначении их входов и выходов.

3.1.3.В соответствии с изученной методикой составьте схему и план эксперимента для реализации на основе схемы ЛР1_1 и мультиплексора КП7 формирователя временной диаграммы, исследованной вами в работе № 1. Разметьте схему как описано в разделе «Подготовка к выполнению лабораторной работы».

3.1.4.Составьте в письменной форме план эксперимента по разработке и исследованию полного коммутатора, позволяющего подключить выход любого из 8 источников информации ко входу любого из 8 приемников информации:

проведите функциональный анализ проектируемого устройства, определите разрядность адресных комбинаций;

соотнеся основные функции коммутатора и возможности

микросхем К555КП7 и К555ИД4, разработайте в соответствии

50