2831

.pdf

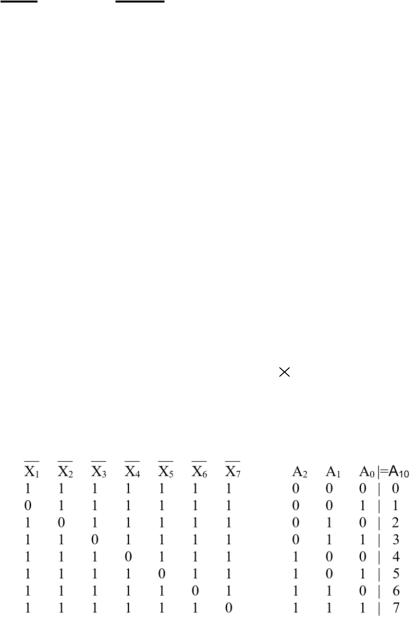

риант задания, соответствующую таблицу истинности для Y1…Y4, СДНФ или СКНФ этих функций.

3.2.2. Выполните такие преобразования СДНФ или СКНФ, чтобы реализовать каждую из функций с минимальным количеством и разнообразием микросхем (минимальный элементный базис). Например, Y4 X1 X 2 удобно реализовывать на од-

ной микросхеме ЛА3, используя один элемент для инвертирования Х1, второй – для логического умножения с инвертированием, третий – для повторного инвертирования результата

X1 X 2 Y4 . Для выражений вида YK = MAVMBVMC, где MA, MB, MC – три минтерма (конъюнктивных выражения), удобно использовать преобразование (MAVMB)V(MAVMC), где в качестве MA следует выбрать тот из минтермов, который позволит оптимально упростить обе скобки (вынести общие множители). В скобках должны остаться функции неравнозначности, эквивалентности, импликации, которые затем следует выразить так, чтобы их можно было реализовать в минимальном элементном базисе.

3.2.3. Составьте по результатам преобразования принци-

пиальные схемы и приведите их в отчете. При этом в качестве инверторов следует применять элементы «исключающее ИЛИ» и «И-НЕ», но так, чтобы в схеме было минимальное количество корпусов микросхем, а в каждой из них использовалось максимальное количество элементов (клапанов). При необходимости использовать константу лог. ˶1" изо-

бражайте на входе логического элемента проводник с именем L1. Разметьте каждую из схем так, как описано в разделе «Подготовка к выполнению лабораторной работы». Для расположения микросхем следует использовать разъемы +2 и +3. Номера выводов (распиновку) найдите в справочнике и нанесите на схему по правилам, приведенным в [1].

3.2.4. Запустите на ПК программу VirtualPCB, загрузите схему ЛР1_2, переименуйте выходные сигналы как в заготовке отчета, удалите индикацию ненужных сигналов, сохраните схему как ЛР2_1.

31

3.2.5. Наберите в редакторе на основе ЛР2_1 разработанную вами схему для реализации той из функций Y, СДНФ которой включает 3 конъюнкции и которая указана на выданной диаграмме значком . Сигнал L1 снимайте с одной из линий поля констант. Проверьте распиновку, вызывая УГО использованных микросхем. На индикацию под линиями Х1, Х2, Х3 выведите сигнал Y. Константы L1, R# и S# установите в лог. ˶1".

3.2.6.Проверьте результат ввода, как указано выше, в частности проверьте отображение всех выходных сигналов в поле индикации, если какого-то имени нет, удалите связь и создайте ее снова. Сохраните схему под тем же именем ЛР2_1.

3.2.7.Установите нужные микросхемы в колодки согласно правилу, приведенному выше, включите питание стенда и щелкните «Соединиться с устройством». Генератор G1 переведите в режим «2 Гц» и запустите. Наблюдайте значения в поле индикации и на диаграмме до ее заполнения.

Остановите генератор, сдвиньте диаграмму влево так, чтобы в ее начале значения сигналов Х1, Х2, Х3 были нулевыми, проверьте совпадение диаграммы Y с заданной.

Если что-то не так, то проверьте правильность соединений согласно рекомендациям по поиску неисправностей или же правильность преобразований в ходе синтеза автомата. Сохраните исправленную схему.

4.КОНТРОЛЬНЫЕ ВОПРОСЫ

1.Как построить таблицу истинности цифрового автомата по временной диаграмме его функционирования?

2.Что отражает формула логической функции?

3.Дайте описание процедуры составления СДНФ и СКНФ логической функции и их минимизации.

4.По каким принципам выбирают элементную базу для реализации логической функции?

5.Изложите последовательность действий при синтезе цифрового автомата по заданной временной диаграмме.

6.Какие ошибки возможны при синтезе цифрового автомата по заданной временной диаграмме?

7.Как построить временную диаграмму по таблице истинности цифрового автомата?

32

Лабораторная работа № 3

ИССЛЕДОВАНИЕ ШИФРАТОРОВ НА ЛОГИЧЕСКИХ ЭЛЕМЕНТАХ

ИСПЕЦИАЛЬНОЙ МИКРОСХЕМЕ

1.Цель работы

1.1.Изучить принципы построения схем шифраторов.

1.2.На примере схемы трехразрядного шифратора получить практические навыки сборки и наладки макетных образцов функциональных узлов вычислительной техники.

2.Теоретические сведения

2.1. Определение шифраторов Шифраторами или кодерами называют разновидность

преобразователей кодов, которые преобразуют комбинации (слова) унитарного кода в соответствующие слова какого-либо позиционного кода. Двоичные шифраторы – это комбинационные схемы, которые при подаче активного уровня на один из n информационных входов выдают на выходе слово позицион-

ного двоичного кода, значение которого соответствует но-

меру активного входа. При этом разрядность выходного слова a составляет

a = int (log2n) разрядов, (1)

где int означает округление в бóльшую сторону до целого числа.

Шифратор с n входами иногда называют шифратором n х a (например, 10х4). Графическое обозначение такого шифратора имеет вид, приведенный на рис. 17. Для удобства сопряжения с переключателями и т.п. периферийными устройствами схему шифраторов обычно организуют так, чтобы активным уровнем служил лог. ˶0".

33

|

n |

|

|

|

a |

Как и другие преобразователи |

|

|

|

|

|

||||

|

|

|

|

|

|||

I |

/ |

|

D1 |

CD |

D2 |

/ |

Q кодов, шифраторы могут быть ап- |

|

|||||||

|

|

|

|

|

|

|

паратно реализованы на логиче- |

|

|

|

|

|

|

|

|

|

|

|

Рис. 17 |

|

ских элементах, на программи- |

||

|

|

|

|

руемой логике и на совокупности |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

специальных микросхем. |

2.2. Синтез двоичного шифратора на логических элементах

Простота алгоритма преобразования делает шифратор удобным объектом для выработки навыков синтеза комбинационных схем. Построим шифратор с 7 входами и нулевым состоянием, управляемый низкими входными уровнями. Пример источника инверсного унитарного кода приведен на рис. 18.

Здесь переключатель SA1 имеет за- |

|

|

|

|

|

|

|

|

|

SA |

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

земленный |

обегающий контакт, а |

|

|

|

|

|

|

|

|

|

X 7 |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

1 |

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X 6 |

|||||

сигнальные линии X7 ...X1 |

подтяну- |

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

X |

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

7 |

|

|

|

|

|

|

X |

5 |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

ты к лог. ˶1" с помощью набора ре- |

*R |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

X6 |

|

|

|

|

X 4 |

|||||||||||||||

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

X5 |

|

|

|

|

|

|

|

|||||

зисторов *R. |

|

|

|

|

|

|

|

|

|

|

|

|

|

X 3 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

X 4 |

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

X 2 |

||||||||||

Выходной код этого шифрато- |

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

X3 |

|

|

|

X1 |

|||||||||||||||

|

|

|

|

|

|||||||||||||||||||

ра согласно соотношению (3.1) бу- |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

X 2 |

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||||

дет |

состоять |

из |

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

X1 |

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

||||||||||||||||

int (log27) = 3 разрядов. По |

словес- |

|

|

|

5 В |

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

ному описанию составим таблицу |

|

|

|

Рис. 18 |

|

|

|

|

|||||||||||||||

функционирования (табл. 3): |

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

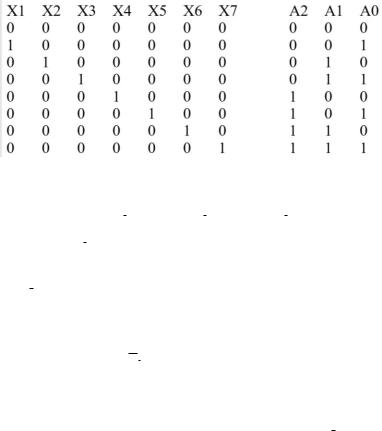

Таблица 3 |

||||||

34

В принципе существует несколько способов синтеза логических функций Аi (i = 0…2), соответствующих этой таблице.

2.2.1. В простейшем случае (факультативная шифрация) логические формулы функций могут иметь вид:

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

А0= X1vX3vX5vX7 |

= X X |

3 |

X |

5 |

|

X |

7 |

|

|||||||||||

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

А1= X2vX3vX6vX7 |

= X |

X |

|

X |

X |

7 |

|

(2) |

|||||||||||

|

2 |

3 |

|

6 |

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

А2= X4vX5vX6vX7 |

= X |

X |

|

X |

X |

7 |

|

|

|

||||||||||

|

4 |

5 |

|

6 |

|

|

|

|

|

|

|

||||||||

Такое решение дает минимальный объем аппаратных средств (по 0,5 корпуса микросхемы ЛА1 на каждый выход). Однако функции Аi определены в таблице истинности не на полном множестве комбинаций входных сигналов, т.е. фа-

культативно. Проанализируем их значения при неунитарном наборе на входах (сигналы от произвольного набора источников). Полное возможное количество входных комбинаций составляет 27=128, то есть существует 120 комбинаций с неопределенностью. Рассмотрим, например, какой код будет на выходе, согласно (2), при X2&X4=1, или X3&X5=1, X1&X4 =1 и так далее. Полученные коды не соответствуют ни одному из номе-

ров входов – устройство оказалось незащищенным от не-

правильного использования. Его следует применять только для шифрации положения переключателей с обегающим контактом и других подобных устройств, в которых одновременное появление активных уровней на нескольких входах кодера невозможно в принципе.

2.2.2. Повторим исходную таблицу истинности в положительной логике (табл. 4):

35

Таблица 4

Исключить ложные коды можно, записав логические функции в классической СДНФ:

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

) , (3.3) |

||||||||

|

|

A =X (&X1 ) X |

(&X3 ) X |

(&X5 ) X |

(&X |

|

||||||||||||||||||||||||||||||

7 |

||||||||||||||||||||||||||||||||||||

0 |

1 |

|

|

|

|

3 |

|

|

|

|

|

|

5 |

|

|

|

|

|

7 |

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

где &XJ – логические произведения инверсий всех аргу- |

||||||||||||||||||||||||||||||||||

ментов, |

|

кроме |

|

|

указанного |

|

в |

|

|

индексе |

|

(например, |

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

). А1 и |

||||||||||||||

&X3 = X1 X2 X4 X5 X6 X7 =X X |

2 |

X |

4 |

X |

X |

6 |

X |

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

5 |

|

|

7 |

|

|||||||||||||

А2 определяются аналогично. Оценка затрат аппаратных средств – 12,5 корпуса. Можно было бы записать Аi и в виде СКНФ: А0=(X1v(vX1 ))&(.......) и так далее, но не выпускается шестивходовых микросхем ИЛИ, поэтому аппаратная реализация будет еще более громоздкой. Результат такого пути синтеза формально точен – ложные коды при Xj& X j = 1 отсутству-

ют, но с инженерной точки зрения потеря входных сигналов при их взаимном наложении зачастую недопустима.

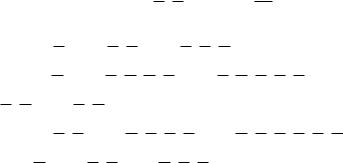

2.2.3. На практике выбран третий путь синтеза – по приоритетной таблице функционирования. При этом чисто договорно задают, какой вход имеет приоритет над остальными (обычно вход с большим номером – над всеми входами с меньшими номерами). Тогда таблица функционирования будет иметь вид (табл. 5):

36

Таблица 5

Здесь знак Ф означает произвольное, несущественное для функционирования устройства значение аргумента. Видно, что в этом варианте нужно создавать вдвое меньше логических произведений (по 6-5-4..1-0 штук) и для А0, например, логическое уравнение будет иметь вид:

|

|

|

|

|

|

(4) |

A0 =X1 (&X>1 ) X3 (&X>3 ) X5 X6 X7 X7 |

||||||

Соответствующие уравнения для А1 и А2 студентам следует составить самим. С точки зрения затрат это означает, что нужно 6 схем приоритета: одна с шестью входами, одна с пятью и т.д., т.е. схема остается громоздкой. Первый путь ее упрощения – использовать одни и те же конъюнкции многократно, т.е. построить схему последовательного логического умножения X7 X6 ... X2 с промежуточными отводами (нарисуйте такую схему шифратора). Затраты аппаратных средств составят 8 корпусов с резервом. Недостаток этого решения – разное время прохождения сигнала от Xi до Аj, т.е. наличие кри-

тических состязаний второго вида (ложные коды в момент установления нового значения). Второй путь – выявить в формулах Аj лишние вхождения аргументов: ведь если одновременно X1=1 и X5=1, то проход X1 на А0 блокировать уже не нужно и так далее. База такой минимизации – теорема разложения в инверсном виде (по [5], формула 1.27):

|

|

|

|

Xpv f (Xn,..., X p ,...,X1)=Xpv f (Xn,...,1,...,X1). |

(5) |

||

37

В нашем случае X7 X7 X6X5 = X7 X6X5 и так далее. Отсюда, последовательно применяя (3.5) к X7, X6, X5, получим:

A2 =X7 X6 X7 X5 X6 X7 X4 X5 X6 X7 =X7 X6 X5 X4 ; A1 =X7 X6 X7 X3 X4 X5 X6 X7 X2 X3 X4 X5 X6 X7 =X7 X6X3 X4 X5 X2 X4 X5 ;

A0 =X7 X5 X6 X7 X3 X4 X5 X6 X7 X1 X2 X3 X4 X5 X6 X7 =

=X7 X5 X6 X3 X4 X6 X1 X2 X4 X6.

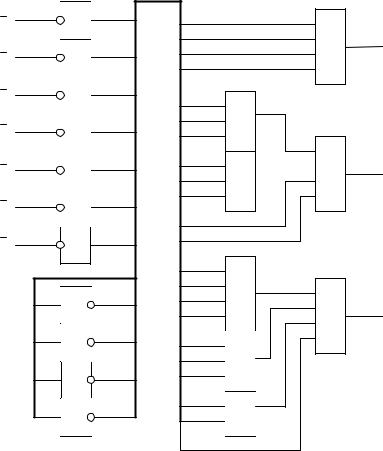

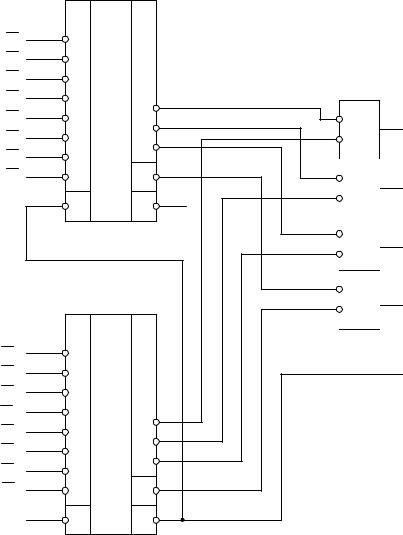

Соответствующая принципиальная схема приведена на рис. 19 (условный расход комплектующих составляет 5,25 корпуса). Схема выполняет заданную функцию и соответствует таблице функционирования, однако, во-первых, четырехвходовые микросхемы ИЛИ не выпускаются промышленностью, во-вторых, разное количество логических элементов между входом и выходом для разных аргументов ведет к критическим состязаниям второго вида (ложные коды низкоприоритетных входов в момент установления новой пары значений). Для получения работоспособной схемы студентам сле-

дует самостоятельно переработать схему, приведенную на рис. 19. Следует заменить схемы 4ИЛИ на 4НЕ-ИЛИ, ввести инверторы на выходы схем И, а также изменить длину путей от входов до выходов с помощью дополнительных инверторов так, чтобы инверсии высокоприоритетных сигналов приходили на выходную логику раньше, чем низкоприоритетные сигналы. Переработанную схему следует привести в отчете.

38

|

1 |

1 |

X1 |

|

|

|

|

|

X2 |

1 |

2/2 |

|

||

X3 |

1 |

3/2 |

|

||

X4 |

1 |

4/2 |

|

||

X5 |

1 |

5/3 |

|

||

X6 |

1 |

6/3 |

|

||

X7 |

1 |

7/3 |

|

||

2 |

1 |

12 |

|

|

|

4 |

|

14/4 |

|

1 |

|

|

|

|

5 |

|

15/2 |

|

1 |

|

|

|

|

6 |

|

16/3 |

|

1 |

|

|

|

4

5

6

7

2

14

15

3

14

15

6

7

1

12

14

16

3

14

16

5

16

7

1

A2

&

1

& |

|

A1 |

|

&

1

A0

&

&

Рис. 19

2.3. Иные реализации двоичных шифраторов

Для реализации шифраторов возможно использование ПЛМ (см. п. 2.1), но это нецелесообразно, поскольку в настоящее время в составе различных ТТЛ серий выпускается несколько законченных интегральных схем приоритетных шифраторов (ИВ1..ИВ3), УГО, схемы и функциональные возможности которых приведены в литературе [5-9]. Микросхемы ИВ1, ИВ2 помимо основной функции – преобразования кода – выполняют индикацию наличия или отсутствия активных

39

уровней хотя бы на одном из входов. Эти сигналы используются для разрешения работы смежных микросхем (рис. 20).

ИВ1

X0

X1

X2

X3

X4

X5

X6

X7

X8

X9

X10

X11

X12

X13

X14

X15

...

I |

PRCD А |

|

0 |

|

|

1 |

|

|

2 |

|

|

3 |

0 |

|

4 |

||

1 |

||

5 |

||

2 |

||

6 |

||

|

||

7 |

G |

|

Е |

EC |

|

ИВ1 |

|

I |

PRCD А |

|

0 |

|

|

1 |

|

|

2 |

|

|

3 |

0 |

|

4 |

||

1 |

||

5 |

||

2 |

||

6 |

||

|

||

7 |

G |

|

Е |

EC |

1

A0

1

A1

1

A2

1

G

A3

40