лаба2

.docxФЕДЕРАЛЬНОЕ АГЕНТСТВО ЖЕЛЕЗНОДОРОЖНОГО ТРАНСПОРТА

Федеральное государственное бюджетное образовательное учреждение высшего образования

«Петербургский государственный университет путей сообщения

Императора Александра I»

(ФГБОУ ВО ПГУПС)

Факультет «Автоматизация и интеллектуальные технологии»

Кафедра «Информационные и вычислительные системы»

ЛАБОРАТОРНАЯ РАБОТА №2

по дисциплине

«Основы микропроцессорной техники и программирования»

ТЕМА РАБОТЫ

«Исследование структуры простейшей микроЭВМ и микропроцессора I8085»

Выполнил:

Обучающийся группы : АР-709 |

________________ Дата, подпись |

Баранов Д.А. И.О. Фамилия |

|

|

|

Исправить замечания:

|

________________ Дата, подпись |

Баушев А.Н. Должность, И.О. Фамилия |

Защита: ________________ Зачтено/не зачтено

|

________________ Дата, подпись |

________________ Должность, И.О. Фамилия |

Санкт-Петербург 2020

Цель работы.

Исследование с помощью симулятора AVSIM85 структуры микроЭВМ, ее основных устройств и принципов функционирования .

Изучение внутренней структуры МП I8085A (1821ВМ85), назначения функциональных блоков и принципов взаимодействия при реализации команд

Задание на лабораторную работу (Вариант 14):

1. Ввести с регистров 00, 01, 02, 03 порта 8255 в РОН`ы B, A, D, C соответственно числа: 10001001В, 10011111В, 40Н, 2DН.

2. Сложить числа, введённые в РОН`ы B и D. Зафиксировать состояние флагов регистра признаков.

3. Ввести в ячейки оперативной памяти с адресами 0037Н – 003FН следующие данные (А8, 4D, F7, 4F, 56, 79, 2, 73)Н. Для ввода использовать внешний порт 03Н.

Структурные схемы CPU и микроЭВМ.

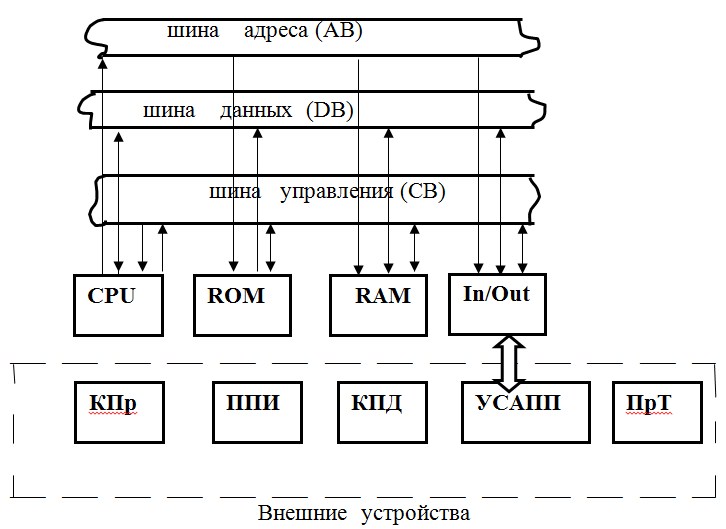

Рис.1 – Типовая архитектура микропроцессорной системы

Разрядность двунаправленной шины данных – от 8 разрядов.

Разрядность шины адреса – от 16 разрядов.

CPU – центральное процессорное устройство. Обеспечивает выполнение всех операций в соответствии с заданным алгоритмом. Практически обеспечивает выполнение всего процесса функционирования системы.

ROM (ПЗУ) – постоянное запоминающее устройство.

RAM (ОЗУ) – оперативное запоминающее устройство.

In/Out - интерфейсы ввода-вывода (порты ввода-вывода). Обеспечивают связь системы с внешними устройствами.

КПр – программируемый контроллер прерываний.

ППИ – программируемый параллельный интерфейс.

КПД – контроллер прямого доступа к памяти для управления внешними запоминающими устройствами.

УСАПП – программируемый последовательный интерфейс (универсальный синхронно-асинхронный приемо-передатчик).

ПрТ – программируемый таймер.

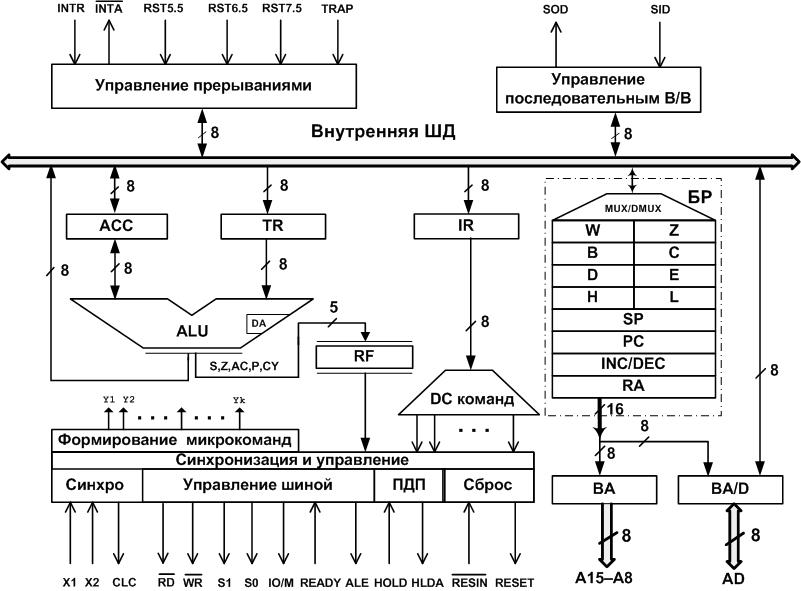

Рис. 2 – Архитектура микропроцессора КР1821ВМ85А.

ШД – 8-разрядная шина данных.

Внутренняя шина данных связывает между собой все блоки МП. Ее разрядность равна разрядности информационного слова.

ША – 16-разрядная шина адреса.

ШУ – шина управления.

МЕМ – память.

PORT – устройства ввода-вывода (порты).

Шина – группа проводов передачи информации, объединенных одним общим функциональным признаком. МП имеет три шины. Совокупность шин образует магистраль.

РОН – регистры общего назначения. Служат для хранения операндов, промежуточных результатов, могут использоваться для хранения адресов памяти. РОН могут объединяться в пары для работы с 16-разрядными данными – BC, DE, HL. Все РОН программно доступны. Разрядность каждого РОН равна разрядности шины данных.

MX/DX- мультиплексор-демультиплексор. Обеспечивает передачу данных с внутренней шины данных в блок РОН.

W,Z – регистры временного хранения. Служат для временного хранения второго и третьего байта кода команды. Регистры программно недоступны.

SP – 16-разрядный указатель стека. В нем хранится адрес последней занятой ячейки стека (вершины стека). При записи данных содержимое регистра увеличивается на 1, а при чтении – уменьшается на 1. Стек реализуется в основной памяти с дисциплиной LIFО.

РС – 16- разрядный счетчик команд (программный счетчик). Используется для приема и хранения текущего адреса команды. При выборке каждого байта команды содержимое программного счетчика автоматически увеличивается на 1, при этом первый байт всегда передается в регистр команд RI.

I/D – схема инкремена-декремента. Позволяет автоматически увеличить или уменьшить на 1 содержимое регистра адреса и совместить во времени модификацию адреса и выполнение операции в АЛУ.

RGA – буферный регистр адреса. Служит для приема и хранения адресной части команды. Разрядность регистра равна разрядности шины адреса.

BD – буферный регистр данных. Используется для временного хранения выбранного из памяти слова перед его передачей на внутреннюю шину данных или для временного хранения результата перед его выдачей во внешнюю шину данных.

IR – регистр команд. Принимает и хранит код очередной команды, адрес которой хранится в программном счетчике.

DCкоманд – дешифратор кода команды.

ALU – 8-разрядное арифметико-логическое устройство. Предназначено для выполнения арифметических и логических операций.

АСС – регистр-аккумулятор или просто аккумулятор. Предназначен для временного хранения операнда или промежуточного результата. При выполнении операции с двумя операндами в А хранится один из операндов, а после выполнения операции – результат. Разрядность А равна разрядности информационного слова.

TR – регистр временного хранения. Предназначен для временного хранения одного из операндов перед выполнением операции в АЛУ.

CU – устройство управления. Вырабатывает последовательность управляющих сигналов, обеспечивающих выполнение микрооперации, расшифрованной по коду операции.

RF – регистр признаков или регистр флагов. В нем формируются признаки результата операции, выполненной в АЛУ. Регистр 8-разрядный, формирует 5 признаков (флагов).

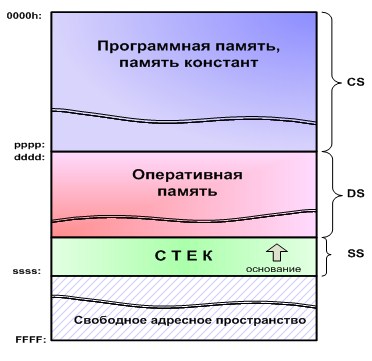

Рис. 3 – Распределение адресного пространства памяти микроЭВМ (2D-модель)

Выполнение работы:

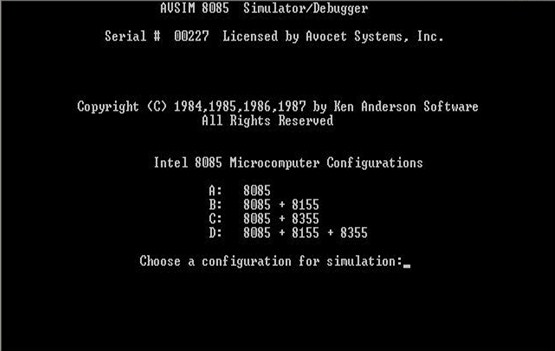

Рис. 4 – Окно запуска симулятора в режиме диалога

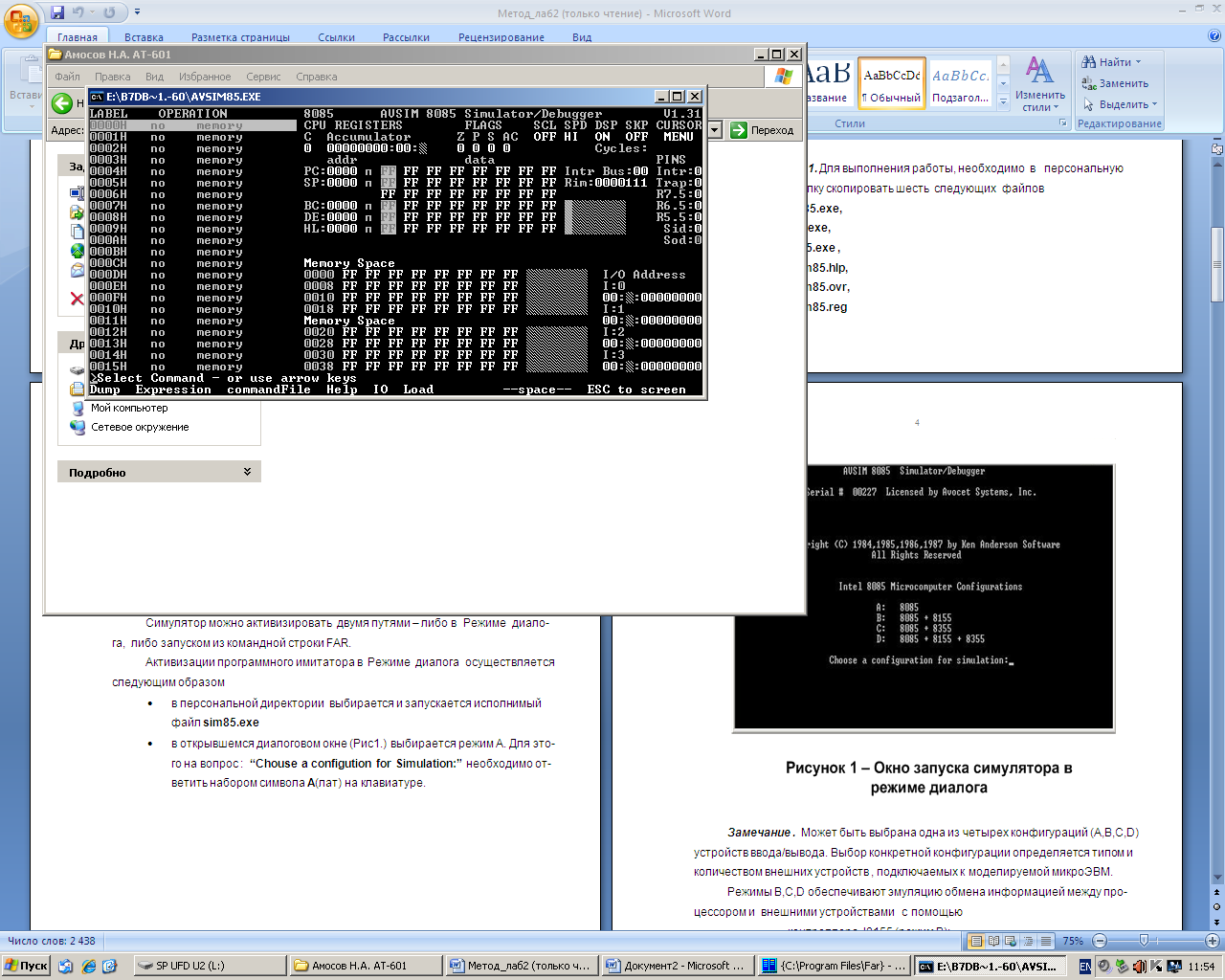

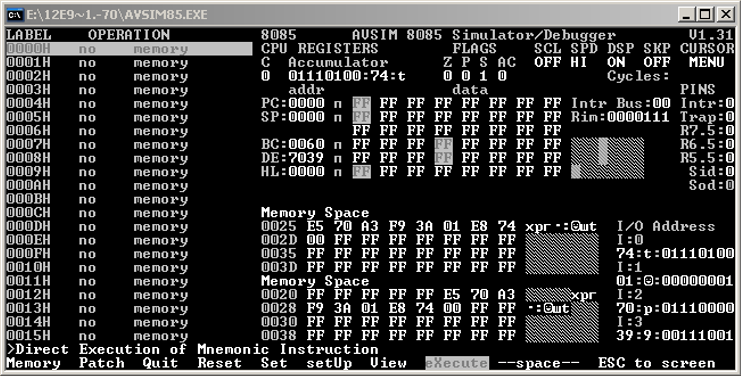

Рис. 5 – Окно симулятора в режиме А

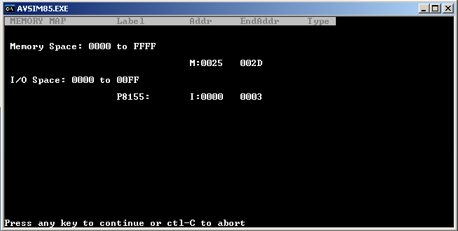

Рис. 6 – Контроль конфигурации симулятора в окне MEMORY MAP

Задание 1

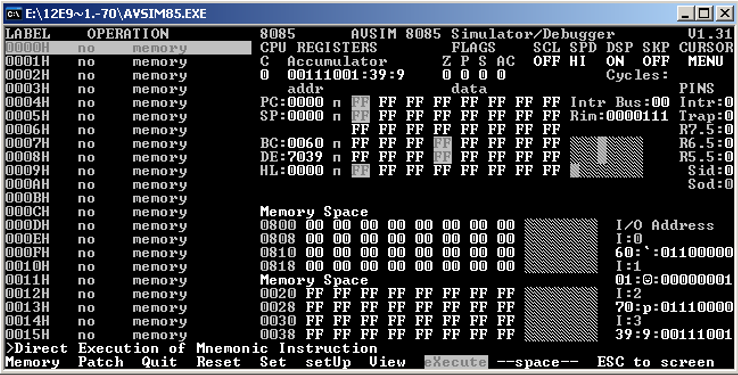

Рис.6 – Ввод данных с текущего порта ввода в соответствующие регистры

Задание 2

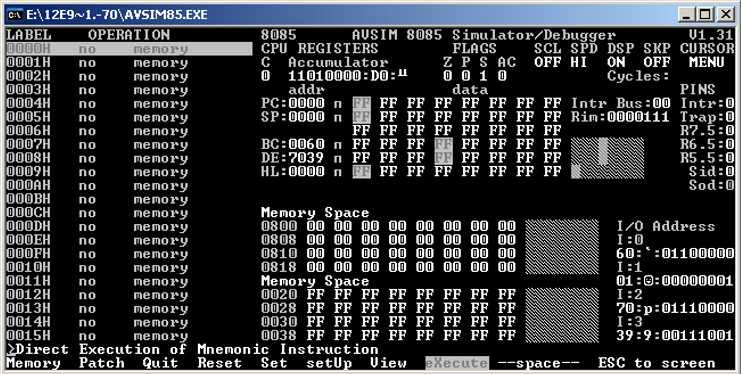

Рис.7 – Результат сложения чисел в симуляторе

Проверка

01100000В 70Н

011000002 = 6016 7016 = 011100002

01100000 70 +01110000 +60

11010000 D0

Задание 3

Рис.8 – Сохранение всех заданных чисел в ячейках с 0037H по 003FH

Вывод

С помощью симулятора AVSIM85 была исследована структуры микроЭВМ, а также ее основные устройства и принципы функционирования, внутренняя структура

МП I8085A (1821ВМ85), назначения функциональных блоков и принципов взаимодействия при реализации команд