Учебники 80389

.pdfмогла бы быть достигнута в идеальном случае. Существуют три класса конфликтов:

1.Структурные конфликты, которые возникают из-за конфликтов по ресурсам, когда аппаратные средства не могут поддерживать все возможные комбинации команд в режиме одновременного выполнения с совмещением.

2.Конфликты по данным, возникающие в случае, когда выполнение одной команды зависит от результата выполнения предыдущей команды.

3.Конфликты по управлению, которые возникают при конвейеризации команд переходов и других команд, которые изменяют значение счетчика команд.

Конфликты в конвейере приводят к необходимости приостановки выполнения команд (pipeline stall). Обычно в простейших конвейерах, если приостанавливается какая-либо команда, то все следующие за ней команды также приостанавливаются. Команды, предшествующие приостановленной, могут продолжать выполняться, но во время приостановки не выбирается ни одна новая команда.

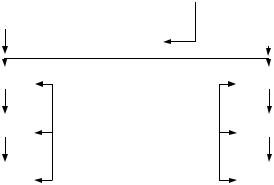

Архитектура двойной независимой шины

Эта архитектура (Dual Independent Bus — DIB) впервые была реализована в процессоре шестого поколения и предназначалась для увеличения пропускной способности шины процессора и повышения производительности. При наличии двух независимых шин данных для ввода-вывода процессор получает доступ к данным с любой из них одновременно и параллельно, а не последовательно, как в системе с одной шиной. Вторая, или фоновая (backside) входная шина процессора с DIB применяется кэшпамятью второго уровня, поэтому она может работать значительно быстрее, чем в том случае, если бы ей пришлось использовать (совместно с процессором) основную шину.

Вархитектуре DIB предусмотрено две шины: шина кэш-памяти второго уровня и шина, соединяющая процессор и основную память, или сис-

темная шина. Процессоры Pentium Pro, Celeron, Pentium II/III, Athlon и Duron могут использовать обе шины одновременно, благодаря чему снижается критичность такого параметра, как пропускная способность шины.

Для реализации архитектуры DIB кэш-память второго уровня перемещена с системной платы в один корпус с процессором, что позволило приблизить быстродействие кэш-памяти второго уровня к быстродействию встроенной кэш-памяти, которое значительно превосходит быстродействие памяти, помещаемой на системную плату. Чтобы поместить кэш в корпус процессора, понадобилось модифицировать гнездо процессора. DIB также позволяет системой шине выполнять одновременно несколько транзакций (а не одну последовательность транзакций), благодаря чему ускоряется поток информации внутри системы и повышается эффективность. Все средства архитектуры DIB повышают пропускную способность почти в три раза по сравнению с процессором, имеющим архитектуру одиночной шины.

SMM

Для быстрых и мощных процессоров портативных компьютеров, Intel разработала схему управления питанием. Эта схема дает возможность про-

81

цессорам экономно использовать энергию батареи и таким образом продлить срок ее службы. Intel впервые реализовала такую возможность в процессоре 486SL, который является усовершенствованной версией процессора 486DX. Впоследствии, когда возможности управления питанием стали более универсальными, их начали встраивать в Pentium и во все процессоры более поздних поколений. Система управления питанием процессоров называется SMM

(System Management Mode - режим управления системой).

SMM физически интегрирована в процессор, но функционирует независимо. Благодаря этому она может управлять потреблением мощности, в зависимости от уровня активности процессора. Это позволяет пользователю определять интервалы времени, по истечении которых процессор будет частично или полностью выключен. Данная схема также поддерживает возможность приостановки/возобновления, которая позволяет мгновенно включать и отключать мощность, что обычно используется в портативных компьютерах. Соответствующие параметры устанавливаются в BIOS.

Технология MMX

Взависимости от контекста, MMX может означать multi-media extensions (мультимедийные расширения) или matrix math extensions (мат-

ричные математические расширения). Технология MMX использовалась в старших моделях процессоров Pentium пятого поколения (Pentium I MMX) качестве расширения, благодаря которому ускоряется компрессия/декомпрессия видеоданных, манипулирование изображением, шифрование и выполнение операций ввода-вывода почти все операции, используемые во многих современных программах.

Вархитектуре процессоров MMX есть два основных усовершенствования. Первое, фундаментальное, состоит в том, что все микросхемы MMX имеют больший внутренний встроенный кэш, чем их собратья, не использующие эту технологию. Это повышает эффективность выполнения каждой программы и всего программного обеспечения независимо от того, использует ли оно фактически команды MMX.

Другое усовершенствование MMX состоит в расширении набора команд процессора 57 новыми командами, а также во введении новой возможности выполнения команд, называемой одиночный поток команд -

множественный поток данных (Single Instruction — Multiple Data, SIMD). SIMD позволяет одной команде осуществлять одну и ту же опера-

цию над несколькими данными, подобно тому как преподаватель, читая лекцию, обращается ко всей аудитории, а не к каждому студенту в отдельности. Технология SIMD позволяет ускорить выполнение циклов при обработке графических, анимационных, видео- и аудиофайлов; в противном случае эти циклы отнимали бы время у процессора.

AMD и Cyrix, лицензировали у Intel технологию MMX и реализовали

еев собственных процессорах.

Инструкции SSE.

В феврале 1999 года Intel представила общественности процессор Pentium III, содержащий обновление технологии MMX, получившей на-

звание SSE (Streaming SIMD Extensions - потоковые расширения SIMD). До

82

этого момента инструкции SSE носили имя Katmai New Instructions (KNI), так как первоначально они были включены в процессор Pentium III с кодовым именем Katmai.

Инструкции SSE содержат 70 новых команд для работы с графикой и звуком в дополнение к существующим командам MMX. Фактически этот набор инструкций имел еще и второе название — MMX-2. Инструкции SSE позволяют выполнять операции с плавающей запятой, реализуемые в отдельном модуле процессора.

Инструкции SSE2, содержащие в себе 144 дополнительные команды SIMD, были представлены в ноябре 2000 года вместе с процессором Pentium 4. В SSE2 были включены все инструкции предыдущих наборов MMX и SSE. Потоковые расширения SIMD (SSE) содержат целый ряд новых команд для выполнения операций с плавающей запятой и целыми числами, а также команды управления кэш-памятью. Новые технологии SSE позволяют более эффективно работать с трехмерной графикой, потоками аудио- и видеоданных (DVD-воспроизведение), а также приложениями распознавания речи. В целом SSE обеспечивает следующие преимущества:

•более высокое разрешение/качество при просмотре и обработке графических изображений; улучшенное качество воспроизведения звуковых и видеофайлов в формате MPEG2,

•одновременное кодирование и декодирование формата MPEG2 в мультимедийных приложениях;

•уменьшение загрузки процессора и повышение точности/скорости реагирования при выполнении программного обеспечения для распознавания речи.

Инструкции SSE и SSE2 особенно эффективны при декодировании файлов формата MPEG2, который является стандартом сжатия звуковых и видеоданных, используемым в DVD-дисках. Следовательно, SSEоснащенные процессоры позволяют достичь максимальной скорости декодирования MPEG2 без использования дополнительных аппаратных средств (например, платы декодера MPEG2). Кроме того, процессоры, содержащие набор инструкций SSE, значительно превосходят предыдущие версии процессоров при распознавании речи.

Одним из основных преимуществ SSE по отношению к MMX является поддержка операций SIMD с плавающей запятой, что очень важно при обработке трехмерных графических изображений. Технология SIMD, как и MMX, позволяет выполнять сразу несколько операций при получении процессором одной команды. В частности, SSE поддерживает выполнение до четырех операций с плавающей запятой за цикл; одна инструкция может одновременно обрабатывать четыре блока данных. Для выполнения операций с плавающей запятой инструкции SSE могут использоваться вместе с командами MMX без заметного снижения быстродействия. SSE также поддерживает упреждающую выборку данных (prefetching), которая представляет собой механизм предварительного считывания данных из кэш-памяти.

Наилучший результат использования новых инструкций процессора обеспечивается только при их поддержке на уровне используемых прило-

83

жений. Графическое приложение Adobe Photoshop поддерживает инструкции SSE, что значительно повышает эффективность использования SSEоснащенных процессоров. Поддержка инструкций SSE встроена в DirectX 6.1 и в самые последние видео- и аудиодрайверы.

Инструкции SSE являются расширением технологий MMX, а SSE2 — расширением инструкций SSE. Таким образом, процессоры, поддерживающие SSE2, поддерживают также инструкции SSE, а процессоры, поддерживающие инструкции SSE, в свою очередь, поддерживают оригинальные команды MMX. Это означает, что стандартные MMX-приложения могут выполняться практически на любых системах.

3DNow и Enhanced 3DNow

Технология 3DNow разработана компанией AMD в ответ на реализацию поддержки инструкций SSE в процессорах Intel. Впервые (май 1998 года) 3DNow реализована в процессорах AMD K6, а дальнейшее развитие — Enhanced 3DNow — эта технология получила в процессорах Athlon

и Duron. Аналогично SSE, технологии 3DNow и Enhanced 3DNow предна-

значены для ускорения обработки трехмерной графики, мультимедиа и других интенсивных вычислений. 3DNow представляет собой набор из 21 инструкции SIMD, которые оперируют массивом данных в виде единичного элемента. В Enhanced 3DNow к существующим добавлены еще 24 новых инструкции. Технологии обработки данных 3DNow и Enhanced 3DNow хоть и подобны SSE, но несовместимы на уровне инструкций, поэтому производителям программного обеспечения необходимо отдельно реализовать поддержку этих технологий.

Технология 3DNow, как и SSE, поддерживает операции SIMD с плавающей запятой, а также позволяет выполнять до четырех операций с плавающей запятой за один цикл. Инструкции 3DNow для операций с плавающей запятой могут использоваться вместе с командами MMX без заметного снижения быстродействия. Поддерживается и упреждающая выборка данных — механизм предварительного считывания данных из кэш-памяти.

Все технологии ускорения обработки данных компаний Intel и AMD реализованы на уровне операционных систем Windows 9x и Windows NT/2000 и старше. Кроме этого, все программные интерфейсы DirectX компании Microsoft и Open GL компании SGI оптимизированы для технологии 3DNow, а практически все современные видеодрайверы 3Dfx, ATI, Matrox и nVidia поддерживают 3DNow и Enhanced 3DNow. Несмотря на то что технология 3DNow поддерживается многими компьютерными играми и драйверами видеоадаптеров, существует ряд профессиональных графических приложений (к их числу относится и Adobe Photoshop), не поддерживающих

3DNow.

Матричныеивекторныепроцессоры

В отличие от скалярных и даже суперскалярных процессоров данные устройства манипулируют массивами данных и предназначены для обработки изображений, матриц и массивов данных. Частным случаем векторного процессора является процессор изображений, который предназначен для обработкисигналов, поступающихотдатчиков-формирователейизображения.

84

Матричный процессор имеет архитектуру, рассчитанную на обработку числовых массивов. Архитектура процессора включает в себя матрицу процессорных элементов, например 64 х 64, работающих одновременно. Постпроцессор предназначен для реализации некоторых специальных функций, например управления базой данных.

Векторный процессор обеспечивает параллельное выполнение операции над массивами данных, векторами. Он характеризуется специальной архитектурой, построенной на группе параллельно работающих процессорных элементов (рис. 4.24, 4.25).

Векторная обработка увеличивает производительность процессора за счет того, что обработка целого набора данных (вектора) производится одной командой. Векторные компьютеры манипулируют массивами сходных данных подобно тому, как скалярные машины обрабатывают отдельные элементы таких массивов. В этом случае каждый элемент вектора надо рассматривать как отдельный элемент потока данных.

Результат С

Операнд А |

Устройство сложения |

|

128-разр. |

||

|

||

|

|

|

Операнд В |

Устройство умножения |

|

128-разр. |

|

|

Обмен |

|

|

Устройство сдвига |

||

данными |

||

|

|

|

|

Логическое устройство |

|

|

|

|

|

|

|

|

Устройство задержки |

Управление

Управление

Рис. 4.24. Векторный процессор Cyber - 205

При работе в векторном режиме векторные процессоры обрабатывают данные практически параллельно, что делает их в несколько раз более быстрыми, чем при работе в скалярном режиме. Максимальная скорость передачи данных в векторном формате может составлять 64 Гбайт/с, что на два порядка быстрее, чем в скалярных машинах.

Кратковременная остановка

Операнд А |

|

|

|

128-разр. |

Управ- |

Срав- |

Вырав- |

|

ление |

нение |

ниваю- |

Операнд В |

поряд- |

||

знаком |

ков |

щий |

|

128-разр. |

|

|

|

|

|

|

Сложение

Счет для |

Сдвиг для |

Обнару- |

Результат С |

нормали- |

нормали- |

жение |

|

конечного |

128-разр. |

||

зации |

зации |

варианта |

|

|

|

|

|

Кратковременная остановка

Рис. 4.25. Архитектура конвейера сложения векторного процессора Cyber-205

85

В настоящее время созданы однокристальные векторно-конвейерные процессоры, такие, как SX-6. Основными компонентами микропроцессора являются скалярный процессор и восемь идентичных векторных устройств, суммарная производительность которых составляет 64 Гфлопс. Примерами систем подобного типа являются, например, процессоры фирм NEC и Hitachi

4.10. Динамическое исполнение (Dynamic execution technology)

Это совокупность технологий обработки данных в процессоре, обеспечивающая более эффективную работу процессора за счет манипулирования данными, а не простого исполнения списка инструкций. Динамическое исполнение представляет собой комбинацию трех методов обработки данных:

•множественное предсказание ветвлений;

•анализ потока данных;

•спекулятивное (по предположению) исполнение. Впервые реализовано в процессоре Pentium Pro.

Множественное предсказание ветвлений. Предсказывается прохо-

ждение программы по нескольким ветвям: процессор может предвидеть разделение потока инструкций, используя алгоритм множественного предсказания ветвлений. С большой точностью (более 90 %) он предсказывает, в какой области памяти можно найти следующие инструкции. Это оказывается возможным, поскольку в процессе исполнения инструкции процессор просматривает программу на несколько шагов вперед. Этот метод позволяет увеличить загруженность процессора.

Хотя ВТВ (Branch Target Buffer — буфер предсказания переходов) и не может правильно предсказать абсолютно все переходы, но большинство предсказаний оказывается точными, что обеспечивает значительное повышение производительности. Например,, программный цикл, состоящий из пересылки, сравнении, сложения и перехода в 80486 DX выполняется за 6 тактов синхронизации, а в Pentium за 2 (команды пересылки и сложения, а также сравнения и перехода сочетаются и предсказывается переход).

Анализ потока данных. Анализирует и составляет график исполнения инструкций в оптимальной последовательности, независимо от порядка их следования в тексте программы. Используя анализ потока данных, процессор просматривает декодированные инструкции и определяет, готовы ли они к непосредственному исполнению или зависят от результата других инструкций. Далее процессор определяет оптимальную последовательность выполнения и исполняет инструкции наиболее эффективным образом.

Спекулятивное выполнение. Повышает скорость выполнения, просматривая программу вперед и исполняя те инструкции, которые необходимы. Процессор выполняет инструкции (до пяти инструкций одновременно) по мере их поступления в оптимизированной последовательности

86

(спекулятивно). Поскольку выполнение инструкций происходит на основе предсказания ветвлений, результаты сохраняются как «спекулятивные». На конечном этапе порядок инструкций восстанавливается и переводится в обычное машинное состояние.

Процессоры уровня IA-64 имеют мощные вычислительные ресурсы, включая 128 регистров целых чисел, 128 регистров действительных чисел, 64 предикационных регистра, а также ряд специальных регистров.

Набор команд оптимизирован для решения задач криптографии, обработки видеосигналов и других процессов, встречающихся в серверах и рабочих станциях.

На рис. 4.26 и 4.27 представлены иллюстрации к возможностям архитектуры IA-64:

•предикация (predication) - одновременное исполнение двух ветвей программы, вместопредсказанияпереходов(выполнениянаиболеевероятного);

•опережающее чтение данных (speculative loading), т. е. загрузка данных в регистры с опережением, до того, как определилось реальное ветвление программы (переход управлений).

Эти возможности осуществляются комбинированно — при компиляции и выполнении программы.

1. Ветвление может иметь два |

|

Команда 1 |

|

|

|

2. Компилятор назначает для каждой |

|

|

||||||||||

исхода |

|

|

|

|

|

|

|

|

ветви регистр (Р1, Р2) (или «буфер пред- |

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

3. Все команды этой ветви |

|

|

Команда 2 |

|

|

|

выборки» - predicate register) |

|

|

|||||||||

помещаются в регистр Р1 |

|

|

|

|

|

|

|

|

|

|

4. Все команды данной ветви по- |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

Команда 3 |

|

|

|

|

|

мещаются в регистр Р2 |

|

|||||

|

|

|

|

|

|

|

перехода |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Команда 4 |

|

|

5. ЦП начинает выполнять обе |

|

|

Команда 7 |

|

|

|

||||||||

|

(P1) |

|

|

|

|

(P2) |

|

|

|

|||||||||

|

|

|

ветви параллельно, так как |

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

вычисления независимы |

|

|

|

|

|

|

||||||||

|

Команда 5 |

|

|

|

|

Команда 8 |

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

(P1) |

|

|

|

|

|

|

|

|

|

|

|

|

|

(P2) |

|

|

|

|

|

|

|

6. |

Когда |

становится |

известен |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|||||||||

|

Команда 6 |

|

|

|

|

Команда 9 |

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

(P1) |

|

|

реальный |

исход ветвления, |

|

|

(P2) |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Компилятор может подготовить параллельную обработку, переставив команды и сочетая инструкции 4 и 7, 5 и 8, 6 и 9

для одновременного выполнения

Рис. 4.26. Предикация или одновременное предварительное выполнение всех ветвей оператора условного перехода

Предикация — центральный метод планирования параллельной обработки. Компилятор транслирует операторы исходного кода, содержащие ветвление (условный переход), в совокупность блоков машинных команд, идущих друг за другом. Обычный процессор, в зависимости от исхода условия, исполняет один из этих базовых блоков, пропуская все другие. Более развитые процессоры пытаются прогнозировать исход операции перехода и заранее (спекулятивно, по предположению) выполняют один из блоков, теряя время при ошибке прогнозирования.

87

1. Компилятор сканирует исходную программу |

|

|

|

|

2. В момент исполнения программы эта команда |

|

||||||||||

Команда 1 |

|

|||||||||||||||

|

|

|

считывает данные, которые могут понадобиться |

|

||||||||||||

и обнаруживает чтение данных (команда 8, |

|

|

|

|

|

|||||||||||

после перехода). Она удаляется. Помещается |

|

|

|

|

в одной из ветвей |

|

|

|

||||||||

Команда 2 |

|

|

|

|

||||||||||||

опережающее чтение перед переходом. После |

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||

перехода вставляется проверка. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

Чтение с |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

опережением |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

5. Реально команда чтения вы- |

|||||||||

|

|

|

|

|

Команда 3 |

|

полняется перед |

ветвлением |

||||||||

|

|

|

|

|

перехода |

|

программы |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Команда 4 |

|

|

3. Если исполнение идет по данной ветви, |

|

|

|

|

Команда 7 |

|

|

|||||

|

|

|

|

то поскольку данные уже считаны, команда |

|

|

|

|

|

|

||||||

|

|

|

|

8 реально выполняться не будет |

|

|

|

|

|

|

|

Команда 8 |

|

|||

|

Команда 5 |

|

|

|

|

|

|

|

|

|

|

|

|

(чтение) |

|

|

|

|

|

|

4. Проверка действительности считанного |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

данного |

|

|

|

|

|

|

|

|

|

|

|

|

|

Команда 6 |

|

|

|

|

|

|

|

|

|

|

Команда |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

проверки |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Команда 9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(обработка) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 4.27. Опережающее считывание данных в регистр из памяти (speculative loading)

Базовые блоки обычно малы (2-3 команды) и ветвление встречается в среднем через каждые шесть операторов языка программирования. Поэтому выигрыш оказывается небольшим.

Когда компилятор уровня IA-64 обнаруживает оператор ветвления в исходной программе, он анализирует все возможные ветви (блоки) и помечает их метками или предикатами (predicate). После этого он определяет, какие из них могут быть выполнены параллельно (из соседних, независимых, ветвей).

Затем компилятор группирует машинные коды в 128-битовые связки (bundles), по 3 команды в каждой. В описания связок (template) заносится информация о том, какие команды могут исполняться параллельно (независимо). Например, если компилятор находит 16 команд, которые не имеют взаимной связи, он укладывает их в 6 независимых связок (по 3 в первых 5 и одна в 6-й) и помечает их в описании.

В процессе выполнения программы ЦП просматривает описания связок, выбирает команды, которые взаимно независимы и распределяет их на параллельную обработку. Если ЦП обнаруживает оператор ветвления, он не пытается предсказать переход, а начинает выполнять все возможные ветви программы.

Таким образом, могут быть обработаны все ветви программы, но без записи полученного результата. В определенный момент процессор наконец «узнает» о реальном исходе условного оператора, записывает в память результат «правильной ветви» и отменяет остальные результаты.

88

Опережающее чтение (по предположению) разделяет загрузку данных в регистры и их реальное использование, избегая ситуации, когда процессору приходится ожидать прихода данных, чтобы начать их обработку.

Прежде всего, компилятор анализирует программу, определяя команды, которые требуют приема данных из оперативной памяти. Там, где это возможно, он вставляет команды опережающего чтения и парную команду контроля опережающего чтения (speculative check). В то же время компилятор переставляеткомандытакимобразом, чтобыЦПмогихобрабатыватьпараллельно.

В процессе работы ЦП встречает команду опережающего чтения и пытается выбрать данные из памяти. Может оказаться, что они еще не готовы (результат работы блока команд, который еще не выполнился). Обычный процессор в этой ситуации выдает сообщение об ошибке, однако система уровня IA-64 откладывает «сигнал тревоги» до момента прихода процесса в точку «команда проверки опережающего чтения». Если к этому моменту все предшествующие подпроцессы завершены и данные считаны, то обработка продолжается, в противном случае вырабатывается сигнал прерывания.

4.11 Технология Hyper-Threading. Многоядерность.

Из предыдущих параграфов следует, что основным способом повышения производительности процессора является увеличение его тактовой частоты. Это направление встречает ряд ограничений первое обусловлено конечность скорости света 3*108 м/с, которое ограничивает минимальное время передачи информации. Второе: при сегодняшних технологических нормах производства процессоров и малоэффективных воздушных системах охлаждения добиться линейного масштабирования тактовой частоты процессоров не удаётся. Общепринято отождествлять производительность процессора со скоростью выполнения им инструкций программного кода. Производительность (Performance) - это отношение общего числа выпол-

ненных инструкций программного кода ко времени их выполнения:

Производительность = Количество инструкций Время выполнения

В этом смысле производительность процессора отождествляется с количеством инструкций, выполняемых за секунду (Instructions rate). А поскольку одной из важных характеристик процессора является его тактовая частота, то желательно именно с ней связать производительность процессора. Это можно сделать, если количество инструкций, выполняемых за единицу времени, рассматривать как произведение количества инструкций, выполняемых за один такт процессора (Instruction Per Clock, IPC), на количество тактов процессорав единицу времени (тактовая частота процессора):

Производительность = |

Количество инструкций |

· |

Количество тактов |

|

Количество тактов |

||||

|

|

Время выполнения |

||

|

IPC |

|

Частота |

89

Количество тактов процессора в единицу времени – это и есть его тактовая частота (Frequency). Таким образом, производительность процессора зависит в равной степени и от его тактовой частоты, и от количества инструкций, выполняемых за такт (IPC):

Производительность = IPC · Частота

Последняя формула, по сути, определяет два разных подхода к увеличению производительности процессора, первый из которых связан с увеличением тактовой частоты процессора, а второй – с увеличением количества инструкций программного кода, выполняемых за один такт процессора. Вполне очевидно, что увеличение тактовой частоты не может быть бесконечным и определяется технологией изготовления процессора. При этом рост производительности не является прямо пропорциональным росту тактовой частоты, то есть наблюдается тенденция насыщаемости, когда дальнейшее увеличение тактовой частоты становится нерентабельным. Количество инструкций, выполняемых за время одного такта, зависит от микроархитектуры процессора: от количества исполняемых блоков, от длины конвейера и эффективности его заполнения, от блока предвыборки и т.д., а кроме того, естественно, от оптимизации программного кода к данной микроархитектуре процессора. Поэтому вполне корректным является сравнение производительности процессоров на основании их тактовой частоты в пределах одной и той же микроархитектуры (при одинаковом значении IPC процессоров) и некорректно сравнение производительности процессоров с различной микроархитектурой исключительно на основе тактовой частоты. К примеру, основываясь на тактовой частоте, некорректно сравнивать производительность процессоров с разным размером L2-кэша или производительность процессоров, поддерживающих и не поддерживающих технологию Hyper-Threading.

Другим подходом к увеличению производительности процессорной подсистемы, типичным для серверных решений, является использование многопроцессорных SMP-конфигураций. В этом случае достигается параллельное (Thread Level Parallelism, TLP) и в какой-то мере независимое решение нескольких разных задач или нескольких потоков одной задачи на нескольких процессорах, что, естественно, сопровождается приростом общей производительности вычислительной подсистемы сервера. Впрочем, ожидать адекватного количеству процессоров роста производительности и в данном случае не приходится — многое зависит от типа решаемых задач, от реализации в серверной операционной системе поддержки SMP. Всегда можно найти такое приложение, которое в двухпроцессорной конфигурации будет показывать результаты ниже, чем в однопроцессорной, и потому любой «талантливый» программист вполне сможет свести на нет все преимущества многопроцессорной архитектуры.

Между тем, кроме перечисленных способов увеличения общей производительности процессорной подсистемы, существуют технологии, по-

90