- •Введение

- •1. Производство Интегральных Схем на современном этапе

- •2. Основы технологии производства Интегральных Схем

- •3. Библиотеки топологических элементов. Резисторы и конденсаторы

- •4. Библиотеки топологических элементов. Моп-транзисторы

- •5. Библиотеки топологических элементов. Биполярные транзисторы

- •6. Понятие топологии. Цели и задачи топологического проектирования

- •7. Проектирование топологии аналоговых схем

- •8. Обзор коммерческих фабрик по производству Интегральных схем

- •Заключение

- •Библиографический список

- •Оглавление

- •394026 Воронеж, Московский просп., 14

7. Проектирование топологии аналоговых схем

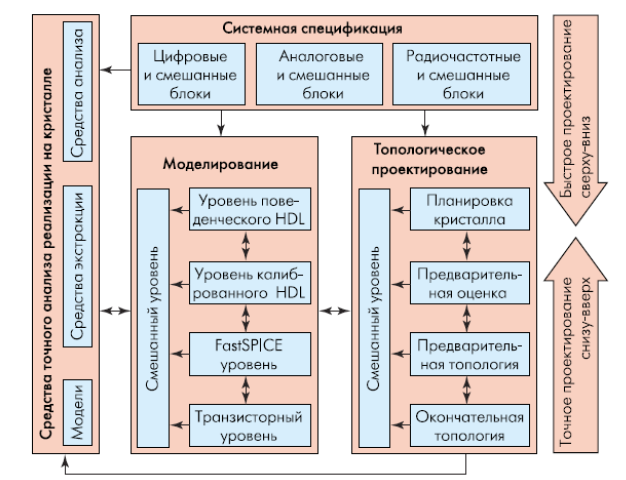

Существующие системы автоматизированного проектирования заказных СБИС формировались в рамках традиционных методологий проектирования. Изначально в них поддерживалась методология проектирования «снизу-вверх», при которой сначала создаются низкоуровневые ячейки, потом блоки и схемы, которые в конечном счете объединяются в целый кристалл. Впоследствии, когда сложность разработок возросла, стал активно развиваться подход «сверху-вниз», при котором проект начинается с создания полной поведенческой модели системы. Связано это с тем, что процесс проектирования снизу-вверх, хотя и обеспечивает возможность учета всех особенностей реализации компонентов схемы на кристалле,- слишком медленный. К тому же в больших проектах на стадии разработок ячеек трудно предвидеть проблемы общесистемного уровня. В то же время при работе сверху-вниз более-менее точная информация о конкретной реализации компонентов схемы часто появляется слишком поздно. Такой подход вполне приемлем для чисто цифровых устройств, но для сложных заказных схем, в силу влияния физических эффектов (например электромиграция, шумы, индуктивность и т.д.), на последней стадии может оказаться, что проект полностью неработоспособен.

При проектировании заказных СБИС предпочтительно объединять оба этих подхода, взяв от первого доступ к точной информации о реализации компонентов схемы на кристалле, а от второго – эффективность и возможность высокоуровневой верификации. Проектирование должно идти одновременно сверху-вниз и снизу-вверх так, чтобы в промежуточной точке, когда оба этих процесса состыкуются, получился оптимальный результат. Такая «meet-in-the-middle» методология представляется наиболее разумной и перспективной при проектировании современных заказных систем на кристалле. Иллюстрация этого подхода представлена на рис. 7.1.

Рис. 7.1. Подход «meet-in-the-middle»

Обеспечение идентичности (matching) элементов ИС с учетом фактора технологического разброса параметров на пластине

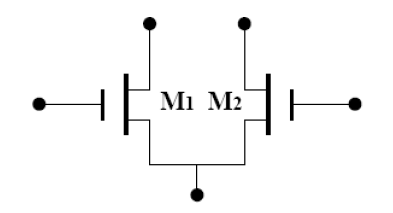

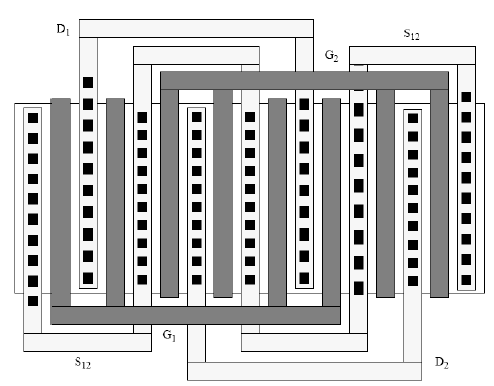

В ходе проведения технологического процесса из-за несовершенства оборудования, погрешностей в ходе проведения технологических операций, а также из-за внутренних и внешних электрических полей в пластине возникает разброс технологических параметров (как правило, параметры кристаллов, расположенных в центре пластины наиболее приближенны к ожидаемым). Поэтому, даже на одном кристалле, располагаясь на некотором расстоянии друг от друга резисторы, конденсаторы и транзисторы с одинаковыми физическими размерами могут иметь незначительные расхождения в параметрах (например, из-за разности толщины подзатворного диэлектрика, уровня легирования и т.д.). При проектировании цифровых блоков, этот технологический разброс повлиять на уровень логического «0» или «1» не сможет. Однако, в аналоговой схеме дело обстоит иначе – даже незначительное расхождение в параметрах может привести к неработоспособности схемы. Например, несущественно разнящаяся дифференциальная пара транзисторов в операционном усилителе приведет к значительному изменению выходного напряжения. Поэтому при проектировании аналоговых блоков для увеличения идентичности (matching) элементов ИС применяют следующие приемы. На рис. 7.2 показана схема дифференциальной пары транзисторов, а на рис. 7.3 показа их топология с центральной симметрией. G1, G2 – затворы соответственно первого (М1) и второго (М2) транзисторов, D1, D2 – стоки транзисторов М1 и М2, S12 – общий исток транзисторов М1 и М2.

Рис.7.2. Схема дифференциальной пары транзисторов

Рис.7.3. Топология дифференциальной пары транзисторов

с центральной симметрией

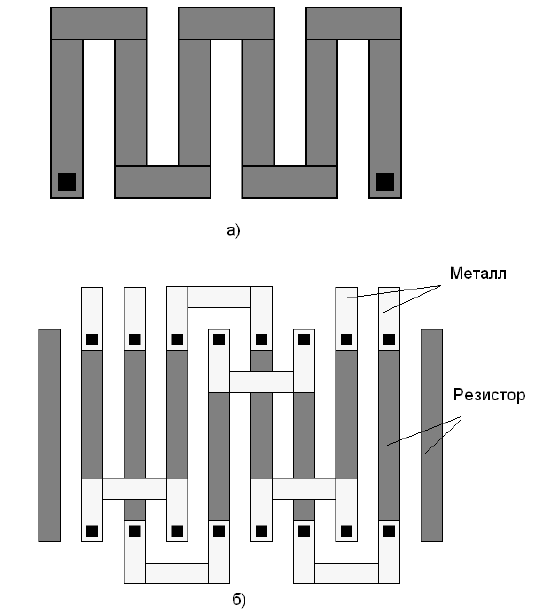

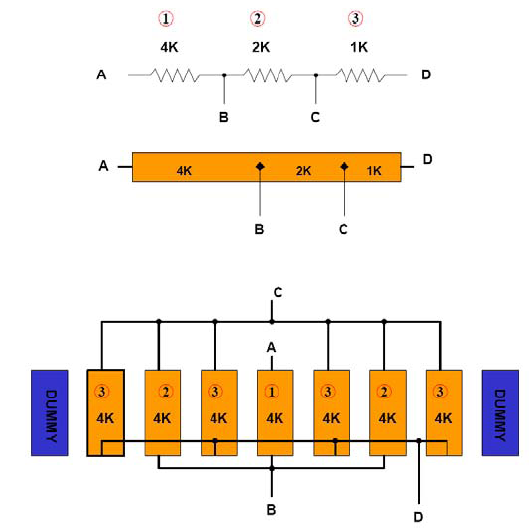

На рис. 7.4,а изображен обычный резистор, а на рис.7.4,б показана реализация двух идентичных резисторов с соблюдением условия максимального совпадения параметров.

Рис. 7.4. а) Топология резистора;

б) топология двух идентичных резисторов

В случае если резисторы имеют разное номинальное сопротивление целесообразно выполнить их наборными на основе минимального резистора (рис. 7.5).

Слева и справа от тела рабочего резистора располагают так называемые DUMMY-резисторы, которые не несут функциональной нагрузки с точки зрения схемотехники (не подключены) и используются как своеобразный экран, в том числе и от наводок от проходящих рядом шин.

Аналогичным образом дело обстоит и с конденсаторами (рис. 7.6).

Рис. 7.5. Схема расположения резисторов с разными номиналами для большего совпадения параметров

Рис. 7.6. Схема и топология нескольких конденсаторов, оптимально размещенных сточки зрения идентичности параметров

Для исключения краевых эффектов обкладки конденсаторов срезаются под углом 45°.

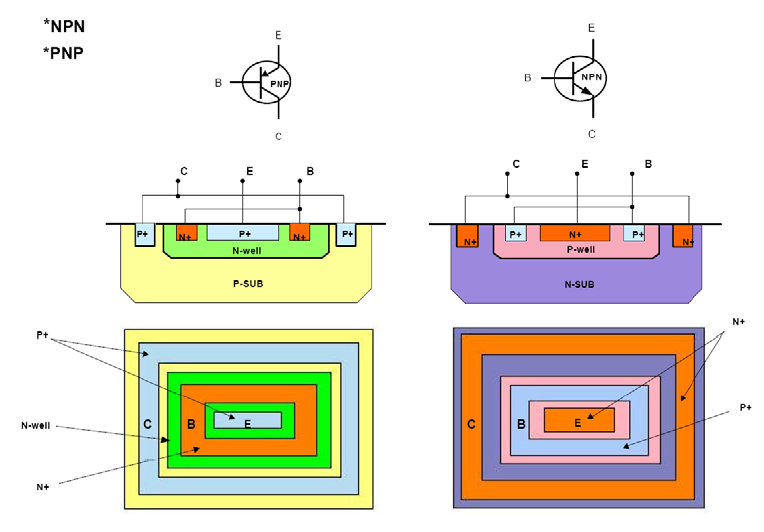

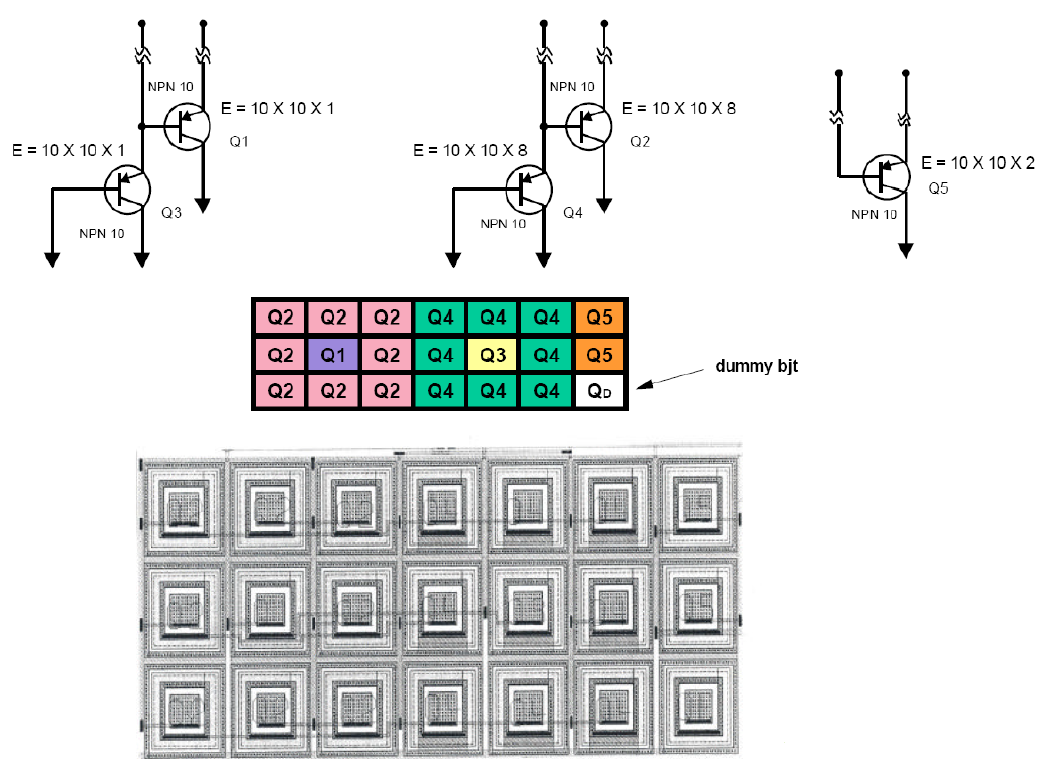

На рис. 7.7 показаны фрагменты сечения и топология биполярных n-p-n и p-n-p-транзисторов, а на ри. 7.8 их оптимальное размещение.

Рис. 7.7. Фрагменты сечения и топология биполярных

n-p-n и p-n-p- транзисторов

Рис. 7.8. Оптимальное размещение пяти n-p-n транзисторов

с разным количеством эмиттеров

Главная цель разработки топологии ИС заключается в эффективном использовании площади кристалла. Однако необходимо учитывать, что характеристики ИС, в частности, динамические, сильно зависят от паразитных емкостей и сопротивлений, определяемых топологией. Поэтому необходимо принимать компромиссные решения, которые учитывали бы оптимальное использование площади и получение хороших характеристик ИС.

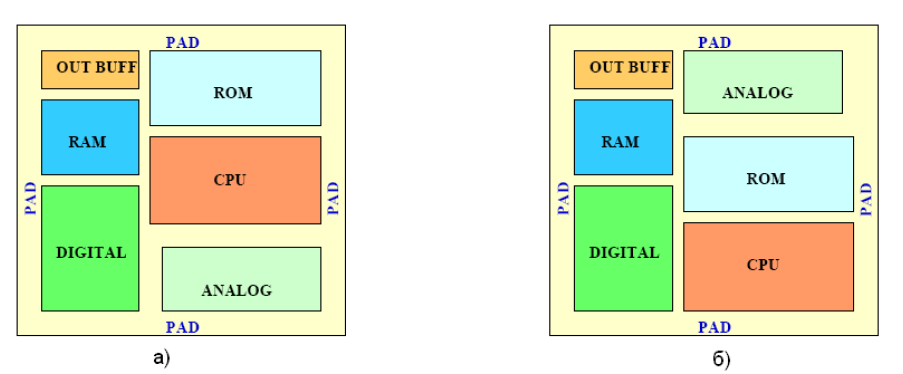

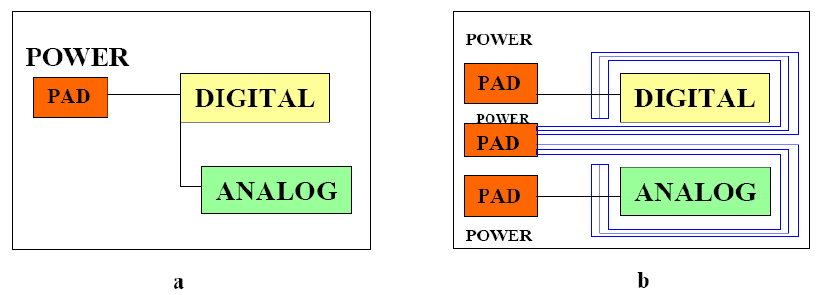

При планировании места на кристалле и размещении блоков для исключения влияния цифровых шумов на аналоговые блоки следует располагать их максимально удаленно друг от друга (рис. 7.9).

Рис.7.9. Расположение цифровых и аналоговых блоков на кристалле а) не верно б) верно

Также для изоляции цифровых и аналоговых блоков друг от друга необходимо использовать различные «земли» и «питания» (с разных PAD-площадок), а также окружать их кольцами из шин дополнительного «питания» (рис. 7.10).

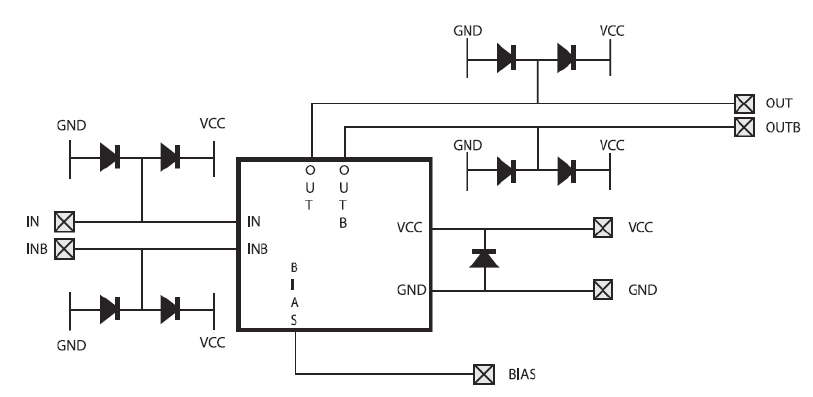

Все входы и выходы ИС должны быть защищены от электростатических разрядов обратно смещенными диодами (рис. 7.11).

Рис. 7.10. Разводка шин питания в цифро-аналоговых схемах

а) не верно; б) верно

Рис. 7.11. Защита от электростатических разрядов