Разработка и прототипирование цифровых устройств на языках VHDL и Verilog. Барабанов В.Ф., Гребенникова Н.И

.pdf

Теперь можно выбрать устройство ПЛИС в списке устройств JTAG цепи и запрограммировать его, нажав кнопку

Program (рис. 2.15).

Рис. 2.15. Выбрать устройства ПЛИС в списке устройств

JTAG

Дождитесь окончания процесса загрузки. После этого можно протестировать работоспособность устройства (рис. 2.16).

31

Рис. 2.16. Тестирование работоспособности устройства

2.3.Задание на лабораторную работу

1.Разработать модель цифровой схемы на языках Verilog HDL и VHDL согласно выбранному варианту. Модель должна быть разработана с использованием иерархического описания.

2.Разработать тестовую оболочку для полученной

модели.

3.Провести тестирование разработанной модели с использованием отладочного комплекта Spartan 3 Starter Kit.

32

Варианты заданий.

Задание необходимо выполнить в соответствии с вариантом, выбранным для первой лабораторной работы.

2.4. Требования к отчету по лабораторной работе

Отчет должен содержать следующую информацию по лабораторной работе:

название работы, цель и задание, согласно варианту;

код описания модели цифрового устройства;

временные диаграммы работы полученной модели.

33

3. ЛАБОРАТОРНАЯ РАБОТА № 3 РАЗРАБОТКА ЦИФРОВЫХ УСТРОЙСТВ С ПАМЯТЬЮ

3.1. Цель работы

Целью данной лабораторной работы является получение навыков разработки и тестирования цифровых устройств с элементами памяти (D-Триггерами).

3.2. Краткие теоретические сведения

При проектировании цифровых устройств широко используются D-триггеры – специальные логические элементы, которые способны запоминать информацию, поданную им на вход. Каждый такой триггер может запомнить один бит информации.

Условное графическое изображение D-Триггера представлено на рис. 3.1.

Рис. 3.1. D-триггер с асинхронным сбросом и установкой

Данные с входа записываются на выход D-триггера синхронно с фронтом тактового сигнала, приходящего на вход C. Таким образом, синхронно с каждым импульсом тактовой частоты схема переходит из одного устойчивого состояния в другое. Состояние всей схемы определяется текущими значениями в триггерах.

Для того чтобы поведение схемы было предсказуемым, необходимо произвести начальную установку значений триггеров. Для этого используются входы S(SET) и R(RESET).

34

Выходное значение триггера сбрасывается в 0 нулевым значением сигнала R, либо устанавливается в 1 нулевым значением сигнала S (в случае триггера с асинхронным сбросом – это происходит независимо от текущего состояния тактового входа С).

3.3.Задание на лабораторную работу

1.Разработать модели цифровой схемы на языках Verilog HDL и VHDL согласно выбранному варианту.

2.Разработать тестовую оболочку для полученных моделей. При тестировании произвести начальную установку триггеров схемы. Отобразить временные диаграммы сигналов на всех точках схемы, отмеченных в задании (y, y1, y2 и т.д.).

Варианты заданий.

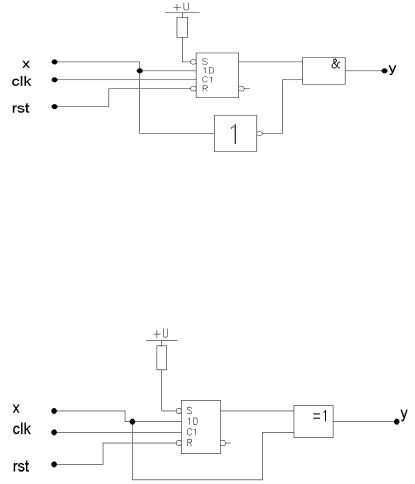

Вариант 1

Примечание: на временной диаграмме требуется отобразить реакцию данной цифровой схемы на импульсный сигнал, поданный на вход X. Длительность импульса данного сигнала должна быть не менее двух периодов тактовой частоты, использованной для тактирования схемы.

35

Вариант 2

Примечание: на временной диаграмме требуется отобразить реакцию данной цифровой схемы на импульсный сигнал, поданный на вход X. Длительность импульса данного сигнала должна быть не менее двух периодов тактовой частоты, использованной для тактирования схемы.

Вариант 3

Примечание: на временной диаграмме требуется отобразить реакцию данной цифровой схемы на импульсный сигнал, поданный на вход X. Длительность импульса данного сигнала должна быть не менее трех периодов тактовой частоты, использованной для тактирования схемы.

36

Вариант 4

Вариант 5

Вариант 6

37

Вариант 7

Вариант 8

Вариант 9

38

Вариант 10

Вариант 11

Вариант 12

39

3.4. Требования к отчету по лабораторной работе

Отчет должен содержать следующую информацию по лабораторной работе:

название работы, цель и задание, согласно варианту;

код описания модели цифрового устройства;

временные диаграммы работы разработанной модели.

40