Управление памятью в современных операционных системах. Савинков А.Ю

.pdfНачальный адрес таблицы отображения (ее еще называют таблица трансляции) заносится в специальный регистр процессора. При переключении процессов и соответствующей смене ВАП операционная система меняет содержимое этого регистра, задавая новое правило отображения виртуальных адресов в физические.

Заметим, что если использована страничная модель ВАП и размер страницы кратен 2 , где - целое число, то на поле смещения в виртуальном адресе должно содержать бит. При этом может быть указано смещение в диапазоне [0,2 − 1], т.е. выход за границу страницы в принципе не возможен.

Метод прямого отображения требует минимальной аппаратной поддержки со стороны процессора, но недостаточно производителен.

Причина низкой производительности метода прямого отображения заключена в том, что таблица отображения находится в ОЗУ. В результате для каждого обращения к данным в памяти необходимо выполнять дополнительное обращение к памяти для получения данных из таблицы. Для современных процессоров обращение к памяти является медленной операцией, за время которой может быть выполнено множество операций над данными в процессорном кэше и регистрах. Поэтому применение прямого отображения в современных процессорах привело бы к катастрофической потере производительности.

3.2.2. Метод ассоциативного отображения

Производительность подсистемы трансляции адресов можно существенно повысить, если перенести

41

таблицу отображения непосредственно в процессор, как показано на рис. 10.

виртуальный адрес

номер блока

ассоциативная таблица отображения (расположена в процессоре)

смещение внутри блока

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

У |

|

|

) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

О |

З |

О |

З |

У |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

с |

в |

в |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

е |

е |

н |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

др |

ж |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

ий |

а |

ра |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

об |

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

к |

т |

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

о |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

ч |

е |

с |

о |

к |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

зи |

л |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

и |

б |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

ф |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

л |

и |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

ес |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

( |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 10. Метод ассоциативного поблочного отображения

Поскольку данные для преобразования виртуальных адресов в физические расположены в процессоре, исключаются лишние обращения к памяти и связанные с этим потери производительности.

Заметим, что таблица трансляции адресов в процессоре, с учетом возможностей реализации, может содержать ограниченное, не очень большое, количество ячеек. Поскольку виртуальное адресное пространство процесса может содержать миллионы блоков, одновременно разместить в процессоре данные для трансляции адресов всех блоков ВАП в большинстве случаев невозможно.

Операционная система может записать в любую ячейку таблицы трансляции адресов информацию о соответствии виртуального и физического адреса любого блока в ВАП. Если программа выполнит обращение по виртуальному адресу из блока, представленного в таблице

42

трансляции адресов процессора, процессор выполнит преобразование виртуального адреса в физический и обращение к ОЗУ. В противном случае процессор вызовет исключение, которое должно быть обработано операционной системой.

Операционная система должна будет определить с чем связано исключение: с отсутствием информации в таблице трансляции адресов процессора при наличии требуемого блока данных в ОЗУ или с отсутствием требуемых данных в ОЗУ. В первом случае операционная система должна быстро заменить содержание одной из ячеек в таблице трансляции адресов, после чего программа сможет продолжить работу. Во втором случае необходимо будет блокировать процесс и переносить данные в ОЗУ из вторичной памяти, как уже было рассмотрено.

Для минимизации числа отказов при трансляции адресов операционная система должна стремиться размещать в таблице трансляции адресов процессора записи о наиболее часто используемых блоках данных.

При переключении процессов операционная система должна полностью обновить все записи в таблице трансляции адресов процессора, чтобы перейти в другое ВАП.

Поскольку таблица трансляции адресов в процессоре содержит информацию только о части блоков виртуального адресного пространства, причем априорно не известно о каких именно, нельзя прямо сопоставить номер блока виртуального адресного пространства с номером записи в таблице трансляции адресов, как это делалось при прямом отображении. Теперь при каждой попытке трансляции адреса процессор должен просматривать всю таблицу трансляции адресов, чтобы найти необходимое ему соответствие между виртуальным и физическим

43

адресом или обнаружить отсутствие нужной информации. Хранилище данных, которое ведет поиск данных не по номеру ячейки в хранилище, а по содержимому самих данных, называется ассоциативный массив. Поэтому рассмотренный метод трансляции адресов называется

ассоциативное отображение.

Возможность эффективной работы системы трансляции адресов по методу ассоциативного отображения при размещении в таблице трансляции процессора информации только о некоторой части блоков ВАП, обосновывается локализацией ссылок при обращении к памяти. Действительно, если наблюдается локализация при обращении к отдельным адресам в виртуальном адресном пространстве, как было рассмотрено ранее, то будет наблюдаться локализация и при обращении к блокам памяти, причем даже в большей степени. Начав работать с адресами внутри некоторого блока, программа еще долго будет обращаться к одному и тому же блоку, значит можно применить известный принцип кэширования при обращении к данным таблицы трансляции адресов.

Реализация ассоциативного отображения в процессоре с технической точки довольно проста, но для эффективной работы требует от операционной системы выполнения дополнительных действий по выявлению наиболее вероятно используемых блоков данных в ВАП каждого процесса и поддержанию ассоциативной таблицы трансляции адресов процессора в актуальном состоянии.

3.2.3. Метод комбинированного отображения

Метода комбинированного поблочного отображения объединяет преимущества рассмотренных

44

методов прямого и ассоциативного отображений. Идея метода комбинированного поблочного отображения поясняется на рис. 11.

Метод комбинированного поблочного отображения может рассматриваться как модификация метода прямого отображения. Он работает следующим образом. В процессоре реализуется небольшая (от нескольких десятков до нескольких тысяч записей) ассоциативная таблица, выполняющая роль кэша при трансляции адресов.

Она обычно называется ассоциативный буфер трансляции

или TLB (Translation Lookaside Buffer) Всякий раз, при трансляции адреса быстро проверяется, не содержится ли нужная информация в TLB. Если содержится, то обращение к таблице трансляции адресов в ОЗУ не выполняется и используются данные из TLB. Если же нет, то выполняется обращение к таблице трансляции адресов в ОЗУ и полученные данные сохраняются в TLB. При последующих обращениях к тому же блоку, а такие обращения весьма вероятны из-за локализации ссылок, трансляция адреса будет выполнена максимально быстро за счет TLB.

Благодаря TLB, ожидаемые потери производительности из-за трансляции виртуальных адресов будут невелики, на уровне метода ассоциативного отображения. При этом операционная система освобождается от управления кэшированием данных для трансляции адресов.

45

виртуальный адрес

начальный адрес таблицы (своя таблица для каждого ВАП)

|

|

|

|

|

номер блока |

смещение внутри блока |

|

|

|

|

|

|

си |

ассоциативная таблица |

|

|

|

|

|

пи |

|

|

|

|

ерза |

|

|

|

|||

м |

|

|

|

е |

|

(TLB) в процессоре |

|

раз |

|

|

|

|

|

||

|

|

|

иц |

|

|

||

|

|

бл |

|

|

|

|

|

вта |

|

|

|

|

|

||

таблица отображения |

|

|

|||||

|

(расположена в ОЗУ) |

|

|

||||

|

|

|

|

|

|

|

селектор |

|

|

|

|

|

|

|

физический адрес в ОЗУ |

|

|

|

|

|

|

|

(если блок отображен в ОЗУ) |

Рис. 11. Метод комбинированного поблочного отображения

46

3.2.4. Таблица трансляции адресов

Рассмотрим страничную организацию ВАП. Все страницы ВАП последовательно нумеруются, при этом номер страницы виртуального адресного пространства прямо соответствует номеру записи (ячейки) в таблице трансляции. Таким образом, таблица трансляции адресов должна содержать столько же записей, сколько страниц в виртуальном адресном пространстве. На практике число страниц в ВАП может быть весьма значительным, что создает определенные трудности при практической реализации таблиц трансляции адресов. Например, типичный размер страницы в виртуальной памяти 4 КБ, размер 32-битного виртуального адресного пространства 4 ГБ, следовательно, в адресном пространстве укладывается миллион страниц, и таблица трансляции должна содержать миллион записей. Даже если запись занимает 4 Б, таблица из миллиона записей займет 4 МБ ОЗУ, причем такая таблица нужна для каждого запущенного процесса, а их число может измеряться сотнями и тысячами. Очевидно, что реализация таблицы трансляции адресов «в лоб» приведет к слишком большим потерям ОЗУ, поэтому в реальных процессорах применяют многоуровневые структуры таблиц трансляции адресов, позволяющие эффективно хранить разреженные данные. Таблицы трансляции адресов реальных процессов будут разреженными, поскольку большинство процессов используют только малую часть из доступного им ВАП (малую часть страниц из доступного миллиона страниц) и большинство записей таблицы трансляции адресов будут пустыми, следовательно, их можно не хранить.

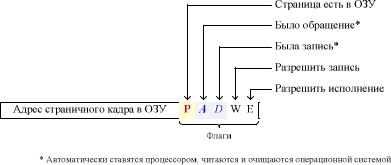

Каждая запись таблицы трансляции адресов одержит адрес страничного кадра, на который отображается данная страница ВАП и несколько флагов. Точная структура этой

47

записи определяется архитектурой процессора, но есть несколько общих моментов, которые можно отметить.

Запись таблицы трансляции адресов, содержащая типичные флаги, показана на рис. 12 (в реальной записи флагов может быть больше).

Рис. 12. Запись таблицы трансляции адресов

Основной флаг, с точки зрения трансляции адресов,

это флаг P (Present) – флаг присутствия. Если он установлен, то данная страница имеет сопоставление со страничным кадром в ОЗУ и преобразование виртуального адреса в физический имеет смысл. Данный флаг может не использоваться в системе трансляции адресов на основе метода ассоциативного отображения, поскольку само присутствие записи в ассоциативной таблице процессора служит индикатором присутствия данных в ОЗУ. Во всех остальных случаях флаг присутствия необходим. Если в процессе трансляции адреса процессор обнаруживает, что флаг P не установлен, то процессор прекращает обращение к памяти и генерирует исключение, известное как страничная ошибка (page fault). Флаг P устанавливается и очищается операционной системой при перемещении данных между ОЗУ и диском.

48

Флаг A (Access) – флаг обращения. Он не является обязательным, но поддерживается большинством процессоров. Этот флаг автоматически выставляется процессором, если он выполнил обращение к данным соответствующей страницы. Операционная система использует этот флаг для выявления страниц, которые больше не используются программами и могут быть выгружены на диск

Флаг D (Dirty) – флаг модификации. Как и флаг A, он не является обязательным, но поддерживается многими процессорами. Этот флаг автоматически выставляется процессором, если он выполнил модификацию данных соответствующей страницы. Операционная система использует этот флаг для выявления страниц, содержимое которых не изменялось после загрузки в ОЗУ с диска. Учет таких страниц позволяет оптимизировать замещение страниц.

Флаг W (Write) – флаг разрешения записи. Он не является обязательным, но поддерживается большинством процессоров. Этот флаг устанавливает и очищает операционная система с целью разрешения или запрета записи данных страницы. Используется для защиты данных в памяти от случайного повреждения или целенаправленной модификации.

Флаг E (Executive) – флаг разрешения выполнения.

Он не является обязательным, но поддерживается большинством процессоров. Этот флаг устанавливает и очищает операционная система с целью разрешения или запрета выполнения программы, содержащейся в странице. Используется для защиты, чтобы предотвратить возможность выполнения массивов данных как программ. Злоумышленник может разместить код вредоносной программы в памяти под видом обычных данных (например,

49

используя ошибку переполнения буфера) и попытаться выполнить ее. Использование флага E исключает такую возможность.

3.3. Замещение в виртуальной памяти

Виртуальная память представляет собой частный случай иерархической памяти, содержащей два уровня. Для нее, как и для любой многоуровневой памяти, необходимо решать задачи выборки, размещения и замещения данных. При этом задачи выборки и размещения могут быть решены относительно просто. Выборка по требованию легко реализуется за счет использования исключений страничная ошибка, размещение при использовании страничной модели, когда все размещаемые блоки имеют одинаковый размер, выполняется тривиально. Решение же задачи замещения требует отдельного анализа.

Как было отмечено ранее, оптимальная стратегия замещения должна выгружать на нижележащий уровень данные, к которым дольше всего не будет обращений, но данная стратегия является нереализуемой, поскольку будущие обращения к памяти достоверно не известны.

На практике, в системах виртуальной памяти находят применение различные неоптимальные дисциплины замещения, отличающихся сложностью реализации, требованиями к аппаратной поддержке со стороны процессора и с разной степенью близости к оптимальной реализации, в том числе основанные на замещении случайно выбранной страницы или на замещении самой старой страницы. Но наибольший интерес представляют подходы, основанные на анализе истории обращений к памяти, которые позволяют добиться большей степени приближения к оптимальной стратегии, но требуют аппаратной

50