- •Министерство общего и профессионального образования российской федерации

- •Учебное пособие Воронеж 2000

- •Учебное издание

- •394026 Воронеж, Московский поспект, 14

- •1. Тестовое диагностирование в цифровой технике:

- •1.1. Введение

- •1.2. Тестовое диагностирование в цифровой технике: цепи и терминология

- •1.3. Процедуры и проблемы программного тестирования

- •1.4. Необходимость проектирования тестопригодных схем

- •2. Анализ тестопригодности: система camelot

- •2.1. Количественная оценка тестопригодности

- •2.2 Принципы вычисления управляемости

- •2.3 Принципы вычисления наблюдаемости

- •2.4 Принципы вычисления тестопригодности

- •2.4.1. Тестопригодность как функция управляемости и наблюдаемости

- •2.5. Применение системы camelot на практике.

- •2.5.1. Количественная оценка проектируемых схем.

- •2.5.2. Автоматический выбор контрольных точек.

- •2.5.3 Методика генерации тестов вручную.

- •2.5.4. Методика автоматической генерации тестов

- •2.6. О других системах анализа тестопригодности

- •2.7. Заключительные замечания о методах анализа

- •3. Методы структурного проектирования

- •3.1. Принцип метода сканирования: сканируемый путь

- •3.2. Сканирование с произвольным доступом

- •3.3. Метод сканирования, чувствительного к уровню тактового сигнала

- •3.4. Недостатки и достоинства методов сканирования

- •3.5. Методы самотестирования: bilbo

- •3.5.3. Устройство встроенного поблочного диагностирования логических схем (bilbo)

- •3.6. Заключительные замечания о методах сканирования

- •4. Генерация тестов для схем, реализующих принцип сканирования

- •4.1. Алгоритм podem, условные обозначения, понятия и принципы

- •4.1.5. Вычисление относительных значении управляемости

- •4.2. Процедура podem

- •4.2.1. Пример 1. Основной принцип podem

- •4.2.2. Пример 2. Многомерный d-проход

- •4.2.3. Пример 3. Переопределение состояний первичных входов

- •4.2.4. Заключение относительного алгоритма podem

- •4.3. Процедура raps

- •4.3.1 Пример 4. Процедура raps

- •4.3.2. Заключение о процедуре raps

- •4.4. Методика выполнения процедур raps и podem

- •4.4.1 Использование статического сжатия тестов

- •4.4.2. Использование динамического сжатия тестов

- •4.5. Замечание относительно процедуры моделирования неисправностей

- •4.6. Заключительные замечания о процедурах podem и raps

- •5. Практические рекомендации по проектированию тестопригодных схем

- •5.1. Средства поддержки процедуры генерации тестов

- •5.2. Средства поддержки процедур тестирования и поиска неисправностей

- •Содержание

5.2. Средства поддержки процедур тестирования и поиска неисправностей

Предыдущие рекомендации связаны в основном с проблемами генерации эффективных тестовых наборов. Этот раздел содержит рекомендации, которые в основном имеют отношение к проблемам реализации тестового диагностирования и выполнения диагностических процедур поиска неисправностей.

РЕКОМЕНДАЦИЯ 12

Компоновать монтажную схему так, чтобы эквивалентные неисправности размещались в одном и том же корпусе интегральной микросхемы

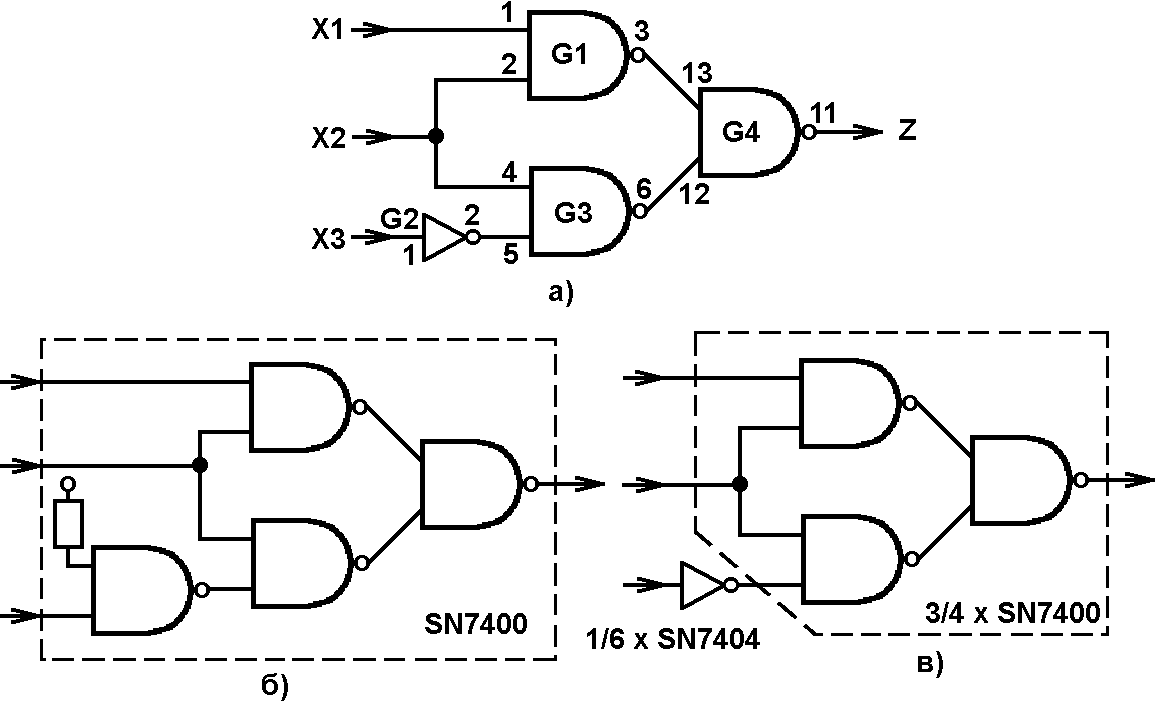

Если поиск неисправности основан на взаимосвязи реакции схемы с перечнем возможных неисправностей в словаре неисправностей, то полезно эквивалентные неисправности сгруппировать так, чтобы они размещались в одной и той же микросхеме. В этом случае нет необходимости в дальнейшем уточнении места неисправности с помощью управляемого пробника. Пример такого подхода приведен на рис. 5.17,а.

Рис 5.17. Влияние эквивалентных неисправностей на точность диагностирования:

а – схема с эквивалентными неисправностями 1.1 п-к-1, 2.1 н-к-0, 2.2 н-к-1, б–одна микросхема SN74200, в – две микросхемы

В этой схеме неисправность н-к-1 в узле G1.1 обнаруживается таким же тестовым набором, как и эквивалентная ей пара неисправностей G2.1 н-к-0 и G 2.2 н-к-1 инвертора G 2. Поэтому если при компоновке монтажной схемы нет каких-либо ограничений, то всю схему предпочтительнее реализовать на двухвходовых элементах И-НЕ одной микросхемы (рис. 5.17,6), а не на трех вентилях И-НЕ одной микросхемы и одного инвертора другой микросхемы (рис. 5.17,в).

На практике все еще есть необходимость идентифицировать источник неисправности с точностью до элемента замены, чтобы исключить проводник печатной платы как причину неисправности. Эта необходимость снижает положительный эффект рекомендации, однако группирование эквивалентных неисправностей может быть полезным при определенных обстоятельствах, т. е. когда известно, какое конкретное устройство подозревается неисправным. Это, в частности, справедливо для группы вентилей, выходы которых соединены вместе либо в виде схемы монтажного ИЛИ, либо монтажного И.

РЕКОМЕНДАЦИЯ 13

Обеспечить возможность диагностическому оборудованию управлять цепью тактовой синхронизации

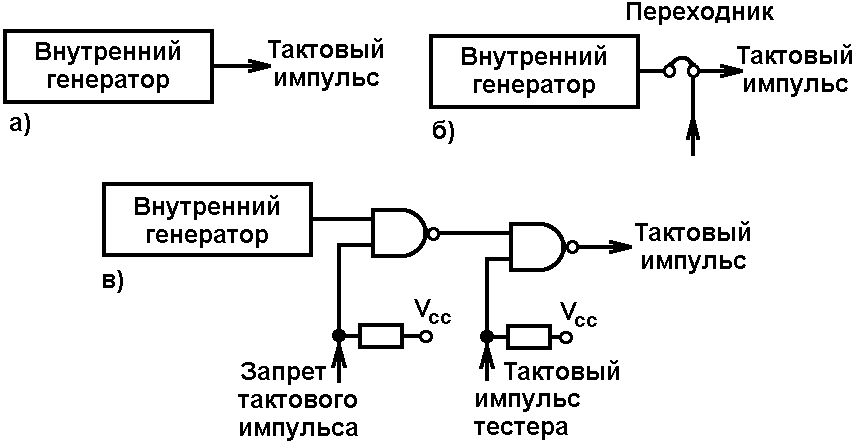

В схемах, содержащих автономные генераторы на печатной плате, внутреннюю тактовую синхронизацию обычно необходимо заменять внешней, обеспечиваемой диагностическим оборудованием. Таким путем, если необходимо, можно сократить частоту функционирования схемы и свести его к одношаговым операциям. Способы замены внутреннего генератора тактовых импульсов показаны на рис. 5.18.

Рис. 5.18. Способы замены тактового генератора:

а – обычная структура; б – соединение перемычкой или контактным разъемом; в – блокировка тактового генератора

РЕКОМЕНДАЦИЯ 14

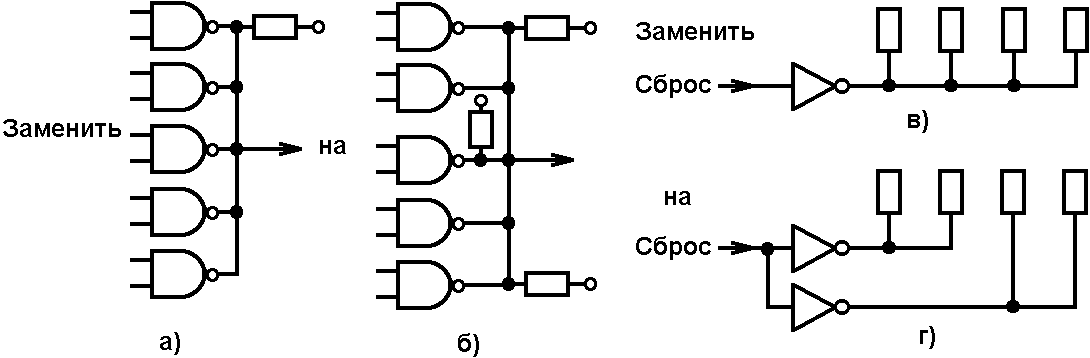

Избегать использования диагностически неразличимых групп элементов, таких, как проводное ИЛИ, проводное И и узлов с большим числом ветвлений

Узлы соединений проводного ИЛИ, проводного И и линии с высоким коэффициентом ветвлений создают неопределенность при поиске неисправного элемента. По возможности следует избегать таких схемных решений (рис. 5.19).

Кроме того, вентили, выходы которых соединены вместе, полезно сгруппировать по отдельным корпусам микросхем. Таким образом, если несколько вентилей подозреваются поврежденными в результате присутствия неисправности на общем выходом узле, то заменить необходимо только несколько корпусов (предпочтительнее один).

Рис. 5.19 Способы уменьшения неопределенности диагностирования

РЕКОМЕНДАЦИЯ 15

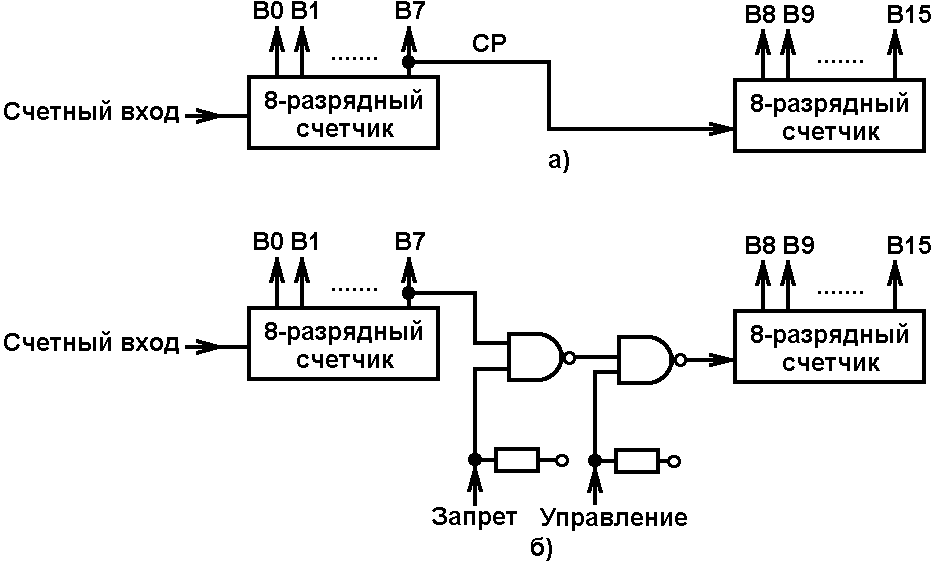

Разрывать длинные цепи на счетчиках

На рис. 5.20,а показан 16-разрядный счетчик, состоящий из двух 8-разрядных счетчиков. Для того чтобы проверить такой счетчик полным тестом, необходимо подать 216+1=65537 тактовых импульсов на частоте 50 кГц на эту процедуру потребляемую приблизительно 1,3 с. Теперь рассмотрим модифицированную схему, показанную на рис. 5.20,6. Каждый 8-разрядный счетчик этой схемы может быть проверен отдельно, и общее время ее проверки сократится до 2 Х(28 + 1)Х 0,02мс, т. е. составит приблизительно 10 мс. Экономия времени тестирования имеет важное значение и приносит пользу сама по себе, но эта экономия полезна также тогда, когда счетчик необходимо устанавливать в определенное состояние для проверки других устройств, расположенных на плате. (В этом отношении независимый доступ и возможность предварительной установки каждого счетчика весьма полезны.)

Рис. 5.20. Управляемый разрыв в структурах на счетчиках:

а – обычная структура; б – реализация независимого функционирования

РЕКОМЕНДАЦИЯ 16

Буферировать входы, чувствительные к фронту импульсного сигнала

Многие управляющие импульсы элементов памяти устройств, такие, как тактовые сигналы, должны иметь минимальные длительности фронта и среза. Если эти сигналы поступают непосредственно с контактного разъема, то может оказаться, что необходимо ввести дополнительно буферное устройство (линейный усилитель, триггер Шмитта или два инвертора) в интерфейс между печатной платой и тестером для формирования последним импульсов с требуемыми параметрами. О чем на самом деле говорит эта рекомендация? Устройства, которые запитываются импульсными сигналами и чувствительны к длительностям их фронтов или срезов, следует отделять от первичных входов и выходов буферами.

РЕКОМЕНДАЦИЯ 17

Внимательно следить, чтобы монтажная схема печатной платы и конструкция способствовали снижению утомляемости оператора и обеспечению непосредственного доступа к узлам схемы

Чтобы уменьшить утомляемость оператора в процессе поиска неисправностей с помощью ручного пробника на печатных платах различного типа, полезно размещать микросхемы на плате в регулярном порядке (по рядам и столбцам) и ориентировать их стандартно, т. е. например, так, чтобы вывод 1 микросхемы располагался в левом верхнем углу. Ошибки происходят также в тех случаях, когда оператор переходит от микросхемы с 14 выводами к микросхеме с 16 выводами, хотя трудно предложить решение этой проблемы. Можно отмечать все микросхемы с 16 выводами цветной меткой или размещать их в определенных столбцах печатной платы.

Следует использовать стандартные соединительные контактные разъемы (например, с одним и тем же шагом), источники питания и общие точки должны всегда находиться на одних и тех же позициях. Входы шины должны конструктивно располагаться рядом и группироваться в соответствии с входными и выходными шинами тестера. (Например, некоторые тестеры способны воздействовать параллельно в каждый момент времени только на группу из 16 выводов.) Должна быть также четкая маркировка номера платы и уровня модификации; сетка обозначений на плате и маркировка любых дискретных элементов специальными идентификаторами элементов (Rl, R2 и т. д.) предпочтительнее, чем справочная сетка.

Все микросхемы и печатные проводники печатных плат, которые должны диагностироваться с помощью управляемых пробников, полезно для наблюдения располагать с одной стороны платы (хотя это невозможно для многослойных печатных плат). Наблюдаемость микросхем необходима для обычной работы с пробником, наблюдаемость печатных дорожек необходима для измерений параметров соединений, чувствительных к току. При этом невозможно проследить за печатным проводником, проходящим под корпусом микросхемы. Аналогично сквозные металлизированные отверстия (межслойные переходы) могут создавать трудности при отслеживании трасс. При использовании контактных щупов любой формы следует избегать защитного изолирующего покрытия.

Не вынесенные на контактный разъем платы контрольные точки должны группироваться на печатной плате вблизи друг от друга для упрощения интерфейса с помощью гибких проводов. Это можно сделать, используя дополнительные гнезда интегральных микросхем или располагая в ряд с регулярным шагом столбиковые выводы или штырьки для монтажа методом накрутки. В этом случае доступ к контрольным точкам осуществляется через одноконтактный наконечник, заканчивающийся соответствующей вилкой или гнездом.

Может появиться необходимость осуществить доступ к устройству с помощью одно- или многоконтактного зажима (клипсы). В этом случае следует предпринять меры, чтобы обеспечить вокруг этого устройства пространство для сопряжения с зажимом. Обычно логические микросхемы не располагаются очень близко друг к другу, но иногда дискретные компоненты, такие, как согласующие резисторы и развязывающие конденсаторы, размещаются в непосредственной близости от микросхемы и затрудняют использование клипсы.

И, наконец, часто считают целесообразно устанавливать сложные микросхемы в специальные контактные гнезда так, что в процессе диагностирования микросхему можно было бы снять, и если обнаружено, что она неисправна, то заменить ее. В противовес этим достоинствам увеличивается опасность загиба выводов во время повторных установок микросхемы, неправильной ориентации и замены ее и возрастает установочное время тестирования, Если эти недостатки перевешивают достоинства установки микросхем в контактные гнезда, то лучше выполнить монтаж микросхемы пайкой, обеспечивая при этом все меры электрической изоляции выводов. В любом случае, проходит или не проходит часть тестовой программы, устройство не должно удаляться с платы в процессе тестирования, даже если оно установлено в контактное гнездо.

РЕКОМЕНДАЦИЯ 18

Предусмотреть короткозамкнутые перемычки на печатном разъеме для проверки сопряжения печатной платы и тестера

На практике неплохо, чтобы оператор проверил правильность сопряжения и ориентации печатной платы перед началом выполнения тестовой программы. Однако полезно, чтобы самой программой выполнялась эта проверка перед подключением источника питания. Один из способов решения этой задачи заключается в установке короткозамкнутой перемычки между двумя неиспользованными контактами печатного разъема. В этом случае с помощью тестовой программы можно проверить, существует ли эта перемычка, и продолжить затем выполнение программы (рис. 5.21)

Рис 5.21 Автоматическая проверка сопряжения печатной платы:

контакты разъема i и j замкнуты внутренней перемычкой на печатной плате, что позволяет проверить правильность их сопряжения перед включением питания. Такой способ значительно уменьшает опасность повреждения (печатной платы или тестера) в результате неправильного сопряжения.

РЕКОМЕНДАЦИЯ 19

Сохранять простоту интерфейса между печатной платой и тестером

Стандартный интерфейс между проверяемой платой и тестером содержит первичные входы, первичные выходы, которым соответствует логический уровень согласования сигналов, включая согласование тестовых воздействий и реакций, и распределение источников питания. Кроме того, здесь могут быть другие интерфейсные средства, такие, как перекидные одно- и многоконтактные пробники, буферные устройства, зажимные компоненты, контактные разъемы, расположенные с двух сторон платы, разъемы различных типов и внутриплатные соединительные разъемы. Хотя каждое из этих средств упрощает частную проблему тестирования, в совокупности они дополнительно усложняют эту процедуру с точки зрения инженера-диагноста, и увеличивают объем тестового оборудования для проверки логических функций и затраты. Проводники могут также представлять собой значительную емкостную нагрузку. Общая инженерная заповедь «сохраняй простоту» применима к данному случаю более чем где-нибудь.

РЕКОМЕНДАЦИЯ 20

Избегать смешанного использования логических элементов разных серий на одной плате

Логическим элементам различных серий требуются различные пороговые эталонные уровни логических сигналов на выводах приема и передачи и обычно различные уровни напряжений питания. Поэтому использование двух или большего числа логических серий на одной и той же плате может значительно усложнить интерфейс. Если смешанная логика неизбежна, то имеется одно решение: обеспечить совместимость всех первичных входов и первичных выходов, по крайней мере, с серией ТТЛ.

РЕКОМЕНДАЦИЯ 21

Ограничить коэффициент разветвления устройства значением, которое на единицу меньше максимального

Если на выходе устройства включена максимальная нагрузка, то добавление нагрузки в виде управляемого пробника на этом узле при тестировании может перегрузить устройство и вызвать искажение выходного сигнала. Чтобы исключить это, следует ограничивать коэффициенты разветвления устройств значениями, которые на единицу меньше максимально допустимых.

РЕКОМЕНДАЦИЯ 22

Обеспечить функциональную полноту схемы, размещенной на печатной плате

Средства, такие, как схему регенерации МОП ЗУПВ, обеспечивающие независимость и функциональную полноту характеристик, необходимо размещать на той же самой плате, где расположена основная часть схемы, для которой предназначены эти средства. Это устраняет необходимость иметь их в тестере и решать следующие проблемы:

а) обеспечивать одновременно цикл регенерации и выполнять процедуры тестирования, что возможно при определенных аппаратурных затратах и высоком быстродействии;

б) обеспечивать вызовы подпрограмм регенерации на уровне тестового диагностирования.

РЕКОМЕНДАЦИЯ 23

Знать предельные характеристики диагностического оборудования

В конечном счете, кристалл или плату приходится сопрягать электрически с тестером. Следовательно, важно знать и понимать предельные характеристики и возможности диагностического оборудования.

Важнейшими из них являются следующие:

А. Максимальная скорость, с которой на двунаправленном выводе могут изменяться режимы прием-передача. Это важный параметр, определяющий возможности тестирования двунаправленных линий.

Б. Возможность использовать так называемые «импульсные ловушки», позволяющие захватывать и измерять динамические процессы, такие, как импульсы малой длительности.

В. Возможность передавать данные в двух режимах: асимметричном, в котором в каждый момент времени изменяется сигнал на одном выводе, или блочном, в котором обеспечивается совместное изменение сигналов на определенных выводах. Обычно используется асимметричный режим, но порой необходим блочный, например когда информация передается на множество линий шины. Однако даже в блочном режиме существует некоторая асимметрия изменений сигналов между отдельными выводами. Эта асимметрия может быть существенной для быстродействующих шин.

Г. Максимальная скорость изменения сигналов из 0 в 1 и из 1 в 0 на выводе при передаче информации, которая обычно определяется временем нарастания и спада выходного напряжения операционного усилителя. Эти времена могут быть различными для отдельных выводов, но в любом случае должна обеспечиваться возможность установки на каждом из них максимальной скорости изменений сигналов.

Д. Возможность идентифицировать в проверяемой схеме логические значения 0 и 1 по одному или двум установленным пороговым уровням в режиме приема информации. Очевидно, эти пороговые значения должны программироваться, что в некоторых случаях необходимо для переопределения логических значений во время выполнения тестовой программы.

Е. Возможность использовать средства синхронизации проверяемой схемы. Если проверяемая схема содержит внутренний независимый генератор, то полезно, чтобы операции в тестере синхронизировались с частотой этого генератора.

Ж. Возможность тестера использовать остановки в процессе тестирования, связанные с необходимостью выполнения в проверяемом устройстве фоновых операций, таких, как цикл регенерации данных в МОП ОЗУ. Тестер должен иметь возможность выполнять в это время другие полезные тестовые процедуры.

3. Возможность стабилизировать процессы, что является важной характеристикой тестера. Стробирование определяет моменты времени, в которые сигналы передаются через согласующие цепи на проверяемую схему, и моменты времени, в которые сигналы, приходящие с проверяемой схемы, улавливаются измерительными преобразователями тестера. Необходимо иметь возможность изменять длительность строб-импульса (для согласования с временем задержки сигналов, распространяющихся через проверяемую схему) и частоту стробирования (для выполнения необходимые условий при измерении динамических параметров). Длительность стробирующего импульса и его частота должны иметь минимальные и максимальные пределы значений.

И. Предельные электрические параметры на выводах тестера «передача-прием», такие, как максимальный ток источника и стока; максимальные положительные и отрицательные перепады напряжений; пределы изменений напряжений логического нуля я единицы при приеме и передаче данных; нагрузочные характеристики (а также возможность проверки емкостной нагрузки интерфейсных проводов).

К. Возможность проверки согласующих резисторов, подключающих выводы тестера к источнику питания или общей шине. Это требуется для проверки третьего состояния и узлов элементов с открытым коллектором.

РЕКОМЕНДАЦИЯ 24

Обращать специальное внимание на платы, которые должны проверяться с помощью внутрисхемного тестирования

В настоящее время внутрисхемное тестирование смонтированных печатных плат является полезным и популярным методом поиска дефектов, вносимых в процессе производства сборочных работ. Цель этого способа – проверить каждое устройство на плате, аналоговое и цифровое, изолированно от всех других устройств, размещенных на плате. Электрическое подключение к устройству осуществляется с помощью специального приспособления, называемого «ложе из гвоздей», которое обеспечивает прямой контакт между выводами тестера и той стороной печатной платы, на которой отсутствуют компоненты. Контактные иголки тестера непосредственно подсоединяются либо к местам пайки выводов компонентов, либо к контактным площадкам, соединенным с компонентами платы. Пассивные аналоговые компоненты электрически изолируются от остальной схемы специальными методами. Цифровые устройства изолируются путем управления компонентами, с которыми соединяется проверяемое устройство. Это управление осуществляется методом «перевешивания» сигналов, прикладываемых тестером к контрольной точке, описанного ранее в этой главе (см. рис. 5.2). В соответствии с методологией тестирования сначала проверяется наличие в схеме разрывов и короткозамкнутых цепей (при отключенном питании), а затем к плате подключается напряжение питания и каждое устройство проверяется отдельно с помощью множества заранее определенных стандартных тестов. Считается, что любая неисправность при такой проверке вызывается дефектом проверяемого устройства или соседних устройств, электрически связанных с проверяемым.

Главная цель внутрисхемного тестирования заключается в обнаружении дефектов, появляющихся в процессе производства платы. Этот метод не обеспечивает проверку правильности функционирования всей платы в целом, т. е. коллективное взаимодействие и функционирование устройств платы. Эта проверка выполняется на следующем этапе с помощью тестера, подключаемого к разъему печатной платы, или системы, заменяющей тестер.

Ввиду важности внутрисхемного тестирования следует рассмотреть все специфические конструкторско-технологические и производственные особенности, улучшающие тестопригодность. Конечно, многие из рекомендаций, рассмотренные ранее, могут быть все еще полезными (как будет показано далее), но имеется ряд рекомендаций, которые связаны только с особенностями внутрисхемного тестирования плат. Эти рекомендации перечислены ниже. Большинство из них связано с максимизацией доступа к внутрисхемным элементам на основе тщательного анализа топологии и конструкции печатной платы; другие в большей степени касаются улучшения электрических характеристик при реализации тестирования.

А. Обязать разработчиков устанавливать все компоненты только на одной стороне печатной платы. Зондирование с помощью вакуумных присосок тестера становится затруднительным, даже невозможным, если компоненты размещены на стороне зондов.

Б. При сверлении отверстий в печатной плате необходимо соблюдать строгое позиционирование, чтобы обеспечить точное сопряжение с контактным полем тестера. В действительности многие проблемы использования внутрисхемного тестирования обусловлены неправильным сопряжением, вызывающим ненадежный электрический контакт.

В. В случае контактирования через площадку печатного проводника последнюю следует размещать как можно ближе к выводу проверяемой микросхемы, чтобы уменьшить влияние дополнительной нагрузки. Импульсная реакция узлов, расположенных рядом с проверяемым устройством, может вызвать эффект обратного воздействия этих узлов на входы проверяемого устройства, что приводит к ошибочным результатам процедуры тестирования. Вероятность такого эффекта заметно возрастает для быстродействующих логических устройств с низким уровнем помехозащищенности, таких, как ЭСЛ, для которых каждый путь передачи сигналов необходимо рассматривать как линию передачи.

Г. Специфическое применение устройства в схеме не должно препятствовать его использованию в качестве средства поддержки процедуры тестирования. Зачастую не все функциональные возможности устройства используются в схеме. Как правило, имеются незадействованные входы и вентили. Способы, с помощью которых развязываются входы, не должны ограничивать возможность управления ими, если в этом появится необходимость (как уже обсуждалось в рекомендации 11). Кроме того, выводы незадействованных устройств или вентилей должны соединяться с развязывающими цепями через некомпонентную сторону печатной платы, что позволяет подключаться к ним через контактные иголки тестера. (Здесь возникает интересный философский вопрос. Следует ли при внутрисхемном тестировании проверять устройство, исходя только из особенностей его конкретного применения в схеме и выполняемых им функций, или проверять его полным тестом, не учитывая особенностей использования в данной схеме? Четырехразрядный двоичный счетчик (например, SN74161) используется для подсчета импульсов только из одного начального состояния (все триггеры в состоянии 0). Таким образом, четыре входа предварительной установки в любое начальное состояние не используются и развязаны через согласующие резисторы. Если прошли все тесты, кроме тестов, проверяющих правильность установки, то следует ли рассматривать счетчик как исправный или как неисправный? Ответ не однозначный. Он определяется соотношением между воспринимаемой неисправностью и реальным механизмом дефекта и тем, раскрывает ли объект тестирования все механизмы дефекта или только те дефекты, которые могут влиять на правильность функционирования.)

Д. Внимательно следить, чтобы не было слишком много обрывов в структуре заземления. В условиях внутрисхемного тестирования через выходы устройств протекают значительные импульсные токи, которые могут наводить шумовые выбросы на шине заземления. Эти выбросы могут вызывать непредвиденные переходные процессы в какой-либо части схемы, которые будут восприниматься, как проявления неисправности. Это особенно справедливо для логических элементов с низким уровнем помехозащищенности, таких, как ЭСЛ.

Е Аналогично некоторые буферные устройства, такие, как SN74S37 или SN74S240, могут быть источниками или приемниками больших токов. Если эти устройства связаны с проверяемым устройством, то существует опасность появления в процессе тестирования переходных процессов, которые могут изменить условия тестирования и, следовательно, его результата. Поэтому такие устройства целесообразно поддерживать в состоянии их «наименьшей агрессивности» (на выходе SN74S37 состояние логической единицы, выход SN74S240 в третьем состоянии). При проектировании схемы следует предусматривать возможность простой установки этого состояния.

И, наконец, многие из предыдущих рекомендаций находят конкретное применение в тестерах, реализующих внутрисхемное тестирование. В частности, это рекомендации 6 (относительно начальной установки), 7 (о разрыве цепей обратной связи), 9 (относительно проектирования для серийного производства), 10 (о зависимости тестирования от информации ПЗУ и ПЛМ), 11 (об использовании свободных выводов), 13 (об управлении цепью тактовой синхронизации), 17 (касающаяся вопросов топологии и монтажа печатных плат, таких, как ориентация, маркирование, установка контактных гнезд) и 23 (о предельных характеристиках и возможностях диагностического оборудования).

РЕКОМЕНДАЦИЯ 25

Выпускать четкую конструкторско-технологическую документацию

Последнее, но не менее важное, инженер-разработчик должен выдать четкую конструкторско-технологическую документацию по проекту схемы. В частности, документация должна содержать следующее:

а) полную Функциональную спецификацию схемы, включающую пояснения к обозначениям сигналов там, где они неоднозначны;

б) временные диаграммы и допустимые отклонения, поясняющие результаты управляющих воздействий;

в) детальные описания обрамления схемы и обозначения всех частей разрабатываемого изделия, которые в будущем могут быть усовершенствованы;

г) четкие чертежи логических схем с обозначением главных и второстепенных цепей обратной связи и пояснением всех нестандартных логических элементов обозначений;

д) детальные описания требований к источникам питания, таких, как последовательность операций для многоуровневых питающих напряжений, максимальный ток нагрузки и потребления, любые специальные уровни напряжений;

е) функции ПЗУ и ПЛМ должны быть представлены в форме булевых выражений. Если эти выражения не найдены, то следует представить в шестнадцатеричной форме распечатки таблиц истинности.

ж) рекомендуемую методологию тестирования, самотестирования и детали всех принятых мер защиты от неисправностей, отказобезопасности и отказоустойчивости.

СПИСОК ЛИТЕРАТУРЫ

Беннетс. Проектирование тестопригодных логических схем / пер. с англ. –М.: Радио и связь, 1990.

Вуд А. Микропроцессоры в вопросах и ответах / пер. с англ. под ред. Д.А. Поспелова.-М.: Энергоатомиздат, 1985.

Каган Б.М. Электронные вычислительные машины и системы.-М.: Энергия, 1979