- •Введение

- •Обзор современного состояния субмикронной и глубоко-субмикронной технологий

- •Проектирование цифровых интегральных схем

- •Задачи и методы схемотехнического моделирования сбис

- •Этапы проектирования сбис

- •Общие вопросы характеризации цифровых библиотек

- •Характеризация логических элементов

- •Характеризация элементов памяти

- •Анализ переходных процессов

- •Описание характеристик ячеек из библиотеки

- •Языки моделирования цифровых библиотек

- •Обзор средств, существующих в настоящее время

- •Средства проектирования компании cadence

- •Системное проектирование

- •Аппаратное проектирование и верификация

- •Математическое макетирование

- •Топологическое проектирование

- •Средства проектирования компании synopsys

- •Средства проектирования компании mentor graphics

- •Системный уровень

- •Уровень регистровых передач

- •Логический уровень

- •Заказное проектирование аналоговых и смешанных схем

- •Топологическое проектирование

- •Краткое описание возможностей SystemC

- •Контекст SystemC

- •Аспекты SystemC

- •Точность моделирования

- •Модели вычислений

- •Функциональное моделирование

- •Моделирование на уровне транзакций

- •Уровень rtl и связь с реализацией

- •Верификационные расширения

- •Построение модели функционального виртуального прототипа

- •Модели использования fvp

- •Создание встроенных программ

- •Функциональная верификация

- •Анализ fvp с помощью транзакций

- •Программы для характеризации цифровых библиотек

- •Spice-подобные программы моделирования

- •Интерфейс к пользовательским моделям

- •Программная система Charisma

- •Характеризация цифровой ячейки по помехоустойчивости

- •Помехоустойчивость цифровых бис к воздействию внешних помех

- •Устойчивость цепей питания цифровых бис

- •Анализ устойчивости цифровых бис к воздействию внутренних помех

- •Влияние помех в шинах питания на входы бис

- •Рекомендуемые схемотехнические методы борьбы с помехами в шинах питания бис

- •Помехи, генерируемые в сигнальных шинах из-за перекрестного взаимодействия

- •Помехи в сигнальных шинах, вызванные «состязаниями» сигналов

- •Конечная верификация проекта

- •Электрическая верификация

- •Временная верификация

- •Функциональная верификация

- •Заключение

- •Библиографический список

- •Оглавление

- •394026 Воронеж, Московский просп., 14

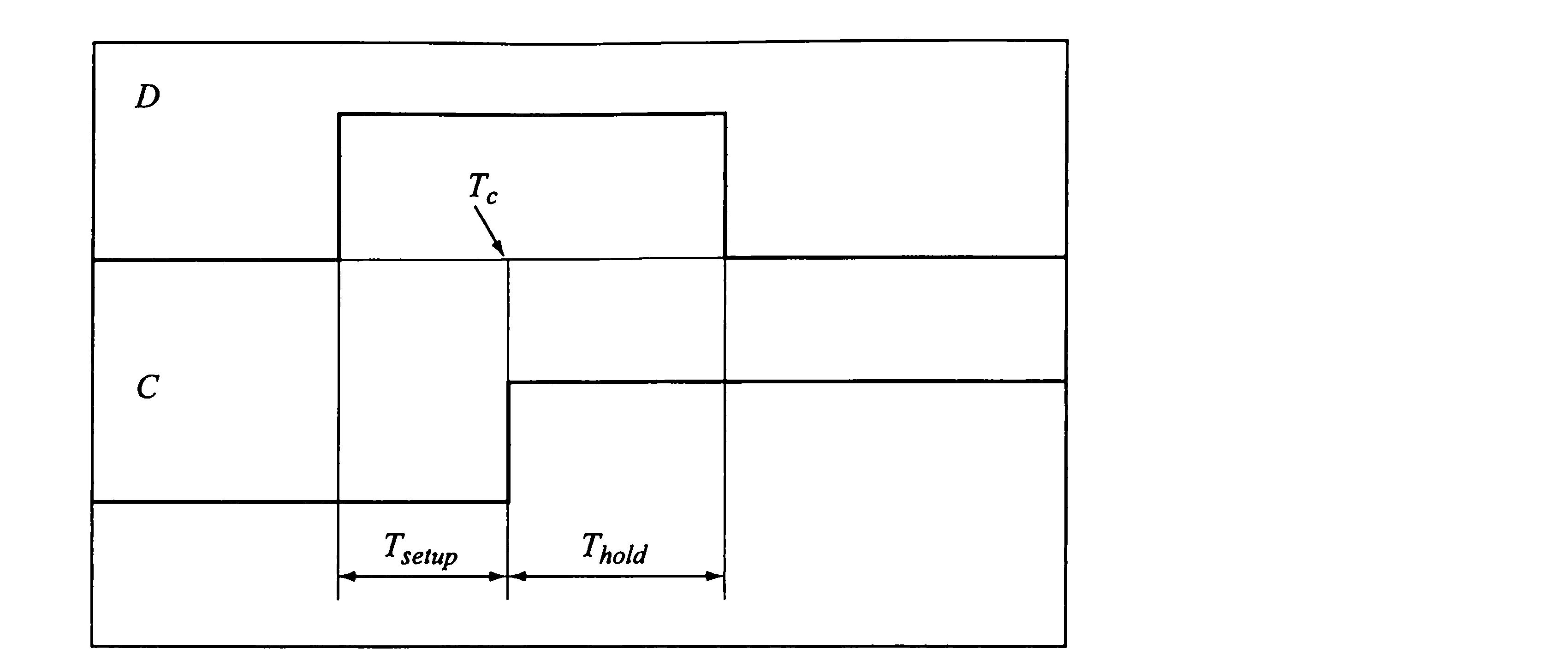

Характеризация элементов памяти

Особенно трудоемкой процедурой является процесс характеризации элементов памяти (ЭП), в частности триггеров. Дело не только в том, что схемы таких элементов, как правило, значительно сложней, чем схемы логических вентилей, но также в том, что для ЭП необходимо вычислять такие специфические параметры, как времена предустановки и удержания информационных сигналов - Тsetup и Тhold. Рассмотрим, что означают эти параметры. Триггеры D-типа имеют информационный вход D и тактирующий вход С. Изменение выходного состояния входа происходит при подаче на вход С переднего (или заднего) фронта тактового сигнала. Выходное состояние триггера определяется значением сигнала на информационном входе D (и внутренним состоянием триггера). Для бессбойной работы D-триггера необходимо установить на информационном входе требуемое логическое состояние (точнее, требуемое напряжение) несколько раньше, чем поступит фронт тактирующего импульса на вход С, и удерживать состояние D входа нужно некоторое время, после прохождения фронта С (рис. 10).

Р ис.

10. Определения параметров Тsetup

и Thold

D-триггера

ис.

10. Определения параметров Тsetup

и Thold

D-триггера

Сумма Тsetup + Тhold фактически определяет предельное быстродействие триггера, поэтому важно знать минимально возможные значения этой суммы и каждого из слагаемых. Минимальные значения в сильной степени зависят от длительности фронтов D и С импульсов, и, в значительно меньшей степени, от емкости нагрузки на выходе триггера. Поэтому, как правило, при характеризации ЭП ограничиваются построением таблиц {Tsetup(SkD,SlC)}, полученных при одном значении емкости нагрузки (SkD,SlC - длительности фронтов D и С сигналов соответственно).

Методов прямого вычисления минимальных значений Тsetup и Тhold, видимо, не существует, поэтому для их определения применяются методы поиска. Рассмотрим как вычислить по отдельности времена Тsetup и Тhold.

Для вычисления Тsetup установим сначала передний и задний фронты импульса D заведомо далеко от момента прихода Тс тактового импульса С. Такое положение фронтов должно обеспечивать правильную работу триггера и минимальную задержку выходного сигнала T0del, которую вычислим и запомним. Запомним также положение переднего фронта D на временной оси, обозначив его t_p. Не меняя положения заднего фронта D, придвинем передний фронт D вправо к точке Тc на некоторую величину Δt. Если при этом триггер работает правильно, то вычислим задержку выходного сигнала Тdel и сравним ее с T0del.

Обычно при приближении фронта D к Тc начиная с некоторого момента, происходит увеличение задержки выходного сигнала. Если это увеличение задержки превысит некоторый предел, установленный пользователем, то такое положение фронта D к Tc, начиная с некоторого момента, происходит увеличение задержки выходного сигнала. Если это увеличение задержки превысит некоторый предел, установленный пользователем, то такое положение фронта D считается недопустимым. Обозначим его t_f. Если же при новом положении фронта D триггер вообще работает неправильно, то также запомним это положение, как t_f. Наконец, если триггер при новом положении фронта работает правильно и относительное увеличение задержки не превышает заданный уровень, то обозначим это положение как t_р и снова передвинем передний фронт вправо на Δt. Повторяя этот процесс, мы в конце концов получим отрезок [t_р, t_f] на левом конце которого триггер работает правильно, а на правом - неправильно. Теперь делим этот отрезок пополам, смещаем передний фронт D в полученную точку и определяем, как описано выше, что это за точка -t_р или t_f.

Сокращая таким образом интервал поиска, найдем с заданной точностью время Тsetup. Совершенно аналогично вычисляется и время Тhold, только при этом смещается влево задний фронт импульса D.

Рассмотрим теперь как можно определить минимальное значение суммы Tsh= Тsetup + Тhold. Как и ранее, установим фронты импульса D заведомо далеко от точки Тс и вычислим эталонную задержку T0del. Не меняя положение переднего фронта D найдем, как описано выше, значение T0hold. Установим задний фронт D в позицию Тс + T0hold и определим при этом положении фронта значение T0setup.Таким образом, мы получили первое приближение Т0sh= T0setup + T0hold. Сместим теперь задний фронт D вправо в позицию T1hold = T0hold + Δt и вычислим новые значения Т1setup и T1sh= Т1setup + Т1hold. Если окажется, что T1sh > T0sh, то, следовательно, минимум Тsh нужно искать при положении заднего фронта на отрезке [Tc+ T0hold, Tc+ T1hold]. Если T1sh < T0sh , то нужно увеличит и повторить вычисления до тех пор, пока не будет выполнено условие T1sh > T0sh. Теперь, когда локализован интервал, на котором следует искать минимум Tsh, для его поиска можно применить любой алгоритм одномерного поиска. Часто используется метод квадратичной интерполяции.

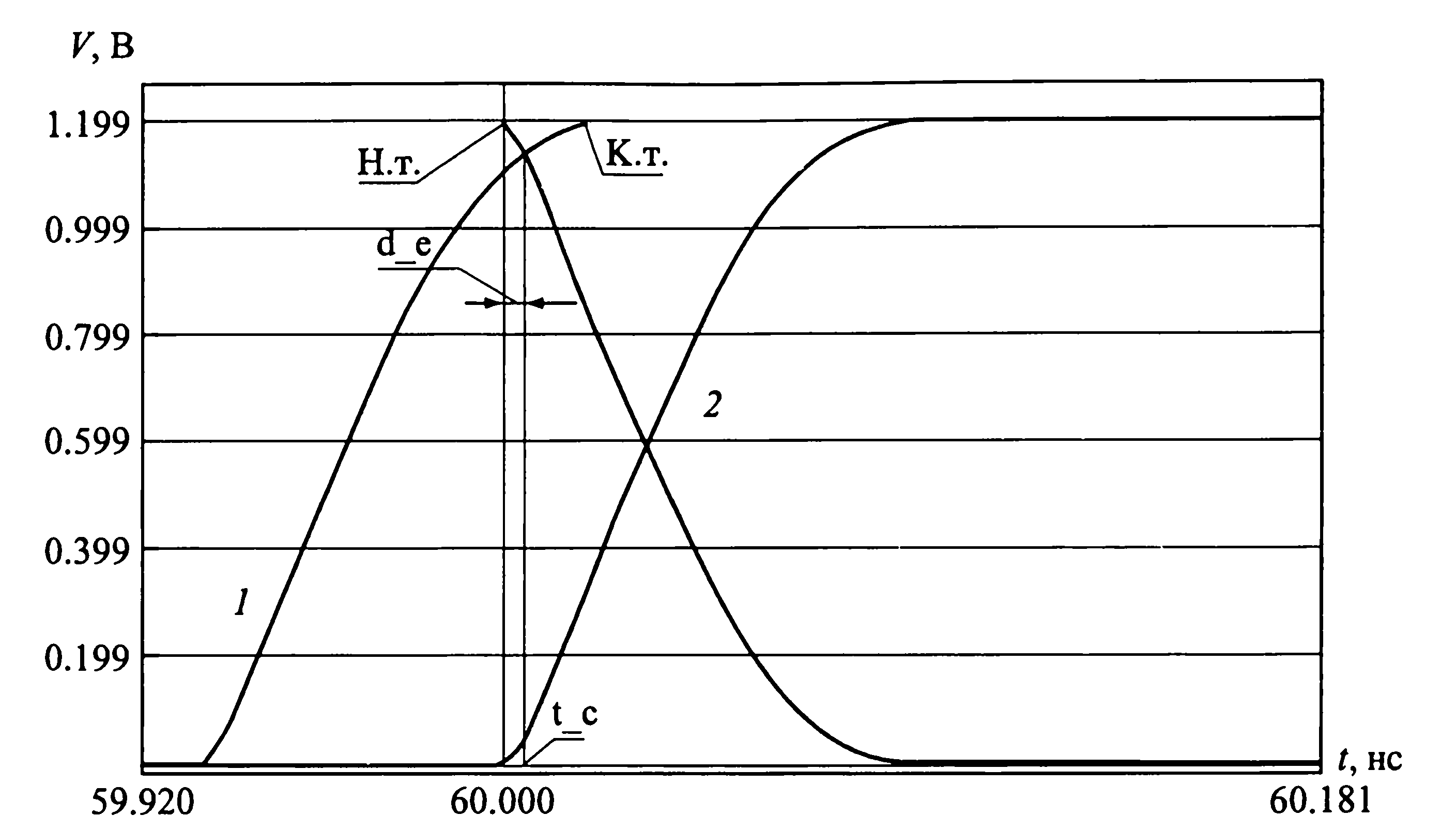

Следует отметить, когда передний и задний фронты D сближаются настолько, что «лезут» друг на друга («клиппирование» импульса), но при этом триггер не теряет работоспособности (рис. 11). При определении Тsh нужно ограничить это клиппирование, так чтобы не утратить возможность вычисления задержки выходного сигнала, т.е. пик клиппированного импульса не должен быть ниже 0.5Vdd. Заметим также, что это ограничение жестко связывает друг с другом положение переднего и заднего фронтов D-сигнала, что делает неоднозначным решение задачи определения минимума суммы Tsetup + Thold .

Рис. 11. Клиппирование импульса на информационном входе триггера при определении минимума суммы Tsetup + Thold

Из приведенного выше видно, какой большой объем вычислительной работы приходится выполнять при характеризации ЭП. Так как каждый шаг описанных алгоритмов - это новое моделирование схемы. Поэтому здесь особенно сказываются преимущества применения специализированного входного сплайн-источника, что дает гибкий механизм управления внутри программы моделирования положением фронтов сигналов.