- •Введение

- •Обзор современного состояния субмикронной и глубоко-субмикронной технологий

- •Проектирование цифровых интегральных схем

- •Задачи и методы схемотехнического моделирования сбис

- •Этапы проектирования сбис

- •Общие вопросы характеризации цифровых библиотек

- •Характеризация логических элементов

- •Характеризация элементов памяти

- •Анализ переходных процессов

- •Описание характеристик ячеек из библиотеки

- •Языки моделирования цифровых библиотек

- •Обзор средств, существующих в настоящее время

- •Средства проектирования компании cadence

- •Системное проектирование

- •Аппаратное проектирование и верификация

- •Математическое макетирование

- •Топологическое проектирование

- •Средства проектирования компании synopsys

- •Средства проектирования компании mentor graphics

- •Системный уровень

- •Уровень регистровых передач

- •Логический уровень

- •Заказное проектирование аналоговых и смешанных схем

- •Топологическое проектирование

- •Краткое описание возможностей SystemC

- •Контекст SystemC

- •Аспекты SystemC

- •Точность моделирования

- •Модели вычислений

- •Функциональное моделирование

- •Моделирование на уровне транзакций

- •Уровень rtl и связь с реализацией

- •Верификационные расширения

- •Построение модели функционального виртуального прототипа

- •Модели использования fvp

- •Создание встроенных программ

- •Функциональная верификация

- •Анализ fvp с помощью транзакций

- •Программы для характеризации цифровых библиотек

- •Spice-подобные программы моделирования

- •Интерфейс к пользовательским моделям

- •Программная система Charisma

- •Характеризация цифровой ячейки по помехоустойчивости

- •Помехоустойчивость цифровых бис к воздействию внешних помех

- •Устойчивость цепей питания цифровых бис

- •Анализ устойчивости цифровых бис к воздействию внутренних помех

- •Влияние помех в шинах питания на входы бис

- •Рекомендуемые схемотехнические методы борьбы с помехами в шинах питания бис

- •Помехи, генерируемые в сигнальных шинах из-за перекрестного взаимодействия

- •Помехи в сигнальных шинах, вызванные «состязаниями» сигналов

- •Конечная верификация проекта

- •Электрическая верификация

- •Временная верификация

- •Функциональная верификация

- •Заключение

- •Библиографический список

- •Оглавление

- •394026 Воронеж, Московский просп., 14

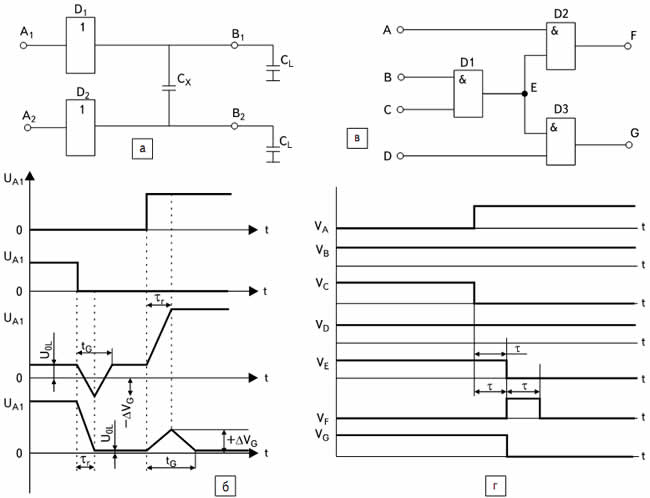

Помехи в сигнальных шинах, вызванные «состязаниями» сигналов

В реальных БИС время задержки распространения сигналов логических элементов имеет конечное значение, зависящее от конкретных условий применения (емкости и индуктивности нагрузки, напряжения питания). При этом значения времени задержек переключения носят статистический характер и могут изменяться для разных БИС. Конечные значения времени задержек переключения и их технологический разброс приводят к ситуации, когда сигналы по различным цепям могут распространяться с разной скоростью и вызывать «состязания» сигналов, приводящие к помехам в сигнальных шинах. Механизм генерации указанного типа помех в цифровых БИС поясняется на рис. 28,в, г, где приведены фрагмент функциональной схемы цифровых БИС в произвольной логике и временные диаграммы работы. Допустим, входы [А, В, С, D] находились в исходном состоянии [0111]. При изменении исходного состояния входов на [А, В, С, D] = [0111] в соответствии с функциональной схемой состояние выходов [F, G] должно изменяться с [01] на [00]. Однако, поскольку логические элементы имеют конечное значение, прямое изменение сигнала на входе А вызовет переход выхода элемента в состояние высокого уровня [1] с задержкой 1τ.

Рис. 28. Схемы, поясняющие механизм генерации помех «перекрестного» типа (а), вызванных «состязаниями» сигналов (в) и временные диаграммы сигналов (б и г)

Изменение сигнала на входе С приведет к появлению задержанного на 1τ сигнала на втором входе логического элемента D2 и обратному переключению его выхода F в состояние низкого уровня [0] через время 2τ. То есть из-за различного времени прохождения сигналов по цепям (вход А — выход F и вход С — выход F) и конечного времени задержки логических элементов на выходе F вместо сохранения сигнала низкого уровня будет сформирован короткий (с длительностью »1τ) сигнал низкого уровня или «выброс» (glitch). Этот сигнал, распространяясь по цепям, может приводить к появлению ложных сигналов на выходах цифровых БИС и потере информации в элементах памяти (при появлении таких помех в цепи синхронизации). Образование сигналов помех и их длительность зависят от длины логических цепей и значений задержки. Помехи этого типа могут возникать также при воздействии других факторов, например, внешних электромагнитных воздействий или ионизирующей радиации, и могут быть как положительными — формирование сигнала высокого уровня на фоне сигнала низкого уровня [0], так и отрицательными — сигнал низкого уровня на фоне сигнала высокого уровня.

Конечная верификация проекта

Многие очень полагаются на моделирование как на основной метод обеспечения точности проектирования и нахождения критических параметров (например, скорости и рассеяние энергии). Однако следует помнить, что моделирование — это лишь один из инструментов разработчика. В общем случае полезно бывает различать моделирование и верификацию.

При моделировании значение параметра проекта (запас помехоустойчивости, задержка распространения или рассеиваемая энергия) определяется в выбранной модели путем подачи на вход цепи набора управляющих сигналов и извлечения параметров из получаемых сигналов. Данный подход очень гибкий, но обладает одним недостатком: его результаты зависят от выбора управляющих сигналов. Например, условие перераспределения заряда в динамическом логическом элементе нельзя обнаружить, не подав на вход именно ту последовательность сигналов, которая активизирует перераспределение заряда. Аналогично, задержка сумматора варьируется в широких пределах в зависимости от входного сигнала. Определение наихудшей ситуации также требует внимательного выбора управляющих сигналов. Другими словами, разработчик должен хорошо представлять внутреннюю структуру схемы и ее работу. Если это не так, моделирование даст бессмысленные результаты.

С другой стороны, при верификации разработчик пытается извлечь параметры системы непосредственно из описания схемы. Например, критический путь сумматора можно определить, изучив схему цепи или ее модель. Преимуществом данного подхода является то, что результат не зависит от выбора пробных сигналов и, предположительно, наиболее надежен. С другой стороны, он основан на ряде неявных предположений, касающихся технологий и методологий проектирования. Возьмем, например, сумматор: определение задержки распространения требует понимания работы логических цепей, составляющих сумматор (например, какая это логика — динамическая или статическая), и определения термина задержка распространения. А нахождение минимальной тактовой частоты синхронной схемы требует определения элементов регистра. Таким образом, существующие инструменты верификации имеют ограниченную область применения и позволяют учесть только часть стилей разработки схем (например, рассмотреть класс однофазных синхронных схем) [1].