Методическое пособие 124

.pdfФГБОУ ВПО «Воронежский государственный технический университет»

Кафедра систем информационной безопасности

МЕТОДИЧЕСКИЕ УКАЗАНИЯ

к практическим занятиям по дисциплине «Архитектура построения и средства защиты СПЦС» для студентов специальности

090302 «Информационная безопасность телекоммуникационных систем» очной формы обучения

Воронеж 2014

Составитель аспирант А.И. Мордовин

УДК 004.056

Методические указания к практическим занятиям по дисциплине «Архитектура построения и средства защиты СПЦС» для студентов специальности 090302 «Информационная безопасность телекоммуникационных систем» очной формы обучения / ФГБОУ ВПО «Воронежский государственный технический университет»; сост. А.И. Мордовин. Воронеж, 2014. 23 с.

Методические указания посвящены исследованию архитектуры, систем команд и методов программирования СПЦС.

Методические указания подготовлены в электронном виде в текстовом редакторе MSWord 2013 и содержатся в файле Мордовин_ПЗ_АПиСЗ СПЦС.pdf.

Ил. 8. Библиогр.:7 назв.

Рецензент д-р техн. наук, проф. А.Г. Остапенко

Ответственный за выпуск зав. кафедрой д-р техн. наук, проф. А.Г. Остапенко

Издается по решению редакционно-издательского совета Воронежского государственного технического университета

© ФГБОУ ВПО «Воронежский государственный технический университет», 2014

Практическая работа №1 Система прерывания микропроцессора

Цель практической работы заключается в исследовании вектора прерываний микропроцессора C8051F120.

Задачи практической работы:

Понять основные способы прерывания;

рассмотреть понятие внешнего прерывания;

изучить работу прерываний таймеров-счетчиков;

написать программу вызова и обработки прерываний.

Теоретические сведения

CIP-51 имеет развитую систему прерываний, поддерживающую в общей сложности 20 источников прерываний с двумя уровнями приоритета. Распределение источников прерываний между встроенными периферийными модулями и внешними входными выводами зависит от конкретного типа МК. Каждый источник прерываний имеет один или несколько связанных с ним флагов прерываний, размещенных в SFR. Когда периферийный модуль или внешний источник прерываний регистрирует событие, удовлетворяющее условию прерывания, соответствующий флаг прерывания устанавливается в 1 [3].

Если прерывание от источника прерываний разрешено, то при установке флага прерывания генерируется запрос прерывания. Как только выполнение текущей команды завершится, будет сгенерирована команда LCALL перехода по предопределенному адресу, откуда начнется исполнение процедуры обслуживания прерывания (interrupt service routine - ISR). Каждая ISR должна заканчиваться командой RETI, которая возвращает управление прерванной программе и приводит к выполнению той команды, которая исполнилась бы, если бы запроса прерывания не было. Если прерывания

неразрешены, флаг прерывания игнорируется и выполнение программы продолжается в нормальном режиме. (Флаг прерывания устанавливается в 1 независимо от того, разрешены прерывания или запрещены) [4].

Прерывание от каждого источника прерываний может быть разрешено или запрещено с помощью соответствующих битов разрешения прерываний в регистрах SFR (IE, IE1 или EIE2). Однако, сначала прерывания необходимо разрешить глобально установкой в 1 бита EA (IE.7), только после этого состояние индивидуальных флагов разрешения прерываний будет иметь силу. Сброс в 0 бита ЕА запрещает прерывания от всех источников прерываний независимо от состояния индивидуальных флагов разрешения прерываний [2].

Некоторые флаги прерываний сбрасываются автоматически аппаратными средствами при переходе к процедуре ISR. Однако большинство флагов прерываний не сбрасываются аппаратно и должны быть сброшены программно до возвращения из процедуры ISR. Если флаг прерывания остается установленным после завершения выполнения команды возврата из прерывания (RETI), то сразу же будет сгенерирован новый запрос прерывания и после завершения выполнения следующей команды произойдет повторный переход к процедуре ISR.

Данное семейство МК поддерживает 20 источников прерываний. Программа может симулировать прерывание установкой в 1 любого флага прерывания. Если прерывание для этого флага разрешено, будут сгенерирован запрос прерывания и произойдет переход по адресу процедуры ISR, связанной с этим флагом прерывания [3].

Два внешних источника прерываний (/INT0 и /INT1) настраиваются как входы с низким активным уровнем, чувствительные к уровню или к фронту сигнала, в зависимости от состояния битов IT0 (TCON.0) и IT1 (TCON.2).

Биты IE0 (TCON.1) и IE1 (TCON.3) служат флагами прерываний для внешних прерываний /INT0 и /INT1 соответственно. Если вход /INT0 или /INT1 настроен как

2

чувствительный к фронту, то соответствующий флаг прерывания автоматически сбрасывается аппаратными средствами при переходе к процедуре ISR. Если вход /INT0 или /INT1 настроен как чувствительный к уровню, то соответствующий флаг прерывания отслеживает (повторяет) состояние входного вывода внешнего прерывания. Внешний источник прерывания должен удерживать на этом входе активный уровень до тех пор, пока запрос прерывания не будет распознан. Затем необходимо деактивировать запрос прерывания до окончания выполнения процедуры ISR, иначе будет сгенерирован другой запрос прерывания [1].

Каждому источнику прерываний можно программно присвоить один из двух уровней приоритета: низкий или высокий. Процедура ISR с низким приоритетом может быть прервана прерыванием с высоким приоритетом. Прерывание с высоким приоритетом не может быть прервано. Каждое прерывание имеет связанный с ним бит приоритета в регистрах SFR (IP-EIP2), используемый для настройки уровня приоритета. По умолчанию присваивается низкий приоритет. Если два прерывания происходят одновременно, прерывание с более высоким приоритетом обслуживается первым [2].

Время реакции на прерывание зависит от состояния процессорного ядра в момент возникновения прерывания. Опрос флага прерывания и декодирование приоритета осуществляется каждый системный тактовый цикл. Поэтому, наименьшее возможное время реакции на прерывание составляет 5 тактовых циклов: 1 цикл для определения прерывания и 4 цикла для выполнения команды LCALL перехода к процедуре ISR. Если происходит «промах кэша», то потребуются дополнительные тактовые циклы (подробная информация приведена в разделе 16). Если в момент выполнения команды RETI появляется прерывание, то до выполнения команды LCALL перехода на процедуру обслуживания этого прерывания будет исполнена одна команда основной программы. Поэтому максимальное время реакции на прерывание (если в настоящий момент не

3

обслуживается другое прерывание или если новое прерывание имеет более высокий приоритет) будет тогда, когда выполняется команда RETI, а следом за ней должна выполняться команда DIV, и произошел «промах кэша». Если выполняется процедура ISR для прерывания с равным или более высоким приоритетом, новое прерывание не будет обслужено до тех пор, пока не завершится текущая процедура ISR, включая команду RETI и следующую команду [2,4].

Задание для практической работы

Используя функции вызова LCALL, осуществить инициализацию и составление вектора прерываний микропроцессора C8051F120, включая обработку внешних прерываний, прерываний четырех таймеров, прерываний по АЦП0 и АЦП1, прерываний по аналоговому компаратору и прерываний от интерфейса УАПП. Установить приоритет для каждого из прерываний.

Контрольные вопросы:

Перечень вопросов для защиты результатов работы:

1.Источники прерываний и их количество.

2.Основы программной реализации прерывания.

3.Программный запрет прерываний.

4.Внешние прерывания микропроцессора.

5.Вектор прерываний.

6.Флаги прерываний.

7.Приоритет прерываний.

8.Время реакции микропроцессора на прерывание.

4

Практическая работа №2 Приемы работы с портами ввода-вывода

Цель практической работы заключается в исследовании возможностей использования портов ввода-вывода микропроцессора.

Задачи практической работы:

рассмотреть функции портов ввода-вывода;

определить область применения портов ввода вывода;

реализовать программный код, осуществляющий запись и чтение данных с портов ввода-вывода.

Теоретические сведения

Данные МК представляют собой полностью интегрированные на одном кристалле системы для обработки смешанных сигналов, которые имеют 64 (МК в 100-выв. корпусе типа TQFP) или 32 (МК в 64-выв. корпусе типа TQFP) цифровых вывода входа/выхода, организованные в 8- разрядные порты. Все порты доступны в режиме как побитной, так и побайтной адресации через соответствующие регистры данных портов. Каждый из выводов портов имеет слаботоковые подтягивающие резисторы и может быть настроен как выход с открытым стоком или цифровой двухтактный выход [3].

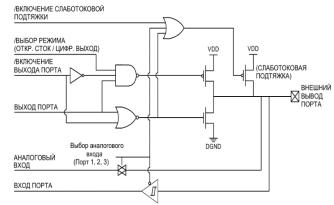

Допустимое напряжение на выводах всех портов составляет 5В. Структурная схема ячейки порта ввода/вывода показана на рис. 1.

5

Рис.1. Структурная схема ячейки порта ввода-вывода

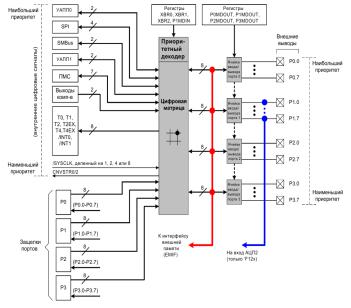

Микроконтроллеры имеют различные цифровые ресурсы, которые доступны через четыре младших порта ввода/вывода: Р0, Р1, Р2 и Р3. Каждый из выводов портов Р0, Р1, Р2 и Р3 может быть определен либо как вывод ввода/вывода общего назначения, либо как вывод, управляемый внутренними цифровыми ресурсами (например, УАПП0 или /INT1), как показано на рис. 2. Разработчик системы определяет, какие цифровые ресурсы будут назначены внешним выводам, ограничиваясь только количеством доступных выводов. Гибкость при распределении ресурсов достигается благодаря использованию приоритетного декодера матрицы. Следует иметь ввиду, что состояние вывода порта ввода/вывода всегда можно прочитать из соответствующего регистра данных независимо от того, как функционирует этот вывод: как вывод ввода/вывода общего назначения или как вывод, назначенный какому-либо внутреннему цифровому ресурсу. Выводы Порта 1 могут использоваться как аналоговые входы АЦП2 [3].

Как младшие, так и старшие порты могут использоваться для интерфейса внешней памяти, сигналы которого активны во время выполнения команды MOVX, обращающейся по адресу, расположенному во внешней (невстроенной) памяти.

6

Рис. 2. Функциональная схема портов ввода-вывода

Приоритетный декодер матрицы, или «матрица», распределяет и назначает выводы портов Р3 – Р0 цифровым периферийным модулям (УАПП, SMBus, ПМС, таймеры и т.д.) микроконтроллера, используя для этого приоритеты. Выводы портов распределяются, начиная с порта Р0.0 и (если необходимо) до порта Р3.7. Цифровые периферийные модули назначаются выводам портов в соответствии с их приоритетом. УАПП0 имеет наивысший приоритет, CNVSTR2 имеет самый низкий приоритет [2].

Так как УАПП0 имеет наивысший приоритет, то его выводы всегда будут отображаться на порты Р0.0 и Р0.1, когда бит UART0EN установлен в 1. Если биты подключения цифровых модулей не установлены в 1, то их порты не доступны на внешних выводах портов МК. Важно также иметь ввиду, что, если выбраны последовательные порты (т.е. SMBus, SPI, УАПП), то матрица распределяет все выводы,

7

ассоциированные с ними. Нельзя, например, назначить вывод RX0 модуля УАПП0 и не назначить вывод TX0 этого же модуля [3].

Назначение внешних выводов микроконтроллера для каждой комбинации подключенных периферийных модулей будет уникальным. Все выводы портов Р0 – Р3, нераспределенные при помощи матрицы, могут быть доступны как выводы ввода/вывода общего назначения путем чтения и записи соответствующих регистров данных портов, которые доступны как в побитном, так и в побайтном режимах адресации. Состояния выходных драйверов выводов портов, которые распределены матрицей и управляются цифровыми периферийными модулями, определяются этими модулями. Запись регистров данных этих портов (или распределенных матрицей битов портов) не будет влиять на состояние этих выводов [2].

Чтение регистра данных порта (или бита порта) всегда возвратит в качестве результата логическое состояние на выводе порта независимо оттого, распределен данный порт матрицей или нет. Исключением являются команды типа чтение-модификация-запись (ANL, ORL, XRL, JBC, CPL, INC, DEC, DJNZ, CLR, SETВ и битовые команды MOV). В течение цикла чтения команд типа чтение-модификация-запись считывается содержимое регистра данных порта, а не логическое состояние самих выводов портов. Следует иметь ввиду, что если при работе на тактовой частоте более 50 МГц состояние вывода устанавливается и затем сразу же считывается (т.е. когда за командой записи сразу же следует команда чтения), то из-за задержки распространения сигнала команда чтения может возвратить значение, соответствующее предыдущему состоянию вывода [1].

Так как регистры матрицы влияют на подключение внутренних периферийных модулей к внешним выводам МК, то они обычно настраиваются в процессе инициализации системы до настройки самих периферийных модулей. После первоначальной настройки регистры матрицы обычно не

8