- •Исследование узлов комплексных систем управления

- •Часть 4

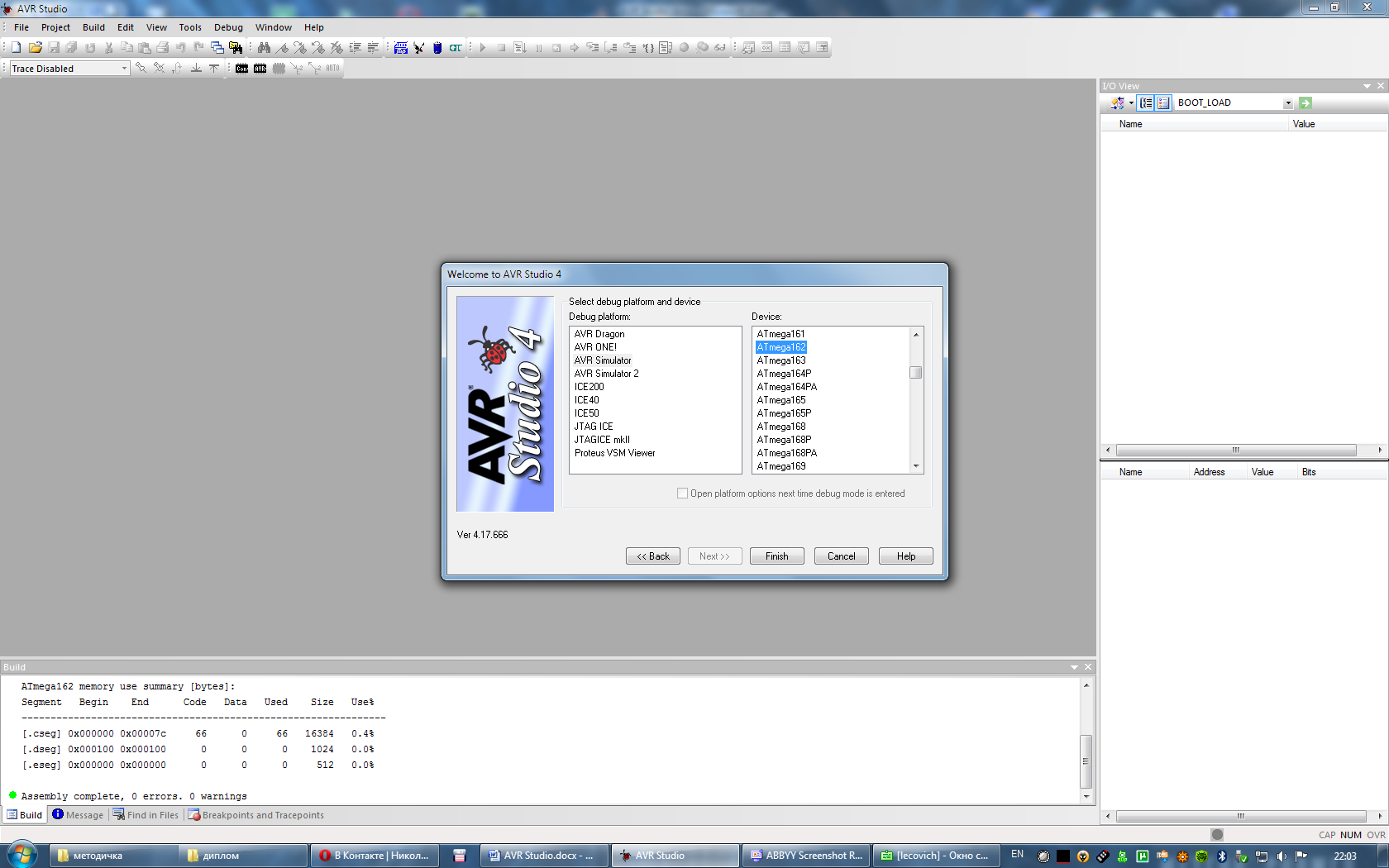

- •Интегрированная среда разработки avr Studio

- •2. Порядок выполнения работы Контрольные вопросы по допуску к работе

- •2.1. Предварительное задание

- •2.2. Рабочее задание

- •3. Итоговые вопросы

- •Описание платы управления, используемой в лабораторной работе

- •Описание системы отладки

- •2. Порядок выполнения работы Контрольные вопросы по допуску к работе

- •Предварительное задание

- •Рабочее задание

- •Приложение 1 Система команд микроконтроллера aTmega

- •Группа команд логических операций

- •Группа команд арифметических операций

- •Группа команд операций с битами

- •Группа команд пересылки данных

- •Группа команд передачи управления

- •Dseg - Сегмент данных

- •Endmacro - Конец макроса

- •Exit - Выйти из файла

- •Include - Вложить другой файл

- •List - Включить генерацию листинга

- •Macro - Начало макроса

- •Nolist - Выключить генерацию листинга

- •Приложение 3 Приведение вкладки в состояние Docking

- •Приложение 4 Названия и номера регистров и портов avr Classic и Mega

- •Регистры управления

- •Библиографический список

- •Содержание

- •Часть 4

- •394026 Воронеж, Московский просп., 14

ФГБОУ ВПО "Воронежский государственный технический университет"

Кафедра электропривода, автоматики и управления в технических системах

Исследование узлов комплексных систем управления

МЕТОДИЧЕСКИЕ УКАЗАНИЯ

к выполнению лабораторных работ

по дисциплине «Комплексная автоматизация на базе микропроцессорных средств» для студентов направления 140400.68 «Электроэнергетика и электротехника» (магистерская программа подготовки «Электроприводы и системы управления электроприводов») очной формы обучения

Часть 4

Воронеж 2013

Составители: канд. техн. наук М.И. Герасимов

инженер Н.С. Лесных

УДК 681.3-181.48

Исследование узлов комплексных систем управления: методические указания к выполнению лабораторных работ по дисциплине «Комплексная автоматизация на базе микропроцессорных средств» для студентов направления 140400.68 «Электроэнергетика и электротехника» (магистерская программа подготовки «Электроприводы и системы управления электроприводов») очной формы обучения. Ч. 4 / ФГБОУ ВПО «Воронежский государственный технический университет»; сост. М.И. Герасимов, Н.С. Лесных. Воронеж, 2013. 63 с.

Методические указания содержат теоретические сведения об устройстве и принципах работы исследуемых узлов, способах исследования и соответствующих программных средствах, предварительное и рабочее задания, определяющие порядок исследования, контрольные и итоговые вопросы.

Предназначены для магистрантов 2 курса очной формы обучения.

Методические указания подготовлены в электронном виде в текстовом редакторе MS Word и содержатся в файле МУ_лаб_КА_4.doc.

Табл. 13. Ил. 15. Библиогр.: 8 назв.

Рецензент канд. техн. наук, доц. А.В. Романов

Ответственный за выпуск зав. кафедрой д-р техн. наук, проф. В.Л. Бурковский

Издается по решению редакционно-издательского совета Воронежского государственного технического университета

©

Лабораторная работа № 17

ИЗУЧЕНИЕ СРЕДЫ РАЗРАБОТКИ МИКРОКОНТРОЛЛЕРНЫХ СИСТЕМ

Цель работы – изучить устройство и систему команд микроконтроллеров Atmel серии ATmega с помощью интегрированной среды разработки AVR Studio.

1. Теоретические сведения

В качестве объекта изучения был выбран микроконтроллер (МК) ATmega 162, который будет использован как в текущей, так и в следующей лабораторной работе.

Структура МК семейства ATmega 162

ATmega162 – экономичный 8-разрядный микроконтроллер, основанный на усиленной AVR RISC архитектуре /1/. ATmega162 обеспечивает производительность 1 млн. оп. в секунду (MIPS) на 1 МГц синхронизации за счет выполнения большинства инструкций за один машинный цикл и позволяет оптимизировать потребление энергии за счет изменения частоты синхронизации.

В ядре AVR сочетаются богатый набор инструкций с 32 рабочими регистрами общего назначения. Все 32 регистра непосредственно подключены к АЛУ (арифметико-логическое устройство), что позволяет указывать два регистра в одной инструкции и выполнять ее за один цикл. Данная архитектура обладает большей эффективностью кода и в 10 раз большей производительностью по сравнению с CISC микроконтроллерами.

ATmega162 обладает следующими возможностями: 16 кбайт внутрисхемно программируемой флэш-памяти с возможностью чтения во время записи, 512 байт ЭППЗУ, 1 кбайт статического ОЗУ, внешний интерфейс памяти, 35 линий ввода-вывода, 32 рабочих регистра общего назначения, JTAG интерфейс для сканирования адресного пространства, встроенная система отладки и программирования, четыре универсальных таймера-счетчика с режимами сравнения, внутренние и внешние запросы на прерывание, два последовательных программируемых УСАПП, программируемый сторожевой таймер с внутренним генератором, последовательный порт SPI и пять программно настраиваемых режимов управления энергопотреблением.

Устройство выпускается по разработанной Atmel технологии энергонезависимой памяти высокой емкости. Встроенная ISP флэш-память может внутрисхемно перепрограммироваться через последовательный интерфейс SPI, обычным программатором энергонезависимой памяти или запущенной программой в секторе начальной загрузки AVR ядра. Программа в секторе начальной загрузки может использовать любой интерфейс для записи программы и выполняется даже при обновлении флэш-памяти приложения, обеспечивая действительную возможность чтения во время записи. В результате комбинирования 8-разрядного RISC ЦПУ с внутрисхемно самопрограммируемой флэш-памятью на одном кристалле ATmega162 является мощным микроконтроллером, обеспечивающим высокую универсальность и обладающим низкой стоимостью, что делает его применение идеальным для построения встроенных систем управления.

ATmega162 поддерживается полным набором инструментальных и программных средств для разработки приложений. В их числе Cи-компиляторы, макроассемблеры, программные отладчики / симуляторы, внутрисхемные эмуляторы, оценочные наборы.

Структурная схема микроконтроллеров семейства Mega приведена на рис. 17.1. Следует заметить, что на этом рисунке изображена схема наиболее совершенного на сегодняшний день представителя семейства, ATmega128x. При рассмотрении других моделей необходимо принимать во внимание присущие им ограничения, такие как наличие тех или иных периферийных устройств и использование портов ввода/вывода этими устройствами. В частности, используемая в данной работе модель ATmega 162 содержит два восьми- и два шестнадцатиразрядных таймера/счетчика. Подробное описание одного из них – Т/С1, его регистров и флагов приведено в методических указаниях к предыдущей лабораторной работе /2/.

Для исследования организации портов и таймеров микроконтроллеров AVR в предыдущих работах проводилось программирование средствами графической среды Algorithm Builder /2/. В данной и последующей работе будет использована иная среда разработки – AVR Studio /3/. В ней составляется не алгоритм, а собственно программа необходимых действий на языке ассемблера AVR. Тем не менее этап разработки алгоритма и анализа результата обязательно должен предшествовать собственно программированию.

Рис. 17.1. Структурная схема микроконтроллеров семейства Mega