ФУУМЭ / 7201_lab6__zashita

.docxМИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра РТЭ

ЗАЩИТА

лабораторной работы №6

по дисциплине «Функциональные узлы и устройства микроэлектроники»

Тема: Исследование интегральной логической схемы ТТЛ

Студент гр. 7201 |

|

Шапошников В.А. |

Преподаватель |

|

Тупицын А.Д. |

Санкт-Петербург

2020

Вопрос 3. Понятие и методика определение помехоустойчивости ИС.

Ответ:

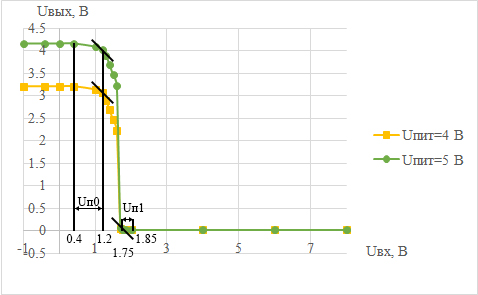

Помехоустойчивость определяет значение напряжения, которое может быть подано на вход интегральной схемы относительно уровней 0 или 1, не вызывая ее ложного срабатывания, то есть переход из состояния 1 в состояние 0 или наоборот. Помехоустойчивость ИС определяют относительно уровней логического нуля (Uп0) и логической единицы (Uп1).

Данный параметр определяется по передаточной характеристике (Uвых=f(Uвх). Для начала определяются точки А и В, которые являются местом соприкосновения касательных, проведенных под углом 45° к верхним и нижним изгибам крайних кривых передаточных характеристик. Затем определяют значения помехоустойчивости. Ниже приведена передаточная характеристика из лабораторной работы (Рис.1), на ней были отмечены параметры Uп0 и Uп1.

Рис.1 Передаточные характеристики для разных напряжений питания