ФУУМЭ / 7201_lab6_

.docxМИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра РТЭ

отчет

по лабораторной работе №6

по дисциплине «Функциональные узлы и устройства микроэлектроники»

Тема: исследование интегральной логической схемы ттл

Студент гр. 7201 |

|

Казмаджи А |

|

|

Степнов Д.Е. |

|

|

Пастушенко И.С. |

Преподаватель |

|

Тупицын А.Д. |

Санкт-Петербург

2020

Цель работы: Ознакомление с принципом действия, схемотехническими особенностями, конструкцией и назначением логической схемы типа ТТЛ и определение ее основных параметров и характеристик.

Тип и параметры объекта исследования

В ходе данной лабораторной работы исследуется логическая интегральная микросхема ТТЛ типа К155ЛА3. Микросхема К155ЛА3, как и ее импортный аналог SN7400, содержат в себе четыре логических элемента 2И – НЕ в корпусе DIP-14.

Микросхемы К155ЛА3 и 7400 созданы на базе ТТЛ, поэтому - напряжение 7 вольт является для них предельно максимальным. При превышении этого значения прибор очень быстро сгорает.

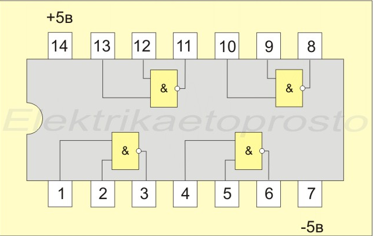

Схема расположения выходов и входов логических элементов (распиновка) К155ЛА3 выглядит следующим таким образом.

Рис.1 – Расположение выводов К155ЛАЗ

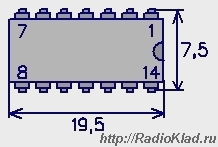

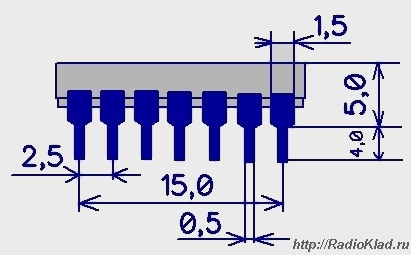

Рис. 2 – Габариты микросхемы

Рис.3 – Размеры корпуса микросхемы К155ЛАЗ.

Параметры К155ЛАЗ:

Таблица 1 – Наименование параметров К155ЛАЗ.

Наименование параметра |

Значение |

Напряжение питания |

5В+-5% |

Максимальное напряжение лог. "0" |

<0.4В |

минимальное напряжение лог "1" |

>2.4В |

Ток потребеления при лог. "0" и Uпит=5В |

<22mA |

Ток потребеления при лог. "1" и Uпит=5В |

<8mA |

Входной ток низкого уровня |

<1,6 mA |

Входной ток высокого уровня |

<0,04 mA |

Входной пробивной ток |

<1 mA |

Ток КЗ |

18-55 mA |

Потребляемая мощность одного элемента |

<19,7mВт |

Время задержки распространения сигнала при включении |

<15нс |

Время задержки распространения сигнала при выключении |

<22нС

|

Помехоустойчивость |

<0.4В |

Таблица 2 – Таблица истинности для К155ЛАЗ:

Вход А |

Вход В |

Выход Q |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

Рис.

4 – Электрическая

схема К155ЛАЗ

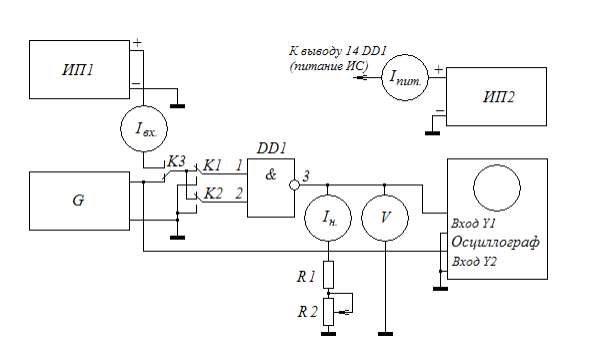

Рис. 5 – Блок-схема измерительной установки

Обработка результатов

Построим передаточные характеристики, при Uп=4 В и 5 В соответственно и определим помехоустойчивость:

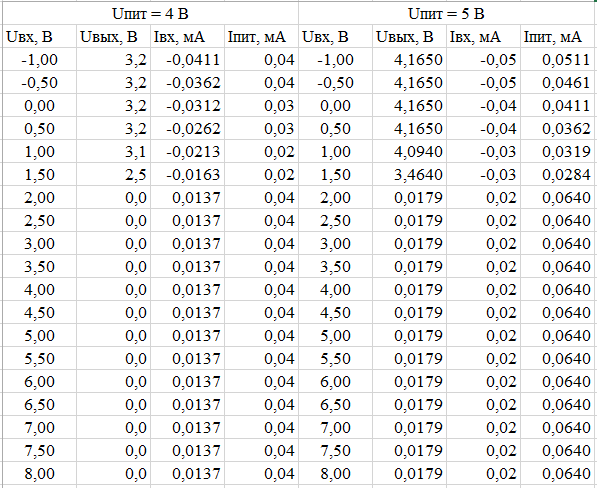

Таблица 3 – Полученные данные моделирования

Рис. 6 Передаточные характеристики для разных напряжениях питания

Построим входные характеристики, при Uп=4 В и 5 В соответственно

Рис. 7 Входные характеристики для разных напряжениях питания

Построим зависимость тока питания, при Uп=4 В и 5 В соответственно

Рис. 8 Зависимость тока питания от входного напряжения

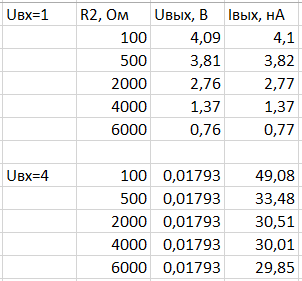

Построим нагрузочную характеристику при напряжении питания 5 в и высоком и низком логическом уровне выходного напряжения:

Примем входное напряжение Uвх= 1 В, при котором на выходе высокий логический уровень, а для низкого уровня примем Uвх= 4 В

Таблица 5 Нагрузочная характеристика

Рис. 9 Нагрузочная характеристика высокого лог. уровня

Рис. 10 Нагрузочная характеристика низкого лог. уровня

Определим динамические параметры схемы:

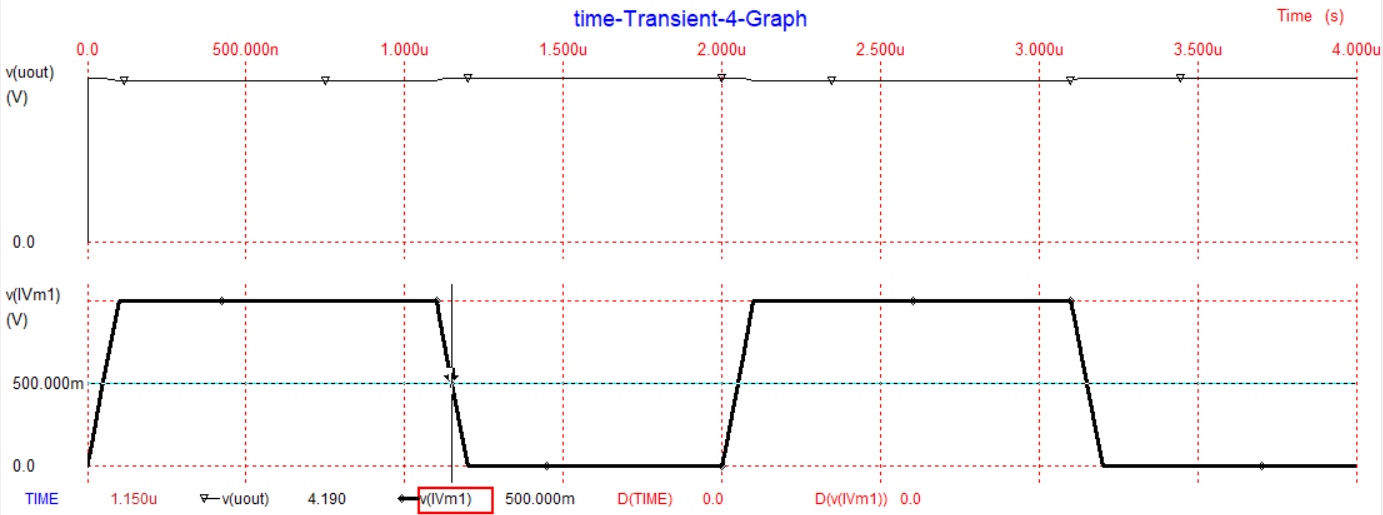

Рис. 11 Временная зависимость выходного и входного напряжений при амплитуде Uвх= 1 В (верхняя и нижняя кривая соответственно)

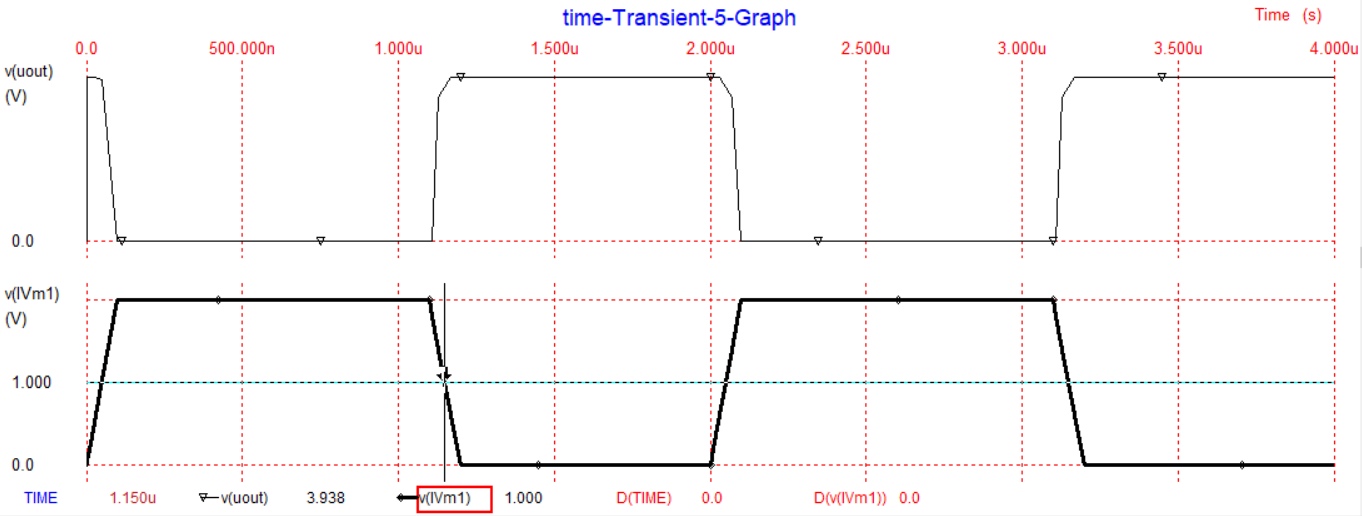

Рис. 12 Временная зависимость выходного и входного напряжений при амплитуде Uвх= 2 В

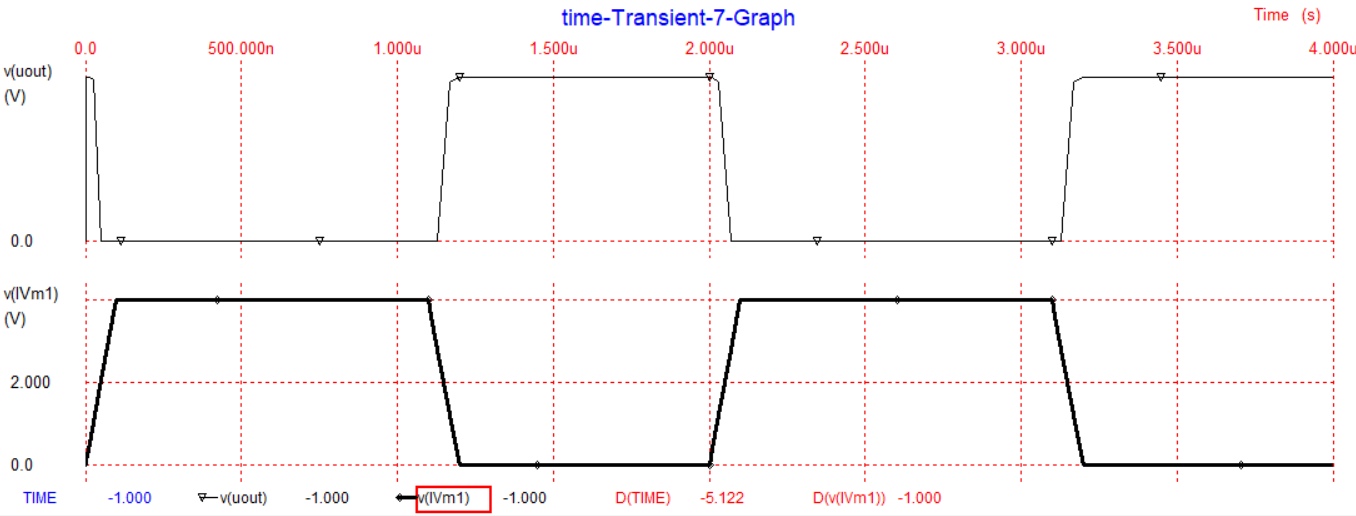

Рис. 13 Временная зависимость выходного и входного напряжений при амплитуде Uвх= 3 В

Рис. 14 Временная зависимость выходного и входного напряжений при амплитуде Uвх= 4 В

Рис. 15 Временная зависимость выходного и входного напряжений при амплитуде Uвх= 5 В

Определим величины задержек τ10 и τ01 для каждой амплитуды входных напряжений.

Таблица 7

Uвх, В |

t10, нс |

t01, нс |

1 |

25,518 |

21,609 |

2 |

24,901 |

22,701 |

3 |

23,517 |

21,531 |

4 |

22,532 |

20,17 |

5 |

22,438 |

20,137 |

Рис. 16 Зависимость времени задержки фронтов и спадов в зависимости от амплитуды

Выводы: в данной лабораторной работе была исследована схема К155ЛАЗ – 2И-НЕ. Были построены ее передаточные, входные, нагрузочные, а также зависимость тока питания от входного напряжения. По передаточным характеристикам была определена помехоустойчивость. Также были определены динамические параметры исследуемой схемы и рассчитаны величины задержек.