- •Features

- •Pin Configuration

- •Disclaimer

- •Description

- •Pin Descriptions

- •AVCC

- •Port A (PA7..PA0)

- •Port B (PB7..PB0)

- •XTAL1

- •XTAL2

- •SRAM Data Memory

- •I/O Direct

- •Data Direct

- •Data Indirect with Displacement

- •Data Indirect

- •EEPROM Data Memory

- •I/O Memory

- •Status Register – SREG

- •Stack Pointer – SP

- •Reset Sources

- •Power-on Reset

- •External Reset

- •Brown-out Detection

- •Watchdog Reset

- •Clock Systems and their Distribution

- •CPU Clock – clkCPU

- •I/O Clock – clkI/O

- •Flash Clock – clkFLASH

- •ADC Clock – clkADC

- •Internal PLL for Fast Peripheral Clock Generation – clkPCK

- •Clock Sources

- •Crystal Oscillator

- •External RC Oscillator

- •External Clock

- •Interrupt Handling

- •Interrupt Response Time

- •External Interrupt

- •Pin Change Interrupt

- •Idle Mode

- •ADC Noise Reduction Mode

- •Power-down Mode

- •Standby Mode

- •Analog to Digital Converter

- •Analog Comparator

- •Brown-out Detector

- •Internal Voltage Reference

- •Watchdog Timer

- •Port Pins

- •Timer/Counters

- •Timer/Counter0 Prescaler

- •Timer/Counter1 Prescaler

- •8-bit Timer/Counter0

- •Timer/Counter0 – TCNT0

- •8-bit Timer/Counter1

- •Timer/Counter1 – TCNT1

- •Timer/Counter1 in PWM Mode

- •Watchdog Timer

- •Overview

- •Register Descriptions

- •USI Data Register – USIDR

- •USI Status Register – USISR

- •USI Control Register – USICR

- •Functional Descriptions

- •Three-wire Mode

- •SPI Slave Operation Example

- •Two-wire Mode

- •Start Condition Detector

- •Alternative USI Usage

- •4-bit Counter

- •12-bit Timer/Counter

- •Software Interrupt

- •Analog Comparator

- •Analog to Digital Converter

- •Features

- •Operation

- •ADC Conversion Result

- •ADLAR = 0

- •ADLAR = 1

- •I/O Ports

- •Introduction

- •Configuring the Pin

- •Reading the Pin Value

- •Alternate Port Functions

- •Alternate Functions of Port A

- •Alternate Functions Of Port B

- •Register Description for I/O Ports

- •Port A Data Register – PORTA

- •Port B Data Register – PORTB

- •Fuse Bits

- •Latching of Fuses

- •Signature Bytes

- •Calibration Byte

- •Signal Names

- •Parallel Programming

- •Enter Programming Mode

- •Chip Erase

- •Programming the Flash

- •Programming the EEPROM

- •Reading the Flash

- •Reading the EEPROM

- •Programming the Lock Bits

- •Reading the Signature Bytes

- •Reading the Calibration Byte

- •Serial Downloading

- •Data Polling Flash

- •Data Polling EEPROM

- •Electrical Characteristics

- •Absolute Maximum Ratings*

- •External Clock Drive Waveforms

- •External Clock Drive

- •ADC Characteristics – Preliminary Data

- •ATtiny26/L Register Summary

- •Ordering Information(1)

- •Packaging Information

- •Data Sheet Change Log for ATtiny26

- •Changes from Rev. 1477A-03/02 to Rev. 1477B-04/02

- •Table of Contents

ATtiny26(L)

ATtiny26(L)

Description

The ATtiny26/L is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the ATtiny26/L achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

The AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers. The ATtiny26/L has a high precision ADC with up to 11 single ended channels and 8 differential channels. Seven differential channels have an optional gain of 20x. Four out of the seven differential channels, which have the optional gain, can be used at the same time. The ATtiny26/L also has a high frequency 8-bit PWM module with two independent outputs. Two of the PWM outputs have inverted non-overlapping output pins ideal for synchronous rectification. The Universal Serial Interface of the ATtiny26/L allows efficient software implementation of TWI (Two-wire Serial Interface) or SM-bus interface. These features allow for highly integrated battery charger and lighting ballast applications, low-end thermostats, and firedetectors, among other applications.

The ATtiny26/L provides 2K bytes of Flash, 128 bytes EEPROM, 128 bytes SRAM, up to 16 general purpose I/O lines, 32 general purpose working registers, two 8-bit Timer/Counters, one with PWM outputs, internal and external Oscillators, internal and external interrupts, programmable Watchdog Timer, 11-channel, 10-bit Analog to Digital Converter with two differential voltage input gain stages, and four software selectable power saving modes. The Idle mode stops the CPU while allowing the Timer/Counters and interrupt system to continue functioning. The ATtiny26/L also has a dedicated ADC Noise Reduction mode for reducing the noise in ADC conversion. In this sleep mode, only the ADC is functioning. The Power-down mode saves the register contents but freezes the oscillators, disabling all other chip functions until the next interrupt or hardware reset. The Standby mode is the same as the Power-down mode, but external oscillators are enabled. The wakeup or interrupt on pin change features enable the ATtiny26/L to be highly responsive to external events, still featuring the lowest power consumption while in the Power-down mode.

The device is manufactured using Atmel’s high density non-volatile memory technology. By combining an enhanced RISC 8-bit CPU with Flash on a monolithic chip, the ATtiny26/L is a powerful microcontroller that provides a highly flexible and cost effective solution to many embedded control applications.

The ATtiny26/L AVR is supported with a full suite of program and system development tools including: Macro assemblers, program debugger/simulators, In-circuit emulators, and evaluation kits.

3

1477B–AVR–04/02

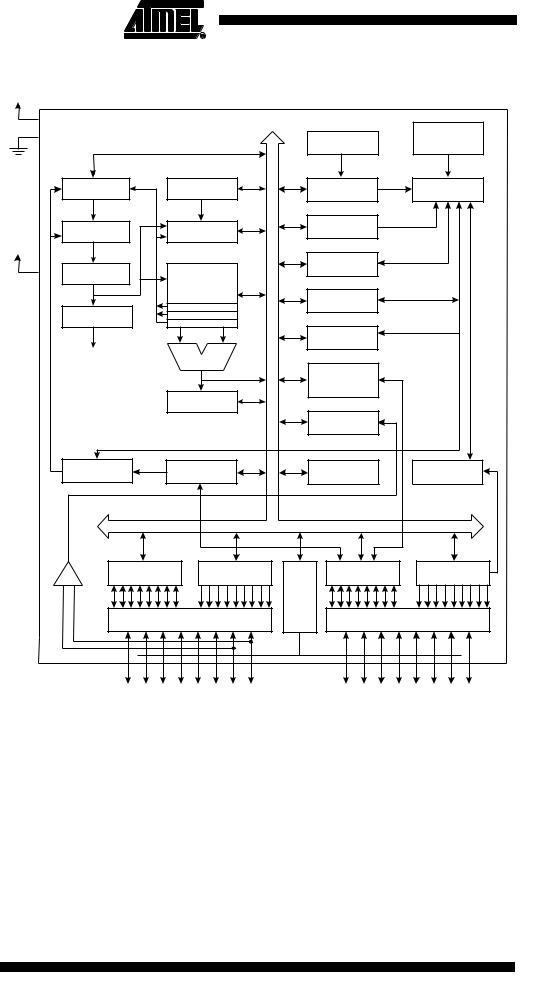

Block Diagram

Figure 1. The ATtiny26/L Block Diagram

VCC

8-BIT DATA BUS

|

|

|

|

|

|

|

INTERNAL |

INTERNAL |

|

|

|

|

|

|

|

CALIBRATED |

|

|

|

|

|

|

|

|

OSCILLATOR |

OSCILLATOR |

GND |

|

|

|

|

|

|

|

|

|

PROGRAM |

|

STACK |

|

WATCHDOG |

TIMING AND |

||

|

COUNTER |

|

POINTER |

|

TIMER |

CONTROL |

||

|

PROGRAM |

|

|

|

MCU CONTROL |

|

||

|

|

SRAM |

|

REGISTER |

|

|||

|

|

FLASH |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

AVCC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MCU STATUS |

|

|

INSTRUCTION |

|

GENERAL |

|

REGISTER |

|

||

|

REGISTER |

|

PURPOSE |

|

|

|

||

|

|

|

|

|

REGISTERS |

|

|

|

|

|

|

|

|

|

|

TIMER/ |

|

|

INSTRUCTION |

|

X |

|

COUNTER0 |

|

||

|

|

Y |

|

|

|

|||

|

|

DECODER |

|

Z |

|

|

|

|

|

|

|

|

|

|

|

TIMER/ |

|

|

|

|

|

|

|

|

COUNTER1 |

|

|

CONTROL |

|

ALU |

|

|

|

||

|

|

LINES |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

UNIVERSAL |

|

|

|

|

|

|

|

|

SERIAL |

|

|

|

|

|

|

STATUS |

|

INTERFACE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

REGISTER |

|

|

|

|

|

|

|

|

|

|

INTERRUPT |

|

|

|

|

|

|

|

|

UNIT |

|

|

PROGRAMMING |

ISP INTERFACE |

|

EEPROM |

OSCILLATORS |

|||

|

|

LOGIC |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

ANALOG COMPARATOR |

DATA REGISTER |

DATA DIR. |

ADC |

DATA REGISTER |

DATA DIR. |

|

+ |

- |

|

PORT A |

REG.PORT A |

|

PORT B |

REG.PORT B |

|

|

|

|

|

|

|

|||

PORT A DRIVERS |

PORT B DRIVERS |

PA0-PA7 |

PB0-PB7 |

4 ATtiny26(L)

1477B–AVR–04/02