Электроника 2.1 / Лабораторная №5

.docxМИНИСТЕРСТВО НАУКИ И ВЫСШЕГО ОБРАЗОВАНИЯ РОССИЙСКОЙ ФЕДЕРАЦИИ

Федеральное государственное автономное образовательное учреждение высшего образования

«НАЦИОНАЛЬНЫЙ

ИССЛЕДОВАТЕЛЬСКИЙ ТОМСКИЙ ПОЛИТЕХНИЧЕСКИЙ

УНИВЕРСИСТЕТ»

«НАЦИОНАЛЬНЫЙ

ИССЛЕДОВАТЕЛЬСКИЙ ТОМСКИЙ ПОЛИТЕХНИЧЕСКИЙ

УНИВЕРСИСТЕТ»

Инженерная школа энергетики Направление – 13.03.02

Электроэнергетика и электротехника

Отделение электроэнергетики и электротехники

«Исследование триггеров на интегральных микросхемах»

Отчет по лабораторной работе №5 по дисциплине

«Электроника 2.1»

Исполнители: |

|

|

студенты группы 5А8Д |

|

Нагорнов А.В. Егоров Е.В. Сучков М.А. Дурникин С.О. |

|

|

|

Руководитель: |

|

|

преподаватель |

Боловин Е. В. |

|

Томск - 2021

Цель работы: экспериментальное исследование работы триггеров, выполненных на интегральных микросхемах, и закрепление знаний по последовательностной цифровой логике.

Краткие теоретические сведения:

Подавляющее большинство цифровых устройств содержит в качестве основных элементов различные типы триггеров.

Триггерами или точнее триггерными системами называют большой класс электронных устройств, обладающих способностью длительно находиться в одном из двух устойчивых состояний и чередовать их под воздействием внешних сигналов. Каждое состояние триггера легко распознается по значению выходного напряжения.

Входы триггеров и сигналы, подаваемые на них, делятся на информационные – управляющие состоянием триггера и вспомогательные – служащие для предварительной установки триггера в заданное состояние и его синхронизацию.

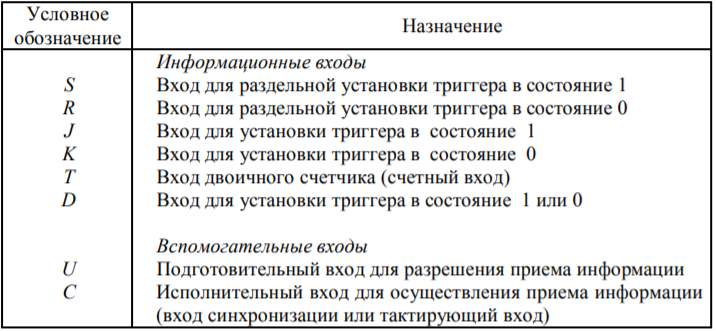

Таблица 1 – Расшифровка обозначений триггеров

Ход работы:

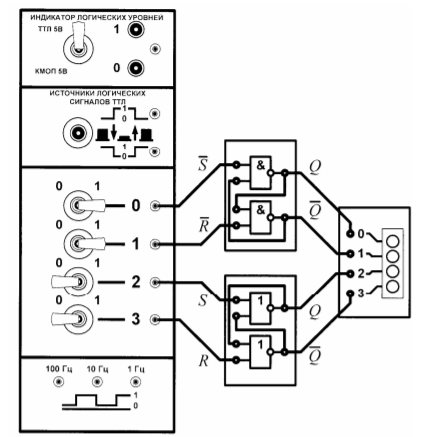

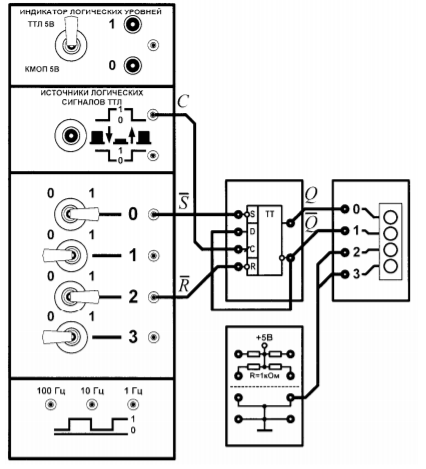

Собираем схему тестирования RS-триггера на элементах И-НЕ (ИЛИ-НЕ) и убедимся, что они функционируют в соответствии с их назначением.

Рисунок 1 – Схема тестирования RS-триггеров

Результаты исследования триггера занесём в таблицу 2.

Таблица 2

RS-триггер на И-НЕ |

|||

|

|

|

|

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

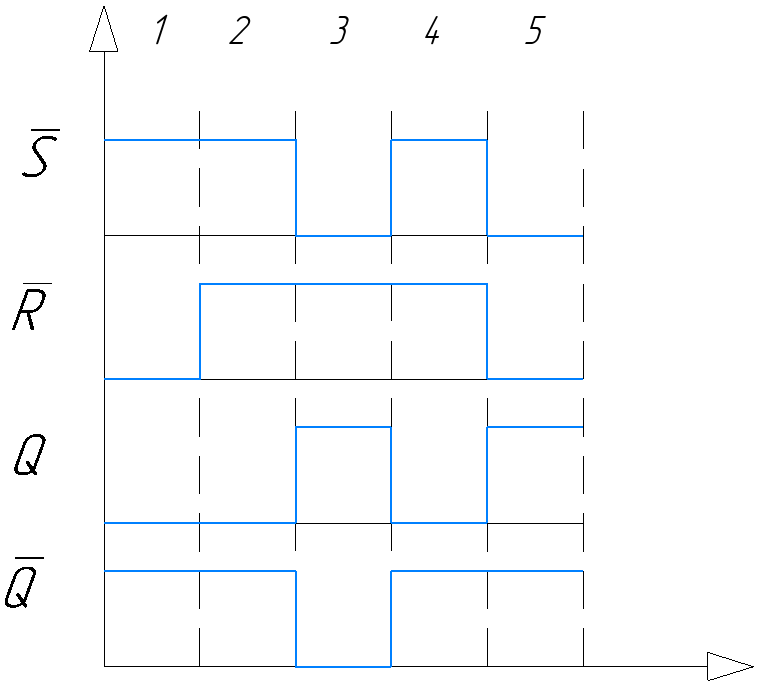

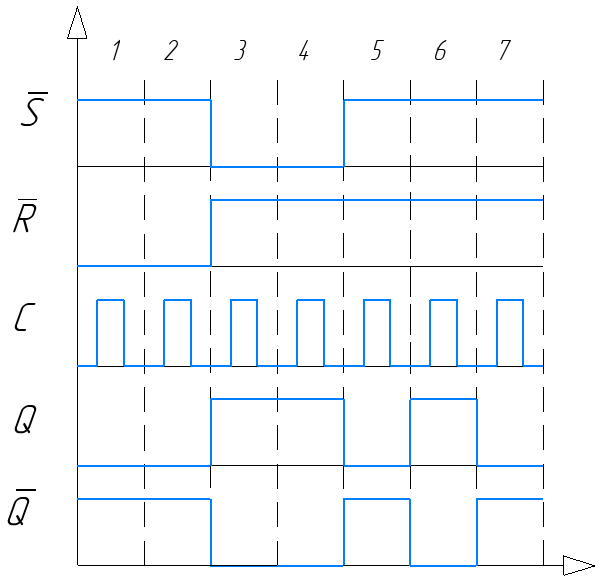

Рисунок 2 – Временная диаграмма RS-триггер на И-НЕ

Таблица 3

RS-триггер на ИЛИ-НЕ |

|||

|

|

|

|

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

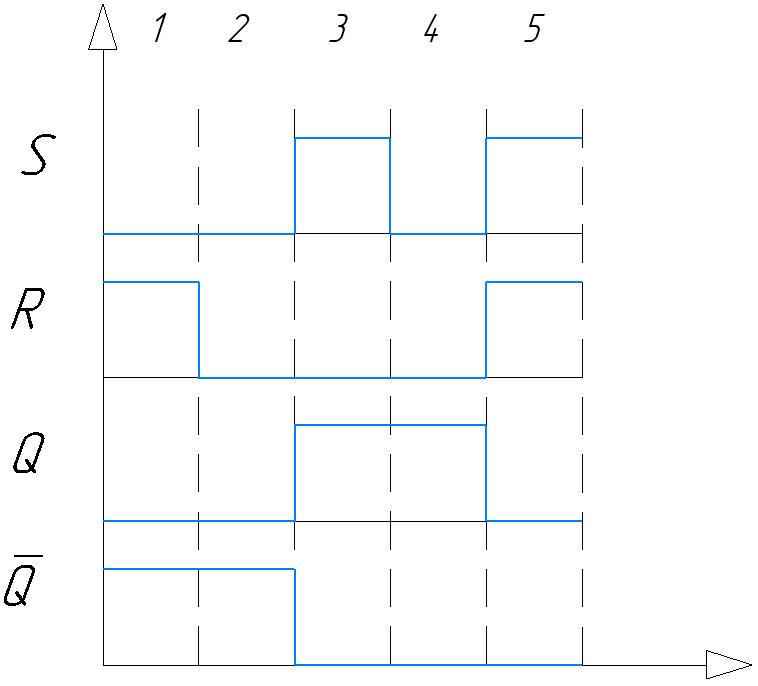

Рисунок 3 - Временная диаграмма RS-триггер на ИЛИ-НЕ

Собираем схему тестирования JK-триггера и убедимся, что он функционируют в соответствии с его назначением.

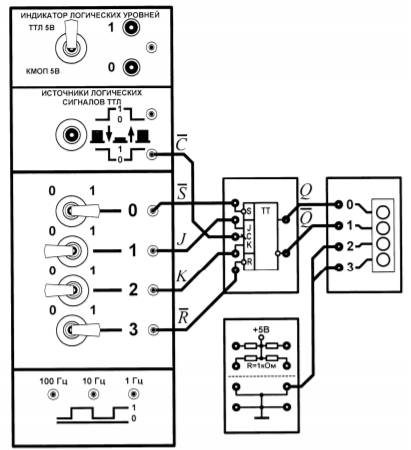

Рисунок 4 – Схема тестирования JK-триггера

Обнуляем триггер. Последовательно подавая на входы J и K триггера различные комбинации сигналов в соответствии с указаниями преподавателя, убедились в соответствии состояния схемы назначению сигналов на ее входах и выходах. Результаты исследований занесём в таблицу.

Таблица 4

JK-триггер |

||||||

|

|

J |

K |

C |

|

|

1 |

0 |

0 |

1 |

Передний фронт |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

|

1 |

0 |

1 |

1 |

0 |

1 |

|

1 |

0 |

0 |

0 |

0 |

1 |

|

0 |

1 |

0 |

1 |

1 |

0 |

|

0 |

1 |

1 |

0 |

1 |

0 |

|

0 |

1 |

1 |

1 |

1 |

0 |

|

0 |

1 |

0 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

0 |

1 |

|

1 |

1 |

0 |

1 |

0 |

1 |

|

1 |

1 |

1 |

0 |

1 |

0 |

|

1 |

1 |

1 |

0 |

1 |

0 |

|

1 |

1 |

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

0 |

|

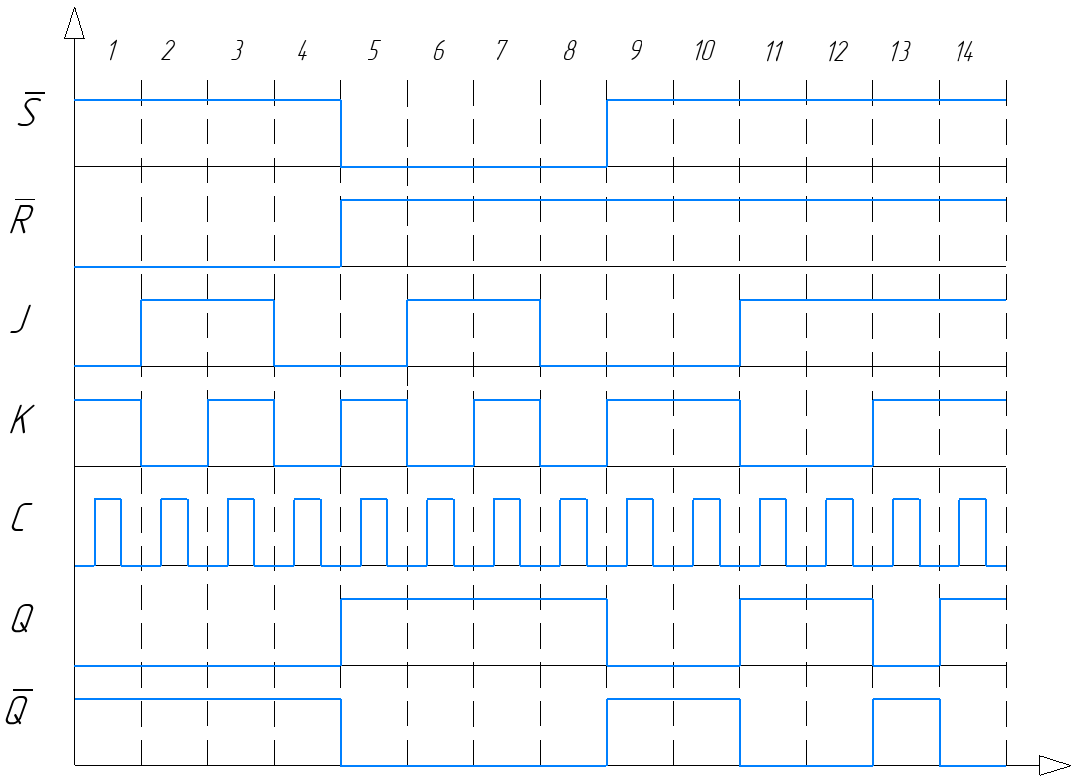

Рисунок 5 - Временная диаграмма JK-триггера

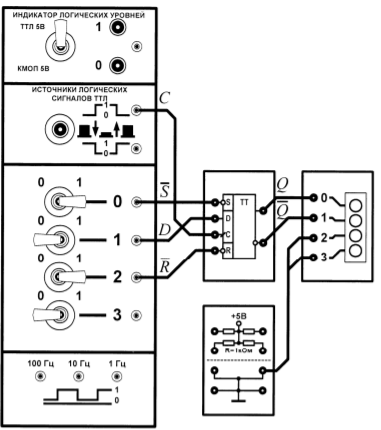

Собираем схему тестирования D-триггера и убедились, что он функционируют в соответствии с его назначением.

Рисунок 6 – Схема тестирования D-триггера

Обнулили триггер. Последовательно подавая на входы R, S, D и C триггера различные комбинации сигналов в соответствии с указанием преподавателя, убедились в соответствии состояния схемы назначению сигналов на ее входах и выходах. Результаты исследований занесём в таблицу.

Таблица 5

D-триггер |

|||||

|

|

D |

C |

|

|

1 |

0 |

0 |

Передний фронт |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

|

0 |

1 |

0 |

0 |

1 |

|

0 |

1 |

1 |

1 |

0 |

|

1 |

1 |

0 |

0 |

1 |

|

1 |

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

1 |

0 |

|

1 |

1 |

1 |

1 |

0 |

|

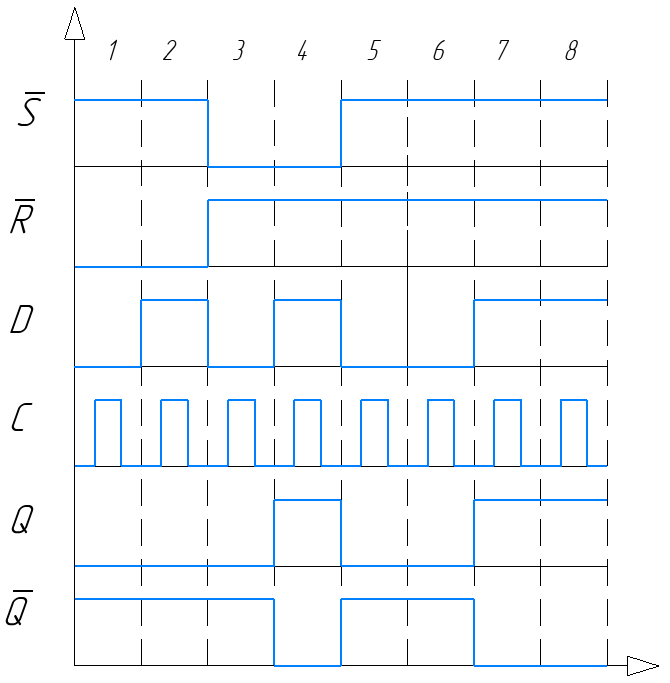

Рисунок 7 – Временная диаграмма D-триггера

Собираем схему тестирования Т-триггера, выполненного на JK- или D-триггерах и убедились, что они функционируют в соответствии с их назначениями.

Нажимая кнопку источника логических сигналов, убедились, что Т-триггер меняет свое состояние с приходом очередного импульса, на счетный вход. Определили экспериментально фронт импульса, по которому происходят переключения в схеме – передний.

Рисунок 8 – Схема тестирования T-триггера, выполненного на D-триггере

Результаты исследования триггера занесём в таблицу.

Таблица 6

T-триггер |

||||

|

|

C |

|

|

1 |

0 |

Передний фронт |

0 |

1 |

1 |

0 |

0 |

1 |

|

0 |

1 |

1 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

0 |

|

1 |

1 |

0 |

1 |

|

Рисунок 9 – Временные диаграммы T-триггера

Вывод: экспериментально исследовали работы триггеров, выполненных на интегральных микросхемах, и закрепили знания по последовательностной цифровой логике. Оформили результаты исследований в таблицы и нарисовали временные диаграммы для различных входов триггеров и инвертированному и не инвертированному выходов.