Лаба 2 / Лабораторная работа 2 Никитина Дарья ПИН 31Д

.docx

Лабораторная работа 2.

микропроцессорные средства и системы

дарья Никитина пин-31Д

Разработка Verilog-описания РАЛУ.

module RALU ( input clk,

input reset,

input [3:0] DataIn,

input [3:0] S,

input M,

input P0,

input A,

input [3:0] v,

input wr,

input [2:0] adr,

output reg OSR,

output reg OSL,

input ISR,

input ISL,

output P4,

output [3:0] R);

reg [3:0] RgA, RgB;

wire [4:1] P;

reg [3:0] BRON [7:0];

always@(posedge clk)

begin

if(reset)

begin

RgA = 0;

RgB = 0;

end

if(v[0]) RgA = A ? DataIn : BRON[adr];

case(v[2:1])

2 'b01:

begin

OSL = RgB[3];

RgB = RgB << 1;

RgB[0] = ISL;

end

2 'b10:

begin

OSR = RgB[0];

RgB = RgB >> 1;

RgB[3] = ISR;

end

2 'b11: RgB = BRON[adr];

endcase

if(wr) BRON[adr] = R;

end

assign P4 = P[4];

ALU_ParallelCarry ALU ( .A(RgA),

.B(RgB),

.S(S),

.M(M),

.P0(P0),

.R(R),

.P(P) );

endmodule

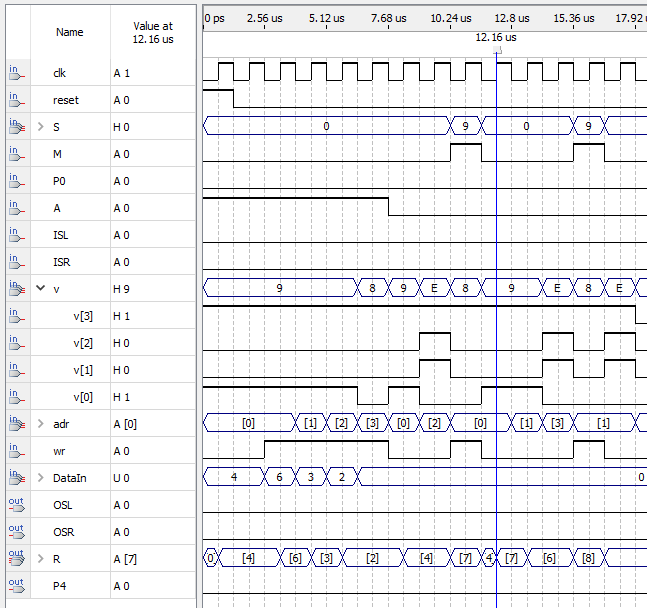

Проверка работы РАЛУ в симуляторе.

Индивидуальное задание (вариант 1)