Sb96713

.pdfМИНОБРНАУКИ РОССИИ

–––––––––––––––––––––––––––––––––––––––––––––––––––

Санкт-Петербургский государственный электротехнический университет «ЛЭТИ» им. В. И. Ульянова (Ленина)

–––––––––––––––––––––––––––––––––––––––––––

О. И. БУРЕНЕВА

ЭЛЕМЕНТЫ СИСТЕМ НА КРИСТАЛЛЕ

Учебно-методическое пособие

Санкт-Петербург Издательство СПбГЭТУ «ЛЭТИ»

2018

УДК 004.3(07) ББК З973.2-018я7

Б90

Буренева О. И.

Б90 Элементы систем на кристалле: учеб.-метод. пособие. СПб.: Изд-во СПбГЭТУ «ЛЭТИ», 2018. 32 с.

ISBN 978-5-7629-2264-7

Содержит описания лабораторных работ по созданию и отладке систем на базе программируемых логических микросхем.

Предназначено для подготовки магистров по направлению «Информатика и вычислительная техника» по программе «Микросистемные компьютерные технологии: системы на кристалле». Может быть использовано и при подготовке специалистов и бакалавров по профилю «Вычислительные машины, комплексы, системы и сети», а также специалистами, разрабатывающими электронную аппаратуру с использованием программируемых логических интегральных схем.

УДК 004.3(07)

ББК З973.2-018я7

Рецензент канд. физ.-мат. наук И. А. Хахаев (ИТМО).

Утверждено редакционно-издательским советом университета

в качестве учебно-методического пособия

ISBN 978-5-7629-2264-7 |

© СПбГЭТУ «ЛЭТИ», 2018 |

2

Введение

Современные программируемые логические интегральные схемы (ПЛИС) являются функционально-сложными элементами и все чаще используются при разработке встроенных систем. Каждое новое поколение FPGA отличается более высокими скоростями работы, большей степенью интеграции, увеличенным объемом памяти и более широкой номенклатурой специализированных элементов [1].

Для выполнения эффективных разработок, разработчику необходимо хорошо знать характеристики доступных блоков, ясно представлять тенденции развития рынка прикладных систем и понимать, как наиболее эффективно использовать возможности FPGA в этих системах.

Цикл включает в себя восемь лабораторных работ. Первые три работы направлены на получение навыков проектирования цифровых устройств различного типа на ПЛИС с последующим анализом характеристик результата с использованием специализированных программных средств среды проектирования Quartus II. Последующие работы ориентированы на освоение способов настройки и особенностей использования специализированных элементов систем на кристалле: распределенной и блочной памяти, процессорного soft-ядра, проектирование цифрового фильтра с использованием средств распределенной арифметики. Одна работа предполагает знакомство с маршрутом проектирования с использованием сторонней САПР, результаты работы которой используются в имплементирующей системе. Восьмая работа посвящена знакомству с JTAG-интерфейсом.

Во всех работах предусмотрено выполнение моделирования разработанных устройств, а также проведение макетных экспериментов, предполагающих использование отладочного набора с установленными ПЛИС компании «Altera», например производимого фирмой «TERASIC» (DE0, DE1, DE0Nano или аналогичные).

3

Лабораторная работа 1 ПРОЕКТИРОВАНИЕ КОМБИНАЦИОННОГО УЗЛА

Цель работы состоит в освоении маршрута проектирования цифровых комбинационных устройств в системе проектирования Quartus II и получении навыков моделирования, анализа результатов проектирования и имплементации проекта в учебную плату.

Краткие теоретические сведения

Под комбинационным узлом (КУ) понимается узел, значения выходных сигналов которого в каждый момент времени полностью определяются значениями сигналов на его входах. Для описания функционирования КУ используются функции алгебры логики, которые могут быть представлены таблицей истинности, аналитическим выражением и другими способами.

Для реализации функции КУ, заданной логическим выражением необходимо выполнить ее декомпозицию на функции имеющегося элементного базиса и прорисовать соответствующую комбинационную схему.

В качестве универсального логического модуля для воспроизведения функций КУ может быть использован мультиплексор. Произвольную функцию от аргументов, поступающих на управляющие входы, можно воспроизвести методом «мультиплексор-константа», подавая на его информационные входы константы 0 и 1. Альтернативой служит метод «мультиплексорфункция», при котором на управляющие входы мультиплексора подается часть входных переменных, а на информационные – остаточные функции, сформированные из оставшихся аргументов.

Третий вариант реализации функций КУ связан с использованием дешифратора: на выходах дешифратора вырабатываются все минтермы, которые можно составить из заданного числа аргументов, а логическая функция в совершенной дизъюнктивной нормальной форме есть дизъюнкция некоторого числа таких минтермов. Для получения функции требуется собрать нужные минтермы по схеме ИЛИ.

Задание на работу

1. Используя последовательность действий, приведенную в приложении, разработать в САПР Quartus II проекты, реализующие функцию следующими способами:

– с использованием элементарного логического базиса;

4

–на основе LPM-модуля мультиплексора (4:1) и логических элементов по схеме «мультиплексор-функция»;

–на основе LPM-модуля дешифратора.

2.Для каждого проекта оценить затраты на реализацию, проанализировать RTL-представление проекта, иерархию использованных примитивов, внутренних регистров и настройки LUT-таблиц, выполнить моделирование проекта.

3.Собрать общий проект, включив в него разработанные преобразователи в качестве отдельных параллельно работающих блоков. Проанализировать RTL-представление проекта, иерархию использованных элементов; определить временные характеристики проекта с использованием анализатора Timing Analyzer.

4.Провести имплементацию проекта в учебную плату: входные сигналы формировать на движковых переключателях, результаты работы наблюдать на светодиодных индикаторах.

Содержание отчета

1.По каждому из трех проектов отчет должен содержать: задание на работу; описание процесса проектирования; исходные файлы (схемные файлы или языковые описания); результаты анализа затрат оборудования, RTLописаний проекта и иерархии использованных элементов; временные диаграммы работы.

2.Для общего проекта верхнего уровня необходимо представить: исходный файл; результаты анализа RTL-представления, иерархию использованных примитивов; результаты моделирования; результаты временного анализа проекта с использованием Timing Analyzer; описание результатов макетирования.

3.Выводы по работе.

Варианты заданий

Вариант |

Функция |

Вариант |

Функция |

|

|

|

|

1 |

0, 2, 3, 4, 7, 9, 13, 15 |

5 |

0, 1, 3, 6, 7, 10, 12, 15 |

2 |

1, 2, 3, 5, 10, 11, 14 |

6 |

1, 2, 4, 6, 8, 10, 12, 14 |

3 |

2, 4, 5, 9, 10, 14, 15 |

7 |

2, 3, 5, 8, 9, 13, 14, 15 |

4 |

3, 4, 5, 7, 8, 10, 13, 14 |

8 |

3, 5, 7, 9, 11, 13, 15 |

5

Лабораторная работа 2 ПРОЕКТИРОВАНИЕ ПОСЛЕДОВАТЕЛЬНОСТНОГО УСТРОЙСТВА

Цель работы состоит в получении навыков проектирования последовательностных устройств и анализа их временных характеристик.

Краткие сведения о проектировании

Последовательностные устройства отличаются от комбинационных цепей наличием элементов памяти, что делает возможным организацию в них обратных связей [2]. Такие устройства (автоматы) за счет элементов памяти (ЭП), имеют некоторое внутреннее состояние Q, определяемое совокупностью состояний всех ЭП. В зависимости от внутреннего состояния, автомат различно реагирует на один и тот же вектор входных сигналов Х, т. е. набор входных сигналов и внутреннее состояние автомата определяют новое состояние Qн = f (Q, X) и вектор выходных переменных Y = f (Q) для автомата Мура и Y = f (Q, X) для автомата Мили, где Q и Qн – состояния автомата до и после подачи входных сигналов.

Переходы автомата из одного состояния в другое начинаются с некоторого исходного состояния Q0, которое также является частью задания автомата. В любой момент времени состояние и выходы автомата зависят от его начального состояния и всех векторов Х, поступавших на автомат ранее. Таким образом, входная последовательность векторов Х преобразуется автоматом в выходную последовательность векторов Y.

Автоматы в каноническом представлении разделяют на две части: память и комбинационные цепи (КЦ). КЦ вырабатывают выходные сигналы и сигналы перевода элементов памяти в новое состояние.

Задание на работу

Спроектировать автомат Мура в соответствии с заданием, используя следующую последовательность действий.

1. Подготовить формализованное задание функционирования автомата с использованием графа переходов. Выполнить кодирование состояний. Определить функции возбуждения элементов памяти, выполнить их минимизацию. Разработать комбинационную схему, обеспечивающую необходимые переходы.

6

2.Подготовить проект схемы автомата в САПР Quartus II, выполнить его моделирование, оценить затраты на реализацию, проанализировать RTLпредставление проекта, иерархию использованных примитивов, внутренних регистров и настройки LUT-таблиц.

3.Для наблюдения смены состояний автомата на светоизлучающих диодах обеспечить в проекте понижение частоты тактового генератора. Провести имплементацию проекта в учебную плату, наблюдать работу схемы.

Варианты заданий

1.4-разрядный счетчик в коде Грея.

2.4-разрядный счетчик в коде Джонсона.

3.4-разрядный счетчик в коде Хемминга 1–4 (контрольные биты комбинационные).

4.4-разрядный суммирующий счетчик по модулю 11.

5.4-разрядный вычитающий счетчик по модулю 9.

Предусмотреть наличие входного сигнала Reset, нулевое значение которого переводит выходные разряды в нулевое состояние, а также выходной сигнал OF, сигнализирующий о переходе в нулевое состояние.

Содержание отчета

Отчет должен содержать: задание на работу; исходные файлы с описанием схемы; временные диаграммы работы, полученные в результате моделирования; RTL-описание проекта, оценки по затратам оборудования; описание результатов макетирования, выводы по работе.

Лабораторная работа 3 КАНАЛЫ ПОСЛЕДОВАТЕЛЬНОЙ ПЕРЕДАЧИ ДАННЫХ

Цель работы: познакомиться с принципами организации последовательного обмена в вычислительных системах.

Краткие сведения

Последовательный способ передачи данных предполагает передачу отдельных битов слова поочередно. Существуют синхронный и асинхронный режимы передачи. При синхронной передаче каждый передаваемый бит сопровождается синхроимпульсом Clk и для связи передатчика и приемника используется минимум три линии: для передачи синхроимпульсов, битов

7

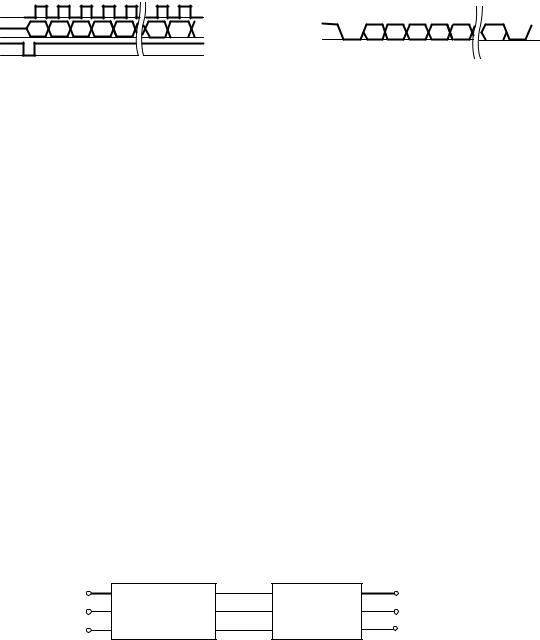

данных и общий проводник. Дополнительно могут использоваться сигналы квитирования. Временная диаграмма работы последовательного синхронного канала приведена на (рис. 3.1, а). Передача данных начинается с пересылки в приемник стартового сигнала FS, получив который, приемник начинает побитовый в соответствии с импульсами Clk прием данных по линии D с их преобразованием в параллельный код.

Clk |

|

|

|

Cтарт- |

Стоп- |

|

|

|

бит |

бит |

|

D |

0 1 2 3 4 |

n-1 |

|

||

D |

0 1 2 3 4 n-1 |

||||

FS |

|

|

|

|

|

|

а |

|

|

|

б |

Рис. 3.1. Формат последовательной передачи данных: а – синхронный режим; б – асинхронный режим

При асинхронной последовательной передаче данных (рис. 3.1, б) передатчик и приемник используют отдельные согласованные генераторы синхроимпульсов. В отсутствие передачи на линии данных сохраняется единичный сигнал. Передатчик инициирует начало передачи нулевым сигналом «старт», его длительность равна длительности информационного бита. После старт-бита следуют информационные биты, за которыми может передаваться бит паритета. Завершается передача данных сигналом «стоп» – переводом линии данных в единичное состояние, обычно на время, равное двум длительностям информационного бита.

Задание на работу

Работа состоит из двух частей. В первой части выполняется проектирование и отладка элементов синхронного, а во второй – асинхронного последовательного интерфейса. Работа выполняется по следующим этапам.

1.Подготовить исходные файлы для реализации синхронных приемника

ипередатчика в соответствии с заданным вариантом.

2.Разработать проект тестирования приемника и передатчика (рис. 3.2).

Clk |

|

Clk |

|

Dout[0..n-1] |

|

|

D |

|

|||

Din[0..n-1] |

Передатчик |

Приемник |

Ready |

||

FS |

|||||

Start |

|

|

Error |

||

|

|

|

Рис. 3.2. Схема тестирования последовательного канала

3.Выполнить моделирование устройств.

4.Выполнить макетирование. Проект должен состоять из приемника и передатчика, не связанных между собой внутри ПЛИС. Данные для передат-

8

чика Din формируются на переключателях, сигнал Start, инициирующий передачу данных, подключить к кнопке. Выходные сигналы передатчика D, FS, Clk выводятся на внешние контакты микросхемы, с подключением к разъему общего назначения. Входные сигналы приемника также через внешние контакты микросхемы, соединяются с контактами разъема общего назначения, а выходные сигналы Data и Ready выводятся на светодиоды. Для визуального наблюдения работы канала приема-передачи в процессе макетирования рекомендуется задать частоту Clk=1Гц и дополнительно на индикацию выводить сигналы, соответствующие значениям принимаемых битов. Для демонстрации совместной работы приемника и передатчика необходимо соединить выходы передатчика и входы приемника на разъеме и в процессе макетирования имитировать разрыв соединения для выявления ошибки передачи.

5.Скорректировать описание приемника и передатчика для реализации асинхронной передачи. Выполнить задания пп. 2–4 для спроектированных асинхронных узлов.

6.Разработать проект тестирования приемника и передатчика, при этом для связи между ними будет использована единственная линия D.

Варианты заданий

Вариант |

Биты: данные/контроль |

Вариант |

Биты: данные/контроль |

|

/стоп-бит(-ы) |

|

/стоп-бит(-ы) |

|

|

|

|

1 |

5/чет./1 |

5 |

5/нечет./2 |

|

|

|

|

2 |

6/чет./1 |

6 |

6/нечет./2 |

|

|

|

|

3 |

7/нечет./2 |

7 |

7/чет./1 |

|

|

|

|

4 |

8/нечет./2 |

8 |

8/чет./1 |

|

|

|

|

Содержание отчета

Отчет по частям 1 и 2 должен содержать следующую информацию: задание на работу; исходные файлы описания приемника и передатчика, а также обобщенную схему тестирования проекта; RTL-описание проекта, оценки по затратам оборудования; результаты моделирования в виде временных диаграмм с комментариями; описание результатов макетирования; выводы по работе.

9

Лабораторная работа 4 ПРИМЕНЕНИЕ ВСТРОЕННЫХ БЛОКОВ ПАМЯТИ

Цель работы состоит в изучении способов настройки и использования блоков встроенной памяти ПЛИС при организации адресного и последовательного доступа.

Краткие теоретические сведения

Память в FPGA представлена двумя ресурсами: блочной (встроенной) и распределенной. Встроенные блоки памяти реализованы в ПЛИС аппаратно, т. е. часть кристалла выделена под организацию памяти и не может быть использована по другому назначению. Количество и емкость таких блоков зависит от конкретной ПЛИС. Распределенная память – это LUT-блоки ячеек ПЛИС, которые также пригодны для хранения данных, информация в этом случае будет «распределена» по площади кристалла. Емкость такой памяти значительно меньше, чем емкость блоков, однако она пригодна для решения определенного класса задач, связанных с буферизацией данных.

Особенность памяти в ПЛИС – это возможность реализации многопортового режима: организация ОЗУ с двумя или более независимыми интерфейсами, обеспечивающими доступ к ячейкам через разделенные шины адреса, данных и управления. Такое решение эффективно в случаях, когда недостаточно одного порта, например при построении буферов FIFO, имеющих раздельные адреса для чтения и записи, при независимости и одновременности этих операций.

В библиотеке параметризированных модулей САПР Quartus II имеются следующие модули ROM/RAM-памяти: lpm_ram_dq – параметризованная RAM с раздельными портами входа-выхода; lpm_ram_dp – параметризованная двухпортовая RAM; alt3pram – параметризованная трехпортовая RAM; lpm_rom – параметризованная ROM; lpm_ram_io – параметризованная RAM с единым портом входа-выхода.

Задание на работу

Работа состоит из двух частей. В первой части предполагается знакомство с блоком памяти, работающим в режиме доступа по адресу. Вторая часть посвящена разработке на базе блочной памяти устройства с последовательным доступом.

10