LS-Sb87081

.pdf

рядные адреса его регистров расположены в адресном пространстве (АП), содержащем 256 адресов. Начальный адрес зоны адресов указан в задании.

Варианты и номера заданий приведены в табл. 4.1.

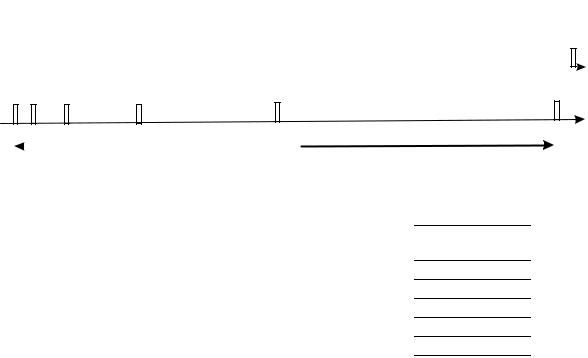

Задание 2. Формирователь импульсной последовательности с ли- нейно-изменяющимися интервалами между импульсами. Разработать узел, формирующий заданную последовательность импульсов. Входные сигналы частоты f = 1/T поступают от ГТИ (генератор разрабатывается). Выход-

ная последовательность периодична с периодом Тр. Узел рассматривается как внешнее устройство процессорной системы. Сигналы пуска и останова поступают из управляющего устройства (процессора), количество периодов работы от пуска до останова фиксируется счетчиком (их максимальное число 100).

ГТИ

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 |

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

|

Выход |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Тp |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 4.1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 4.2 |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Начальный |

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||

|

|

Вариант |

|

|

|

|

|

|

|

Тр |

|

|

|

|

|

|

|

|

|

|

Номера импульсов, |

|

|

|

|

θ |

|||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

проходящих на выход |

|

|

|

|

|

|

адрес |

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

2.1 |

|

|

|

|

|

|

|

|

|

30 |

|

|

|

0, 1, 3, 7, 15, 23, 27, 29, 30 |

|

|

|

|

|

|

|

|

|

30h |

|

|

|

|

|

|

|

4 |

|

|

|

|

|||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

2.2 |

|

|

|

|

|

|

|

|

|

30 |

|

|

|

0, 1, 3, 6, 10, 15, 20, 24, 27, 29, 30 |

|

|

|

|

|

|

40h |

|

|

|

|

|

|

|

8 |

|

|

|

|

||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

2.3 |

|

|

|

|

|

|

|

|

|

31 |

|

|

|

0, 1, 3, 7, 15, 31 |

|

|

|

|

|

|

|

|

|

|

|

|

|

60h |

|

|

|

|

|

|

|

4 |

|

|

|

|

|||||||||||||||||||||||||||||||||

|

|

|

|

|

|

2.4 |

|

|

|

|

|

|

|

|

|

21 |

|

|

|

0, 6, 11, 15, 18, 20, 21, |

|

|

|

|

|

|

|

|

|

|

80h |

|

|

|

|

|

|

|

8 |

|

|

|

|

||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

2.5 |

|

|

|

|

|

|

|

|

|

25 |

|

|

|

0, 1, 3, 7, 12, 18, 25 |

|

|

|

|

|

|

|

|

|

|

|

30h |

|

|

|

|

|

|

|

4 |

|

|

|

|

|||||||||||||||||||||||||||||||||||

Пример временных диаграмм с линейным ростом интервалов между импульсами представлен на рис. 4.1. Варианты заданий приведены в табл. 4.2.

Задание 3. Четырехканальный генератор сигналов с заданными временными диаграммами. Разработать принципиальную электрическую схему генератора, формирующего на выходах 1–4 сигналы, изображенные на временных диаграммах (рис. 4.2). Временные интервалы на диаграммах заданы в микросекундах. Возможные варианты реализации: сочетание двоичного счетчика с ППЗУ, схема на основе распределителя тактов и сборок по ИЛИ; схема с получением искомых импульсов из сигналов счетчика Джонсона, и др. Крите-

рий выбора наилучшего варианта – минимум аппаратных затрат.

21

Вариант 3.1

1

0.1

0.1

Выход 1 |

0.3 |

0.15 |

|

Выход 2

0.2 0.6

Выход 3

3

Выход 4

Вариант 3.2

Выход 1 Выход 2

Выход 3

Выход 4

Вариант 3.3

0.30.35

1

0.25

0.10.35

0.3 |

0.15 |

0.20.6

1

0.2

Выход 1 Выход 2 Выход 3 Выход 4

Вариант 3.4

Выход 1 Выход 2 Выход 3

3

Выход 4

0.4 0.15

0.2 0.6

0.3 0.35

1

0.8

0.1

0.4

0.4

Рис. 4.2

Задание 4. Реверсивный распределитель тактовых сигналов с пере-

менным числом каналов. Разработать распределитель тактов, формирующий на выходах заданные последовательности импульсов. Входные сигналы частоты f = 1/T распределитель получает от ГТИ (генератор разрабатывается).

22

ГТИ 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19

t

Выход 1 |

|

|

t |

Выход 2 |

|

|

|

|

|

|

|

Выход 3 |

|

|

t |

Выход 4 |

|

|

|

|

|

|

|

Выход 5 |

|

|

t |

Выход 6 |

|

|

|

|

|

t |

|

Выход 7 |

|

|

|

|

|

t |

|

|

|

|

|

|

|

Тp |

|

|

|

|

|

|

Рис. 4.3 |

||

Выходная последовательность периодична с периодом Тр. Скважность импульсов равна четырем. Сигналы пуска и останова распределителя поступают из управляющего устройства (процессора), количество периодов работы распределителя от пуска до останова фиксируется (их максимальное число 64). Распределитель рассматривается как ВУ процессорной системы, его адреса расположены в третьей четверти АП емкостью 256 адресов.

|

|

|

|

|

|

|

|

|

|

Таблица 4.3 |

||

Вари- |

Тр |

|

Номера импульсов, проходящих на выходы распределителя |

|

||||||||

ант |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

||

4.1 |

19 |

1, 13 |

2, 12, |

3, 11, |

4, 10, |

5, 9 |

6, 8 |

7 |

– |

– |

– |

|

14, 18 |

15, 17 |

16 |

||||||||||

|

|

|

|

|

|

|

|

|

||||

4.2 |

19 |

1, 9, |

2, 8, |

3, 7, |

|

|

|

|

|

|

|

|

10, 12, |

11, 15, |

4, 6, 16 |

5 |

– |

– |

– |

– |

– |

||||

13, 19 |

||||||||||||

|

|

14, 18 |

17 |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|||

4.3 |

24 |

1, 19 |

2, 18, |

3, 17, |

4, 16, |

5, 15 |

6, 14 |

7, 13 |

8, 12 |

9, 11 |

10 |

|

20, 24 |

21, 23 |

22 |

||||||||||

|

|

|

|

|

|

|

|

|

||||

4.4 |

24 |

1, 19 |

2, 18, |

3, 17, |

4, 16, |

5, 15 |

6, 14 |

7, 13 |

8, 12 |

9, 11 |

10 |

|

20, 24 |

21, 23 |

22 |

||||||||||

|

|

|

|

|

|

|

|

|

||||

Возможные варианты реализации: на основе двоичного счетчика с дешифратором и сборками по ИЛИ, на основе реверсивного регистра, на основе сочетания двоичного счетчика и программируемой памяти, сочетания счетчика и ПМЛ, и др.

Пример временных диаграмм сигналов представлен на рис. 4.3. Варианты заданий приведены в табл. 4.3.

23

Задание 5. Программируемый преобразователь кода в ШИМ-сиг-

нал. Разработать принципиальную электрическую схему преобразования параллельного входного кода N в широтно-модулированный импульсный сиг-

нал (рис. 4.4) с длительностью tи и периодом Тц, где tи = NТц/Nmax, Тц = = (Nmax + 1)kT (Т – период тактового генератора (генератор разрабатывается), а коэффициент k = 1, 4, 8 задается управляющим кодом).

|

tи |

tи |

|

|

|

Таблица 4.4 |

U |

|

|

Разрядность |

Начало |

||

|

|

|

Вариант |

|||

|

|

|

|

входного |

области |

|

|

|

|

|

|

кода |

адресов |

|

kT(Nmax + 1) kT(Nmax + 1) |

t |

5.1 |

8 |

45h |

|

|

5.2 |

10 |

75h |

|||

|

|

|

|

5.3 |

12 |

85h |

|

|

Рис. 4.4 |

|

5.4 |

16 |

C5h |

|

|

|

5.5 |

20 |

35h |

|

|

|

|

|

|||

Входной код, управляющий код и сигналы пуска/останова преобразователя поступают из управляющего устройства (процессора). Преобразователь рассматривается как ВУ процессорной системы, имеющее адрес в заданной части АП емкостью 256 адресов. Варианты задания приведены в табл. 4.4.

Задание 6. Счетчик с программированием приращений содержи-

мого. Счетчик имеет 10 разрядов и является двоично-кодированным. Содержимое счетчика изменяется на ∆N с приходом каждого входного импульса.

Возможны два режима работы счетчика: с ∆N1 и ∆N2. Код режима, сигналы сброса, пуска и останова счетчика поступают от управляющего устройства (процессора). Код, полученный в счетчике к моменту останова, фиксируется. Счетчик рассматривается как внешнее устройство процессорной системы, его адреса расположены в заданной области адресного пространства системы, имеющего емкость 256 адресов.

|

|

|

|

|

Таблица 4.5 |

|

|

|

|

|

|

|

|

Вариант |

∆N |

∆N |

Тип |

Тип |

Область |

|

логического |

|

|||||

|

1 |

2 |

триггера |

элемента |

АП |

|

6.1 |

+3 |

+5 |

JK |

И-НЕ |

40h |

|

6.2 |

–3 |

–5 |

D |

И-НЕ |

80h |

|

6.3 |

+7 |

+9 |

JK |

ИЛИ-НЕ |

C0h |

|

6.4 |

–7 |

–9 |

D |

ИЛИ-НЕ |

36h |

|

6.5 |

+15 |

+17 |

JK |

И-НЕ |

85h |

|

6.6 |

–15 |

–17 |

D |

И-НЕ |

20h |

|

|

|

|

24 |

|

|

|

Возможны следующие варианты реализации: формальный синтез (с использованием триггеров и логических элементов заданного типа), схема с применением комбинационного сумматора и регистра в младших разрядах,

вариант с изменением содержимого счетчика на 0.5(∆N1 + ∆N2) и последующим прибавлением или вычитанием единицы, схема с двоичным счетчиком и ППЗУ и др. Варианты задания приведены в табл. 4.5.

Задание 7. Преобразователь параллельного кода в последовательный для асинхронного протокола передач. Разработать узел, преобразую-

щий параллельный код в последовательный с добавлением к нему старт-бита, стоп-бита и бита паритета.

|

|

|

Таблица 4.6 |

|

|

|

|

Вариант |

Разрядность |

Скорости передачи |

Область АП |

входного кода, бит |

данных, Кбит/с |

||

7.1 |

8 |

2.4; 4.8; 9.6 |

40h |

7.2 |

16 |

4.8; 9.6; 19.2 |

80h |

7.3 |

12 |

1.2; 2.4; 4.8 |

85h |

7.4 |

8 |

9.6; 19.2; 38.4 |

60h |

Предусмотреть передачи последовательного кода со скоростями, указанными в задании. Входной параллельный код, код выбора скорости передачи и сигнал пуска передаются из процессора. Критерий выбора варианта – минимум аппаратных затрат. Варианты задания приведены в табл. 4.6.

25

Список литературы

1.Угрюмов Е. П. Цифровая схемотехника: учеб. пособие для вузов. СПб.: БХВ-Петербург, 2-е изд. 2006; 3-е изд. 2010.

2.Системы автоматизированного проектирования фирмы Altera MAX+ plus II и Quartus II. Краткое описание и самоучитель/Д. А. Комолов, Р. А. Мяльк, А. А. Зобенко, А. С. Филиппов. М.: ИП РадиоСофт, 2002.

3.Артамонов А. Б., Смирнов А. М. Интерфейсные БИС микропроцессорных комплектов: учеб. пособие/ЛЭТИ. Л., 1990.

4.www.altera.com/literature/catalogs/lpm.pdf (Справочник по элементам

LPM).

5.Логические ИС КP1533, КР1554: справочник: в 2 ч. / И. И. Петровский, А. В. Прибыльский, А. А. Троян, В. С. Чувелев. М.: БИНОМ, 1993.

26

ПРИЛОЖЕНИЕ

Рассмотрим кратко пример выполнения некоторых разделов проекта. Пусть требуется разработать формирователь импульсов с тремя выходами, на которых воспроизводятся функции времени Z1, Z2 и Z3, показанные на рис. П.1.

T

T/8

Z1

T/4

Z2

3T/8

Z3

Рис. П.1

Режим работы формирователя старт-стопный (после каждого сигнала пуска формирователь генерирует циклы работы вплоть до сигнала останова).

Поставленная задача может быть решена многими методами. Остановимся лишь на одной группе методов, в рамках которых для формирования требуемых импульсов нужно оперировать интервалами, соответствующими наибольшему общему делителю искомых интервалов (в данном случае – это интервал Т/8). Из этих «квантов» можно собирать нужные выходные сигналы, объединяя их по ИЛИ.

Можно разбить период Т на восемь частей (генератор плюс трехразрядный счетчик плюс дешифратор) и собирать импульсы из этих частей схемой ИЛИ. Такое решение будет простым, но так как выходные импульсы будут составляться из нескольких коротких, на стыках последних могут возникать опасные помехи (просечки). Если для сборки выходных сигналов использовать более длительные интервалы, то решение окажется более удачным – получим исключение просечек. Более длительные интервалы можно получить на выходах Q1–Q4 четырехразрядного счетчика Джонсона (рис. П.2). Сдвиги между импульсами на соседних выходах составляют 1/8 периода, что и позволит составить нужные выходные функции Z1, Z2 и Z3.

Естественно, что для компоновки искомых функций, нужно выбирать диаграммы, фронты которых совпадают с фронтами импульсов Z1, Z2 и Z3.

Нетрудно видеть, что Z1 = Q1Q3, Z2 = Q1Q2 и Z3 = Q2 Q3.

27

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

Q1

Q2

Q3

Q4

Рис. П.2

Блок-схема реализации функций и управления этим процессом от команд программы приведена на рис. П.3. Формирователю присвоен адрес 129 из адресного пространства внешних устройств емкостью 256 адресов. Появление этого адреса открывает путь для прохождения в соответствующие точ-

ки схемы импульсов IOW и IOR , так что приведение схемы в исходное состояние (сброс) и ее пуск осуществляются командами OUT port и IN port соответственно. Таким образом, для управления формирователем, рассматриваемым как внешнее устройство микропроцессорной системы, принята типовая схема – адресный дешифратор плюс логика передачи управляющих сигналов в требуемые точки схемы.

В принципиальной электрической схеме формирователя (рис. П.4), построенной средствами графического ввода пакета Quartus II, использована

А7 А6 А5 А4 А3 А2 А1 А0 |

Селектор адреса |

|

|

|

|

|

Z1 |

||

|

|

|

|

|

|

|

|

|

|

1 |

|

1 |

1000 0001b = |

|

|

|

|

|

Z2 |

|

|

|

= 81h = 129D |

|

|

|

|

1 |

Z3 |

|

|

1 |

Генератор |

Q1 |

Q2 |

Q3 |

Q4 |

||

|

|

|

|

||||||

|

|

|

G |

clk |

Счетчик Джонсона |

Логика |

|||

SEL |

|

Старт/Стоп |

aset |

|

|

|

формирования |

||

|

"1" |

|

|

|

|

|

|||

|

|

|

|

|

|

|

выходных |

||

|

1 |

D |

|

|

|

|

|

функций |

|

IOR |

|

|

OUT port |

;сброс/останов |

|||||

|

|

|

|

|

IN port |

;пуск |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

OUT port |

;сброс/останов |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IOW |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IN port |

;пуск |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

Рис. П.3

28

Рис. П.4

29

библиотека примитивов. Генератор выполнен по кольцевой схеме [1] с цепью задержки из двух инверторов в обратной связи элемента И-НЕ. При переходе управляющего напряжения на высокий уровень начинается генерация, причем первый же импульс (нулевого уровня) имеет стандартную длительность. Поскольку при компиляции схемы САПР может выбросить цепочку из двух последовательно включенных инверторов, эта возможность предотвращена включением виртуальных элементов LCell.

Компиляция проекта, реализованного в микросхеме EPM3032ALC44-4 семейства MAX 3000A, дала следующие результаты: число затраченных макроячеек 10 из общего числа 32 (31 %), число использованных контактов 17 из общего числа 34 (50 %).

Рис. П.5

При моделировании работы формирователя с учетом временных задержек, свойственных примененной микросхеме, получены временные диаграммы (рис. П.5). Как видно, требуемое функционирование схемы достигнуто. Пока адрес отличается от 10000001, формирователь не реагирует на старт-стопные воздействия. При появлении адреса 10000001 устройство запускается командой IOR и останавливается командой IOW . На участках работы формируются импульсы Z1, Z2 и Z3 заданной формы. Частота работы генератора около 50 МГц.

30