LS-Sb87104

.pdf

3.4. Синтез счетчика по mod М1i

Счетчик по mod M1i имеется как в канале зондирующего сигнала G, так и в канале отраженного (подвижного) сигнала Gv. Эти счетчики используют-

ся в качестве делителей частоты на число Mi = Tif0/M0 при i = 1, 2, 3, 4 (рис. 2.1) и могут быть выполнены на 16-разрядном двоичном счетчике с параллельной синхронной загрузкой данных (расчетные значения Mi, как правило, представимы 16-разрядным двоичным кодом).

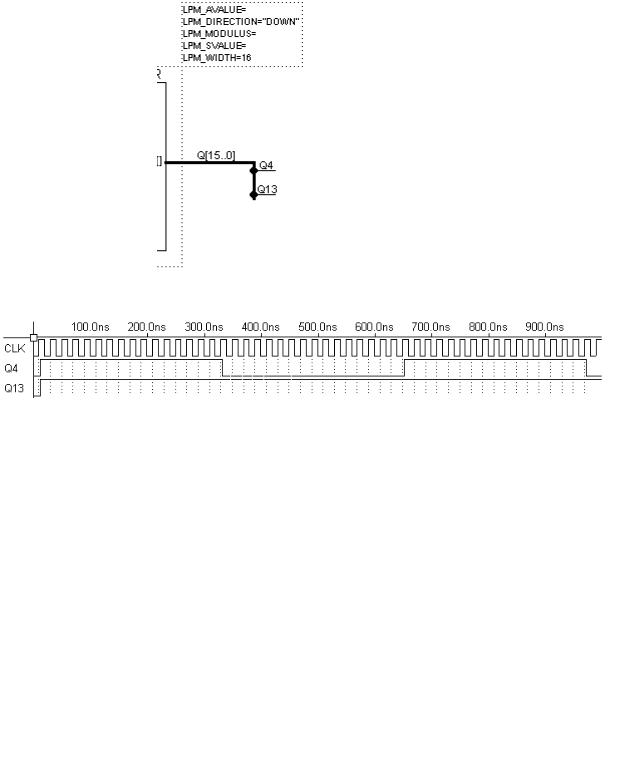

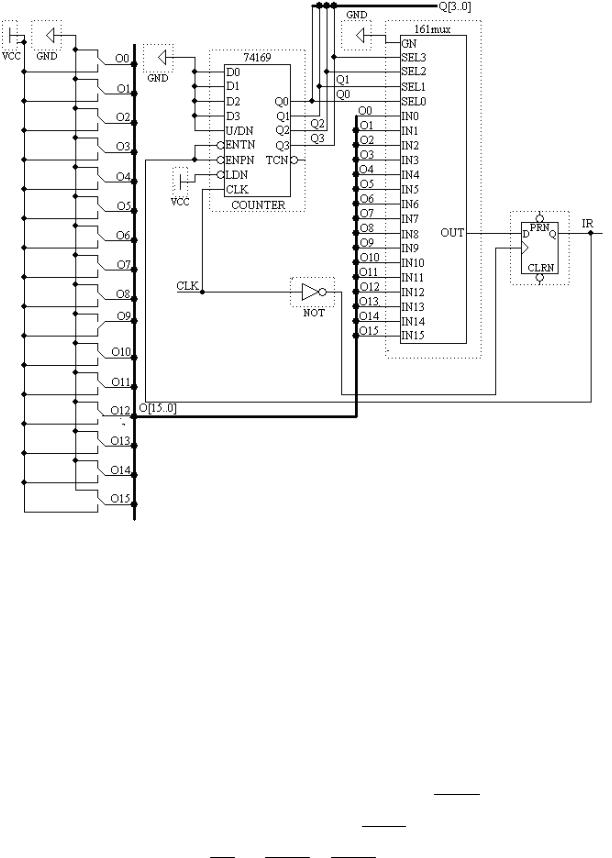

Счетчик по mod M1i на МЭ lpm counter. Для построения делителя на МЭ фирмы Altera используются счетчики из папки lpm: 16-разрядный счетчик lpm_counter с синхронной загрузкой данных (в счетчике задаются входные сигналы cin, clk_en, cnt_en, sload, разрядность width = 16 и направление работы (режим вычитания) lpm direction = down, а также выходной сигнал переноса cout. На рис. 3.12 показана схема 16-разрядного счетчика. Модуль

пересчета Mi этого счетчика определяется соотношением Mi = dM i + 1, т. е.

он задается параллельной записью в счетчик числа dM i = Mi – 1. Число dM i –

двухбайтовое, содержащее мдадший байт dLT и старший байт dMT (M – most, L – least), хранящиеся в памяти в соседних ячейках. Оба байта должны быть записаны в регистры памяти 74377b. По команде OUT port_dLT вырабатывается системный сигнал управления I / OW = 0, а дешифратор адресных сигналов внешних устройств вырабатывает сигнал port_dLT = 0, который разрешает запись младшего байта D[7..0] в регистр; запись производится положтиельным перепадом сигнала I / OW . Аналогичным образом по команде OUT port_dMT записывается старший байт данных D[15..0] в регистр 74377b.

Временные диаграммы работы счетчика представлены на рис. 3.13. После загрузки младшего байта D[7..0] = 05 и старшего байта D[15..0] = 00, которая разрешается сигналом COUT = 1, возникающем в нулевом состоянии счетчика, счетчик начинает считать до нуля, после чего снова произойдет загрузка. На рис. 3.13 запись младшего и старшего байта осуществляется одновременно, реально же запись младшего и старшего байта происходит в разные моменты времени.

- 21 -

Рис. 3.12. Схема 16-разрядного делителя на M1i

Рис. 3.13. Временные диаграммы 16-разрядного делителя

Схема 16-разрядного делителя частоты используется как в неподвижном канале (на тактовый вход подается сигнал с выхода делителя на M0 P40), так и в подвижном канале (на тактовый вход подается сигнал с выхода делителя на Mv P4v). Выходные сигналы счетчиков COUT являются сигналами G и Gv.

3.5. Синтез счетчика по mod Мj

Требуемые коэффициенты Mj реализуются последовательным включе-

нием делителя на постоянный коэффициент Mk и управляемого 2-байтовыми данными 16-разрядного счетчика.

- 22 -

Рис. 3.14. Делитель на Mk = 25 и Mkeyb = 214.

Рис. 3.15. Временные диаграммы работы делителя на Mk = 25 и Mkeyb = 214

Рис. 3.16. Схема 16-разрядного делителя на M1j

Счетчик по mod Mk на МЭ lpm counter. Макроэлемент счетчика используется в режиме делителя на 2k; для Mk = 32 = 25 выходной сигнал снима-

ется с выхода Q4 (схема представлена на рис. 3.14, а временные диаграммы – на

- 23 -

рис. 3.15). Эта же схема формирует сигнал частоты 500 Гц для опроса

шифратора клавиатуры, при этом коэффициент деления M |

keyb |

= 107/500 = |

|||

|

|

|

|

|

|

= 20 000. Легко задать |

M |

= 214 = 16 |

384, если использовать 16-разрядный |

||

|

keyb |

|

|

|

|

счетчик с выходом |

Q13, |

при этом |

частота выходного |

сигнала fkeyb = |

|

= 107 16 384 ≈ 610 Гц. |

|

|

|

|

|

Делитель на M1j строится по такому же принципу, что и делитель на M1i (16-разрядный счетчик с записью двухбайтовых чисел). На вход делителя поступает сигнал частоты f0/M0 = 10 МГц, выходной сигнал делителя – x1. Схема делителя на M1j показана на рис. 3.16.

3.6. Контроллер клавиатуры

Для управления имитатором используются 16 клавиш, каждой из которых приписан свой 4-разрядный двоичный код. При нажатии любой клавиши контроллер клавиатуры должен выдавать двоичный код этой клавиши и флаг клавиатуры, указывающий факт нажатия любой клавиши (сигнал квитирования), или сигнал запроса прерывания IR (interrupt request).

Шифратор клавиатуры. На рис. 3.17 изображена схема шифратора клавиатуры, содержащая счетчик по mod 16 (74169) и мультиплексор 16 1 (161mux). При замыкании клавиши k = 0, 1, , 15 выходной сигнал DO мультиплексора примет значение 1 в момент времени, когда счетчик установится в состояние k, что приведет к появлению значения сигнала IR = 1 и блокировке счета. Пока клавиша нажата, счетчик выдает число k = = DO3DO2DO1DO0, а D-триггер – сигнал IR = 1. При отпускании клавиши сигнал IR установится в 0 и счетчик продолжит счет. Чем ниже частота задающего генератора, тем надежнее исключается «дребезг» контактов клавиш. На частоте генератора 500 Гц «дребезг» надежно устраняется. На рис. 3.18 – временные диаграммы для случая, когда нажата клавиша с номером 9.

Интерфейсные схемы шифратора клавиатуры подключают к системной шине данных 4-разрядный код нажатой клавиши помощью буфера данных, показанного на рис. 3.19, в. Перепадом сигнала IR с 0 на 1 D-триггер

- 24 -

Рис. 3.17. Схема шифратора клавиатуры

Рис. 3.18. Временные диаграммы работы шифратора клавиатуры

устанавливается в состояние 1 (рис. 3.19, б). С выхода триггера флаг клавиатуры FKB = DO4 = 1 подается на буфер данных 74244b вместе с 4-разрядным кодом клавиатуры DO3DO2DO1DO0. При выполнении команды IN CSKB с дешифратора адреса поступает значение сигнала CSKB = 0 (chip select keyboard), а с шины управления – значение I / OR = 0, что приводит к появлению значения сигнала OE = I / OR CSKB = 0, разрешающего передачу по шине данных 5-разрядного кода в аккумулятор CPU.

- 25 -

а |

б |

в |

г |

Рис. 3.19. Интерфейсные схемы клавиатуры: а – формирователь X2; б – флаг клавиатуры; в – формирователь шины данных для ввода; г – расположение клавиш

Анализ назначения нажатой клавиши. Функциональное назначение клавиш показано на рис. 3.19, г: клавиши k = 0, 1, , 7 задают скорость движения цели vj (j = k), k = 8 и 9 – направление движения цели (клавиши 10 и 11

не используются), k = 12, 13, 14, 15 – период Ti сигнала G (i = 1, 2, 3, 4). Коды этих трех групп клавиш различаются значением двух старших

разрядов DO3DO2: 10 – направление движения; 00 и 01 – значение скорости vj; 11 – значение периода Ti. Для принятия решения маской 00001100 выделяются разряды DO3DO2 и содержимое аккумулятора сравнивается с числом 8: содержимое равно 8, если нажатая клавиша имеет коды 10 (клавиши направления движения); содержимое больше 8, если нажатая клавиша имеет коды 11 (клавиши значений периода Ti); содержимое меньше 8, если нажа-

тая клавиша имеет коды 0 (клавиши значений скорости vj). Программа обслуживания клавиатуры при использовании МЭ (два 16-разрядных счетчика для задания периода и один 16-разрядный счетчик для задания скорости

движения vj и программного ввода данных с квитированием имеет вид (зада-

ны адреса клавиатуры – 28h, триггера направления – 68h).

- 26 -

L1: |

IN |

port_KB |

; А = DO DO DO DO DO |

0 |

|||||

|

MOV |

C,A |

|

|

4 |

3 |

2 |

1 |

|

|

; запоминание кода в регистре C |

||||||||

|

ANI |

10h |

; A = 0 0 0 D4 0 0 0 0 (квитирование) |

||||||

|

JZ |

L1 |

; если D4 = IR = 0, повторный ввод |

||||||

|

OUT |

port_KB |

; сброс флага клавиатуры DO4 (см. рис. 3.19, б) |

||||||

|

MVI |

A,0Fh |

; A = 0 0 0 0 1 1 1 1 |

|

|

|

|||

|

ANA |

C |

; 0 0 0 D3D2D1D0 – код нажатой клавиши |

||||||

|

MOV |

C,A |

; запоминание в регистре C кода нажатой клавиши |

||||||

|

ANI |

0Ch |

; A = 0 0 0 0 D3D2 0 0 |

|

|

|

|||

|

CPI |

8 |

; сравнение старших разрядов кода с числом 8 |

||||||

|

JZ |

L2 |

; переход к заданию направления движения |

||||||

|

JC |

L3 |

; переход к заданию скорости движения |

||||||

|

CALL |

TAB |

; подпрограмма чтения таблицы данных |

||||||

|

OUT |

port_dLT |

; запись d |

ML |

в регистр младшего байта счетчика M |

||||

|

INX |

H |

|

|

|

|

|

1i |

|

|

; адрес старшего байта dMM данных |

||||||||

|

MOV |

A,M |

; пересылка dMM в аккумулятор |

||||||

|

OUT |

port_dMT |

; запись d |

MM |

в регистр старшего байта счетчика M |

||||

|

JMP |

L1 |

|

|

|

|

|

1i |

|

L2: |

; переход на ввод кода клавиши |

||||||||

MOV |

A,C |

; A = 0 0 0 0 D3D2D1D0 – код нажатой клавиши |

|||||||

|

OUT |

port_X2 |

; запись D0 = DAL0 в триггер знака (см. рис. 3.19, а) |

||||||

L3: |

JMP |

L1 |

|

|

|

|

|

|

|

CALL |

TAB |

; подпрограмма чтения таблицы данных |

|||||||

|

OUT |

port_dLV |

; запись d |

ML |

в регистр младшего байта счетчика M |

||||

|

INX |

H |

|

|

|

|

|

1j |

|

|

|

|

|

|

|

|

|

||

|

MOV |

A,M |

; A = dMM |

|

|

|

|

|

|

|

OUT |

port_dMV |

; запись d |

MM |

в регистр старшего байта счетчика M |

||||

|

JMP |

L1 |

|

|

|

|

|

1j |

|

|

|

|

|

|

|

|

|

||

TAB: LXI |

H,700h |

; rp H = 0700h |

|

|

|

|

|||

|

MOV |

A,C |

; A = 0 0 0 0 D3D2D1D0 – код нажатой клавиши |

||||||

|

ADD |

A |

; A = A + A = 2C |

|

|

|

|

||

|

MOV |

C,A |

; формирование в rp B числа, равного |

||||||

|

MVI |

B,0 |

; удвоенному коду клавиши |

|

|||||

|

DAD |

B |

; HL = HL + BC = 0700h + 2C – адрес памяти |

||||||

|

MOV |

A,M |

; A = dML – младший байт данных |

||||||

|

RET |

|

|

|

|

|

|

|

|

Для таблицы данных отведена область ПЗУ, начинается с адреса 0700h. Для хранения двухбайтовых чисел используются две соседние ячейки памяти

- 27 -

с адресами A и A + 1. Подпрограмма TAB определяет адрес младшего байта данных и читает его из ПЗУ. Для определения адреса A по коду нажатой клавиши к начальному адресу 0700h прибавляется удвоенный код клавиши. Таким образом, по коду клавиши, например, с номером k = 2, задающей в соот-

ветствии с рис. 3.19, г скорость v2, определяются адреса двух ячеек памяти 0704h и 0705h, где хранятся соответственно младший и старший байты числа dM2 . При выполнении команды OUT port_KB на ЛЭ ИЛИ (см. рис. 3.19, б)

поступают сигналы portKB = 0 и I / OW = 0, на выходе ЛЭ вырабатывается сигнал R = 0, устанавливающий триггер флага клавиатуры в состояние Q = 0, что приводит к сбросу флага клавиатуры (сигнал DO4 = 0). При выполнении команды OUT CSX2 по сигналам portX 2 =0 и I / OW = 0 вырабатывается сигнал = 0 (см. рис. 3.19, а), перепадом с 0 на 1 которого в триггер знака x2

записывается значение разряда BD0 = DO0.

Если ввод данных с клавиатуры производится по прерыванию (сигнал IR подается на вход RST7.5), тогда программа обработки прерываний должна начаться с запоминания содержимого регистровых пар, аккумулятора и регистра признаков. Затем следует ввод данных и их анализ.

PUSH |

H |

PUSH |

B |

PUSH |

PSW |

IN |

CSKB |

MOV |

C,A |

MVI |

A,0Fh |

ANA |

C |

MOV |

C,A |

ANI |

0Ch |

CPI |

8 |

JZ |

L2 |

JC |

L3 |

CALL |

TAB |

OUT |

port_dLT |

INX |

H |

MOV |

A,M |

OUT |

port_dMT |

JMP |

L1 |

;А = DO4DO3DO2DO1DO0

;запоминание кода в регистре C

;A = 0 0 0 0 1 1 1 1

;0 0 0 D3D2D1D0 – код нажатой клавиши

;запоминание в регистре C кода нажатой клавиши

;A = 0 0 0 0 D3D2 0 0

;сравнение старших разрядов кода с числом 8

;переход к заданию направления движения

;переход к заданию скорости движения

;подпрограмма чтения таблицы данных

;записьdML врегистрмладшегобайта(см. рис. 3.12)

;адрес старшего байта dMM данных

;пересылка dMM в аккумулятор

;записьdMM врегистрстаршегобайта(см. рис. 3.12)

- 28 -

L2: |

MOV |

A,C |

|

OUT |

port_X2 |

|

JMP |

L1 |

L3: |

CALL |

TAB |

|

OUT |

port_dLV |

|

INX |

H |

|

MOV |

A,M |

|

OUT |

port_dMV |

|

JMP |

L1 |

TAB: LXI |

H,700h |

|

|

MOV |

A,C |

|

ADD |

A |

|

MOV |

C,A |

|

MVI |

B,0 |

|

DAD |

B |

|

MOV |

A,M |

|

RET |

|

L1: |

POP |

PSW |

|

POP |

B |

|

POP |

H |

|

EI |

|

RET

;A = 0 00 0 D3D2D1D0 – код нажатой клавиши

;записьD0 = DAL0 втриггерзнака(см. рис. 3.19, а)

;подпрограмма чтения таблицы данных

;запись dML в регистр младшего байта счетчика

;M1j, рис. 3.16

;A = dMM

;запись dMM в регистр старшего байта счетчика

;M1j, рис. 3.16

;rp H = 0700h

;A = 0 0 0 0 D3D2D1D0 – код нажатой клавиши

;A = A + A = 2C

;формирование в rp B числа, равного

;удвоенному коду клавиши

;HL = HL + BC = 0700h + 2C – адрес памяти

;A = dML – младший байт данных

;разрешение всех прерываний (после следующей

;команды)

;возврат из подпрограммы обработки прерываний

;RST 7.5

3.7.Приемопередатчик, обслуживающий внешние устройства схемы

Через этот приемопередатчик осуществляется связь системной шины данных с внешними устройствами. На рис. 3.20 представлена схема приемопередатчика, в котором шина DB[7..0] подключена к локальной шине DAL[7..0], а шина DA[7..0] – к системной шине DBS[7..0]. При T = 1 обеспечивается передача от шины DA приемопередатчика к шине DB. Сигнал T =

= RD , поэтому при выполнении команды IN port сигнал RD = 0 и приемопередатчик передает данные от внешнего устройства через локальную шину DB к системной шине DA, а далее от системной шины процессора через приемопередатчик процессора к локальной шине и в процессор. При выполнении

- 29 -

Рис. 3.20. Приемопередатчик внешних устройств

команды OUT port сигнал RD = 1, происходит передача данных от DA к DB в приемопередатчике процессора, т. е. на системную шину данных, а затем от DA к DB в приемопередатчике внешних устройств, т. е. от системной шины данных к локальной и далее во внешнее устройство.

3.8. Дешифратор адресов

При работе имитатора CPU обращается к следующим устройствам: две схемы памяти (ПЗУ и ОЗУ):

○ ПЗУ 573РФ2 объемом 2K 8 бит (для хранения программного обес-

|

печения и таблицы данных); |

|

○ ОЗУ 537РУ10 объемом 2K 8 бит (для |

|

стека и хранения данных). |

|

Поэтому необходимо использовать два |

|

дешифратора адресов – адресов схем памяти и |

|

адресов внешних устройств. Дешифратор адре- |

|

сов схем памяти выполнен на МЭ 74138 |

Рис. 3.21. Дешифратор адресов |

(рис. 3.21). Назначение выходных сигналов де- |

схем памяти |

шифратора, значения начальных ABEG и конеч- |

ных AEND адресов представлены в табл. 3.12. При построении схемы на макроэлементах, в состав которой входят два

16-разрядных счетчика, число внешних устройств увеличивается до восьми:

○регистр младшего байта данных в делителе на M1i

-30 -