- •Введение

- •1 Тема 7. Подсистема управления вводом-выводом

- •1.1 Язык С как стандарт взаимодействия с ОС

- •1.2 Системные операции для работы с файловой системой

- •1.2.1 Системные вызовы open() и close()

- •1.2.2 Системные вызовы read() и write()

- •1.2.3 Системный вызов lseek()

- •1.3 Создание специальных файлов

- •1.4 Запрос информации о статусе файлов

- •1.5 Каналы

- •1.5.1 Полудуплексные каналы UNIX

- •1.5.2 Именованные каналы FIFO

- •1.6 Дублирование дескрипторов файлов

- •1.7 Монтирование и демонтирование ФС

- •1.8 Ссылки на имена файлов

- •1.9 Лабораторная работа по теме №7

- •1.9.1 Интегрированная среда разработки Eclipse

- •1.9.2 Список заданий выполняемых работ

- •1.9.3 Проблема типов в языке С

- •1.9.4 Анализ структуры MBR блочных устройств

- •1.9.5 Запрос информации о статусе файлов

- •1.9.6 Неименованные каналы ядра ОС

- •1.9.7 Именованные каналы FIFO

- •1.9.8 Монтирование flashUSB

- •1.9.9 Работа с именами файлов

- •2 Тема 8. Подсистема управления памятью

- •2.1 Классификация способов управления ОЗУ

- •2.2 Программный и аппаратный способы адресации памяти

- •2.3 Страничная и сегментная адресации памяти

- •2.4 Комбинированный способ адресации памяти

- •2.5 Лабораторная работа по теме №8

- •2.5.1 Структура поцесса

- •2.5.2 Определяемые сегменты процесса

- •2.5.3 Создание и удаление процессов из памяти

- •2.5.4 Динамическое выделение и освобождение памяти процесса

- •3 Тема 9. Базовое взаимодействие процессов

- •3.1 Подсистема управления процессами

- •3.2 Синхронизация процессов

- •3.3 Стандарты POSIX

- •3.4 Системные вызовы ОС по управлению процессами

- •3.5 Системный вызов fork() и каналы процесса

- •1.5.1 Пример использования каналов процессов

- •1.5.2 Имитация конвейеров языка shell

- •3.6 Нити (Threads)

- •3.7 Сигналы POSIX

- •3.8 Лабораторная работа по теме №9

- •3.8.1 Системные вызовы общей группы

- •3.8.2 Управление потоками процессов

- •3.8.3 Обработка сигналов ОС

- •4 Тема 10. Асинхронное взаиодействие процессов

- •4.1 Проблемы распределения ресурсов ОС

- •4.2 Системный пакет IPC

- •4.3 Утилиты управления средствами пакета IPC

- •Утилита ipcmk

- •Утилита ipcs

- •Утлита ipcrm

- •4.4 Семафоры

- •4.5 Задача об обедающих философах

- •4.5.1 Описание задачи

- •4.5.2 Выбор стратегии решения

- •4.5.3 Модель философа

- •4.5.4 Программа-монитор

- •4.6 Лабораторная работа по теме №10

- •4.6.1 Синхронизация двух процессов

- •4.6.2 Задача «Обедающие философы»

- •5 Тема 11. Эффективное взаиодействие процессов

- •5.1 Прикладные средства пакета IPC

- •5.2 Разделяемые сегменты памяти

- •5.3 Задача о читателях и писателях

- •5.4 Передача сообщений

- •5.5 Лабораторная работа по теме №11

- •5.5.1 Задачи с разделяемыми сегментами памяти

- •5.5.2 Программы передачи сообщений

- •6 Тема 12. Системная шина D-Bus

- •6.1 Графические среды ОС

- •6.2 Рабочий стол пользователя

- •6.3 Различия графических сред ОС

- •6.4 X-сервер UNIX

- •6.5 Архитектура шины D-Bus

- •6.5.2 Бибиотека libdbus

- •6.5.3 Проекции ПО D-Bus на языки программирования

- •6.6 Лабораторная работа по теме №12

- •6.6.1 Утилита qdbus

- •6.6.2 Взаимодействие через шину с приложением evince

- •Заключение

- •Список использованных источников

83

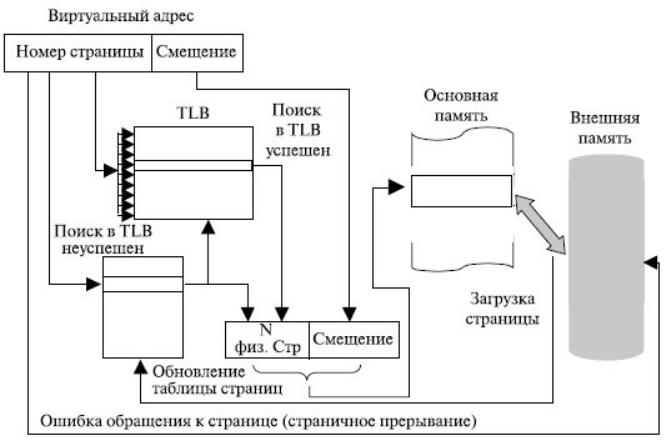

Рисунок 2.12 — Схема адресации страниц с использованием TLB

2.4 Комбинированный способ адресации памяти

Преимущества адресации имеются у каждого способа:

•сегментная адресация памяти — требует относительно малое число записей в таблице сегментов.

•страничная адресация памяти — устраняет проблемы фрагментации, пос-

кольку ОЗУ адресуется с помощью произвольного доступа, следовательно, свободную страницу ОЗУ можно найти в любом месте памяти.

Отсюда возникает идея смешанной (комбинированной) адресации, которая состоит в том, что:

•отдельная программа (процесс) отображается в виде нескольких записей в общей таблице сегментов;

•кажный сегмент, выделенный программе, отображается внутри нее в виде одной или нескольких таблиц страниц.

Общая схема такой адресации приведена на рисунке 2.13.

Таким образом, сегментно-страничная адресация памяти похожа на подобную двухуровневую страничную адресацию.

84

Рисунок 2.13 — Схема сегментно-страничной адресации памяти

При этом:

•существенно уменьшается размер корневой таблицы, постоянно хранящейся в ОЗУ и как следствие ускоряется поиск в ней нужной страницы;

•трехкомпонентная адресация (номер сегмента, номер страницы, смещение) требует аппаратной поддержки виртуализации памяти с помощью MMU, без которой она становится не эффективной;

•появляется возможность оптимизации схем адресации на базе учета разных свойств разных сегментов программы; например, сегменты кода предназначены только для чтения.

Вобщем случае, применяемая схема адресации ОЗУ зависит не только от конструктивных возможностей физической памяти или аппаратной поддержки вируализации памяти с помощью устройств MMU, но и от конструктивных особенностей самого процессора.

На рисунке 2.14 показан пример такой зависимости, который стал поддерживаться процессорами компании Intel, начиная с архитектуры i386.

Здесь выделяются:

•глобальная таблица дескрипторов (GDT), на которую должен указывать специальный регистр процессора — GDTR;

•локальные таблицы дескрипторов (LDT), на которые должен указывать специальный регистр процессора — LDTR.

85

Рисунок 2.14 - Адресация памяти MS Windows на архитектуре i386

Глобальная дескрипторная таблица является единственной и контролизуется ядром ОС, адресуя сегменты процесса и значения регистра LDTR.

Локальные дескрипторные таблицы связаны с конкретными испольняемыми процессами и формируются при их запуске.

Указанная схема адресации, широко используется в ОС MS Windows, по крайней мере, начиная с Windows 2000, выполненной по технологии NT.

Замечание

В качестве указателей на GDT и LDT, используются 16-разрядные слова, в которых младшие три бита имеют специальное значение:

•0-й и 1-й биты — уровень защиты (уровень привилегий) работающей задачи;

•2-й бит используется для различения GDT и LDT.

Подводя итог изложенному в данном разделе учебному материалу, следует понимать, что ОС «скрывает» от процессов детали способов адресации памяти, возлагая реализацию ее распределения на «Подсистему управления памятью».