4597

.pdf1

Министерство образования и науки Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования «Воронежский государственный лесотехнический университет имени Г.Ф. Морозова»

МЕТОДЫ УПРАВЛЕНИЯ ЖИЗНЕННЫМ ЦИКЛОМ

ПРИБОРОВ И СИСТЕМ В РАСШИРЕННЫХ

ПРЕДПРИЯТИЯХ

Методические указания к лабораторным работам для студентов по направлению подготовки 15.04.04 – «Автоматизация технологических процессов и производств»

Воронеж 2016

2

УДК 681.5

Мещерякова, А.А. Методы управления жизненным циклом приборов и систем в расширенных предприятиях / Методические указания к лабораторным работам для студентов по направлению подготовки 15.04.04

– «Автоматизация технологических процессов и производств» для всех форм обучения / А.А. Мещерякова – Воронеж. ФГБОУ ВО «ВГЛТУ», 2016. – 32 с.

Печатается по решению редакционно-издательского совета ВГЛТУ

Рецензент: д.т.н., профессор, зав. кафедрой электротехники и автоматики ФГБОУ ВО «Воронежский государственный аграрный университет имени Петра I» Афоничев Д.Н.

3

4 |

|

Содержание |

|

Введение............................................................................................................... |

5 |

Лабораторная работа № 1 ИНТЕГРИРОВАННАЯ СРЕДА |

|

АВТОМАТИЗИРОВАННОГО ПРОЕКТИРОВАНИЯ XILINX ISE .............. |

6 |

Лабораторная работа № 2 ПРОЕКТИРОВАНИЕ ЛОГИСТИЧЕСКИХ |

|

ЦЕПЕЙ................................................................................................................ |

13 |

Лабораторная работа № 3 ОПЕРАТИВНОЕ ПЛАНИРОВАНИЕ |

|

МАТЕРИАЛЬНЫХ ПОТОКОВ ....................................................................... |

24 |

Библиографический список.............................................................................. |

32 |

5

Введение

Предлагаемые методические указания к лабораторным работам по курсу «Методы управления жизненным циклом приборов и систем в расширенных предприятиях» имеют целью изучения методов управления жизненным циклом изделий (ЖЦИ) в условиях современных форм кооперации предприятий. Рассматриваются методы перехода предприятий к новым организационным формам, средства моделирования бизнеспроцессов, методы создания единого информационного пространства расширенного предприятия, алгоритмы оптимизации бизнеспроцессов ЖЦИ в условиях функционирования предприятия в единой открытой информационной среде.

Процесс изучения дисциплины направлен на формирование следующих концепций:

способностью разрабатывать эскизные, технические и рабочие проекты автоматизированных и автоматических производств различного технологического и отраслевого назначения, технических средств и систем автоматизации управления, контроля, диагностики и испытаний, систем управления жизненным циклом продукции и ее качеством с использованием современных средств автоматизации проектирования, отечественного и зарубежного опыта разработки конкурентоспособной продукции, проводить технические расчеты по проектам, техникоэкономический и функционально-стоимостной анализ эффективности проектов, оценивать их инновационный потенциал и риски (ПК-4);

способностью: выполнять анализ состояния и динамики функционирования средств и систем автоматизации, контроля, диагностики, испытаний и управления качеством продукции, метрологического и нормативного обеспечения производства, стандартизации и сертификации с применением надлежащих современных методов и средств анализа, исследовать причины брака в производстве и разрабатывать предложения по его предупреждению и устранению (ПК-8).

6

Лабораторная работа № 1 ИНТЕГРИРОВАННАЯ СРЕДА АВТОМАТИЗИРОВАННОГО

ПРОЕКТИРОВАНИЯ XILINX ISE

Цель работы: демонстрация полного цикла проектирования программируемых логических интегральных схем (ПЛИС) в интегрированной среде разработки XILINX ISE, начиная с создания нового проекта и заканчивая загрузкой установленной на макетной плате лабораторной установки ПЛИС.

Общие сведения

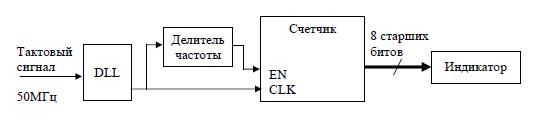

В ходе лабораторной работы создается новый проект 32-разрядного двоичного счетчика, функциональная схема которого представлена на рис. 1. Проект реализуется на макетной плате Digilab2 корпорации Digilent, Inc, содержащей программируемый базовый матричный кристалл (Field Programmable Gate Array - FPGA) Spartan II и обеспечивающей его конфигурирование (загрузку) и простейший контроль функционирования.

Непосредственно на ПЛИС загружается часть схемы, включающей модуль автоподстройки задержек (Delay Locked Loop – DLL), делитель частоты и счетчик. Тактовый сигнал на входе DLL формируется кварцевым генератором макетной платы. В качестве индикатора работоспособности счетчика служит светодиод макетной платы. Проектом предусмотрен вывод на индикатор одного из восьми старших разрядов счетчика. Номер контролируемого разряда задает преподаватель.

Рисунок 1 – Проект «Счетчик»

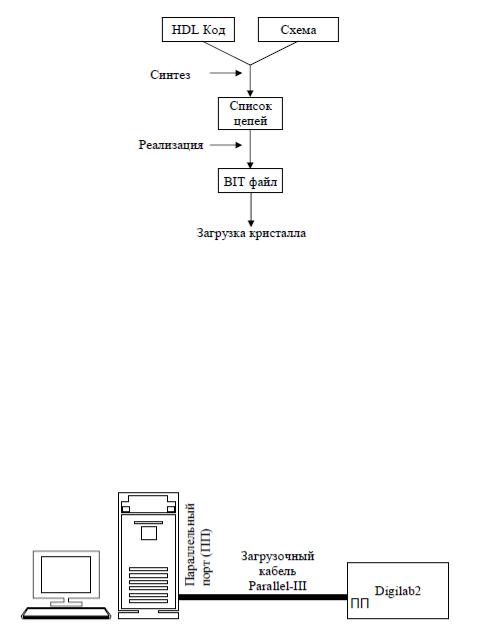

В процессе работы необходимо создать новый проект, подключить к проекту VHDL-файл с описанием счетчика и файл ограничений, корректно назначить электрические цепи выводам ПЛИС, выполнить синтез и реализацию схемы для FPGA Spartan II и сконфигурировать (загрузить) ПЛИС (рис. 2).

7

Рисунок 2 – Цикл проектирования Xilinx

Конфигурирование (загрузка) FPGA Spartan II осуществляется через интерфейс JTAG. Для этого:

1)к разъему параллельного порта макетной платы подключается загрузочный кабель Parallel-III, другой конец которого соединяется с параллельным портом персонального компьютера (ПК) PC (рис. 3);

2)макетная плата переводится в режим конфигурирования через JTAG, для чего с платы удаляются перемычки M0, M1 и M2, а переключатель 1 (SW1) устанавливается в положение JTAG.

Рисунок 3 – Структурная схема лабораторной установки

Загрузка выполняется под управлением программного обеспечения Xilinx. В лабораторной работе применяются ПК с предустановленным программным обеспечением Xilinx ISE. Результаты работы демонстрируются преподавателю.

Создание нового проекта

Шаг 1. Открыть Project Navigator:

Пуск → Программы → Xilinx ISE → Project Navigator.

Шаг 2. Начать новый проект: File → New Project.

Шаг 3. В окне Project Location выберите каталог c:\workshop\labs\01ISEFlows и в окне Project Name введите cleanstart. Щелкните мышкой кнопку <Next>

8

Шаг 4. Выберите Spartan2 в строке Device Family (рис. 4)

Рисунок 4 – Создание нового проекта

Шаг 5. Выберите 2S200-5PQ208 в строках Device, Package, Speed Grade.

Шаг 6. Выберите XST (VHDL/Verilog) в строке Synthesis Tool. Три раза нажмите <Next>, затем кнопку <Finish>.

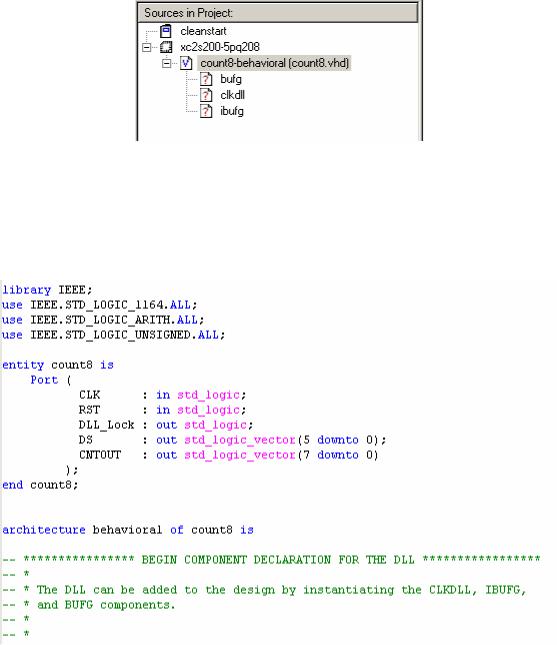

Шаг 7. Добавьте новый источник: Project → Add Copy of Source... Выберите count8.vhd в каталоге 01ISEFlows (рис. 5) и нажмите

<Open>. Убедитесь, что в открывшемся окне выделен тип источника

VHDL Design File и нажмите <OK>

Рисунок 5 – Добавление существующего файла

ISE автоматически подключит исходный файл к проекту и отобразит иерархическую структуру проекта в окне Sources in Project (рис. 6)

9

Рисунок 6 – Отображение иерархии проекта

Шаг 8. Чтобы открыть головной файл проекта, count8.vhd, во встроенном редакторе интегрированной среды Xilinx ISE, дважды щелкните мышкой на этом файле в окне Sources in Project в Project Navigator

Рисунок 7 – Проект «Счетчик»

Реализация проекта

На этом этапе проектирования устанавливается соответствие внутренних сигналов разрабатываемого устройства выводам микросхемы ПЛИС – выводам ПЛИС «назначаются» выходные сигналы проекта. В качестве выходных сигналов проекта, как было отмечено выше, используется 8 старших разрядов 32-разрядного счетчика. Внешним индикатором, отображающим текущее состояние разрядов счетчика, служит светодиод, подключенный к выводу P71 корпуса ПЛИС. Задача, следовательно, состоит в том, чтобы один из разрядов счетчика соединить с выводом P71 (при этом физическое подключение внутренней цепи к выводу микросхемы осуществляется в процессе загрузки в ПЛИС

10

конфигурационного («битового») файла, на текущем этапе лишь дается указание средствам разработки - «назначить» один из внутренних сигналов на определенный вывод). Выводы назначаются в виде ограничений размещения в файле пользовательских ограничений (User Constraint File – UCF). Для данного проекта файл ограничений уже подготовлен. На вывод P71 в нем назначен разряд <3> счетчика, остальные семь разрядов «зарезервированы» путем назначения их на неиспользуемые в плате Digilab2 выводы ПЛИС.

Шаг 1. Чтобы добавить ограничения к проекту, выберите Project → Add Source, и добавьте файл count8.ucf из каталога 01ISEFlows (рис. 8)

Рисунок 8 – Подключение файла пользовательских ограничении (UCF)

Шаг 2. Щелкните правой кнопкой мыши на процессе Generate Programming File (рис. 10) в окне Processes in Source. В появившемся меню выберите команду Proprties… Перейдите на закладку Startup Options

и в строке FPGA Start-Up Clock выберите вариант JTAG Clock (рис. 9).

Рисунок 9 – Установка параметров создания загрузочного файла