МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РОССИЙСКОЙ ФЕДЕРАЦИИ

Федеральное государственное бюджетное образовательное учреждение высшего профессионального образования

ЧУВАШСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ имени И.Н. УЛЬЯНОВА

Факультет Электроэнергетический

Кафедра ТОЭ и РЗА

КУРСОВАЯ РАБОТА

по учебной дисциплине

«МИКРОПРОЦЕССОРНЫЕ СИСТЕМЫ УПРАВЛЕНИЯ»

Проектирование в среде «MAX+Plus II»

Вариант 13

Выполнил: студент группы МЭЭ 03-12

Добронравов Е.Ю.

Принял: к.т.н., доцент

Козлов В.Н.

Чебоксары 2012

Содержание

ЗАДАНИЕ 3

Анализ исходной схемы 4

Анализ работы исходной схемы 7

Внесение изменений в исходную схему 8

Изменение адресов регистров RA, RB, регистра дискретных входов RSA и результата логической функции Y 8

Добавление функции блокировки 10

Выводы 12

Задание

Необходимо, используя САПР «Max+Plus II», изучить исходную схему, а затем доработать её в соответствии с заданным вариантом, отладить и провести моделирование процессов, происходящих в схеме.

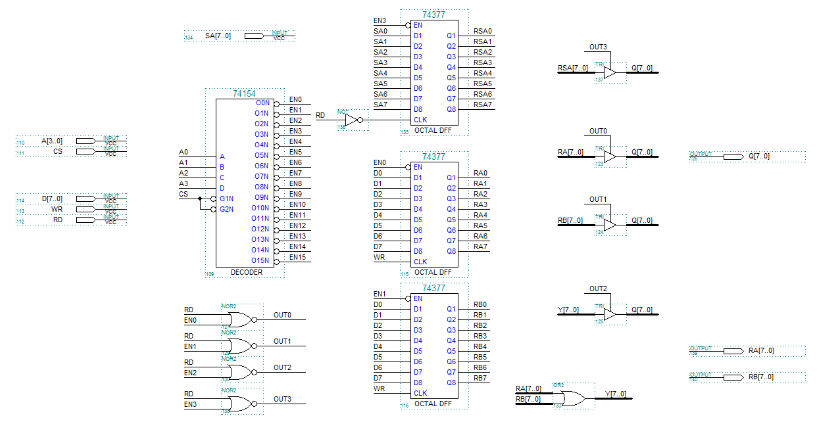

Исходная схема представлена на рисунке 1.

Рисунок 1 – Исходная схема

Изменения, которые следует ввести в схему, представлены в таблице 1.

Таблица 1. Необходимые изменения в схеме.

|

Вариант |

13 |

|

Адрес RA |

13 |

|

Адрес RB |

14 |

|

Адрес дискретных входов |

15 |

|

Тип логической функции |

(RA или не SA) + RB |

|

Адрес результата логической функции Y |

8 |

|

Блокировка |

Запись RA |

|

По какому условию |

RA == 3 |

Анализ исходной схемы

Рассмотрим работу исходной схемы. Для этого сначала рассмотрим работу каждого устройства по отдельности.

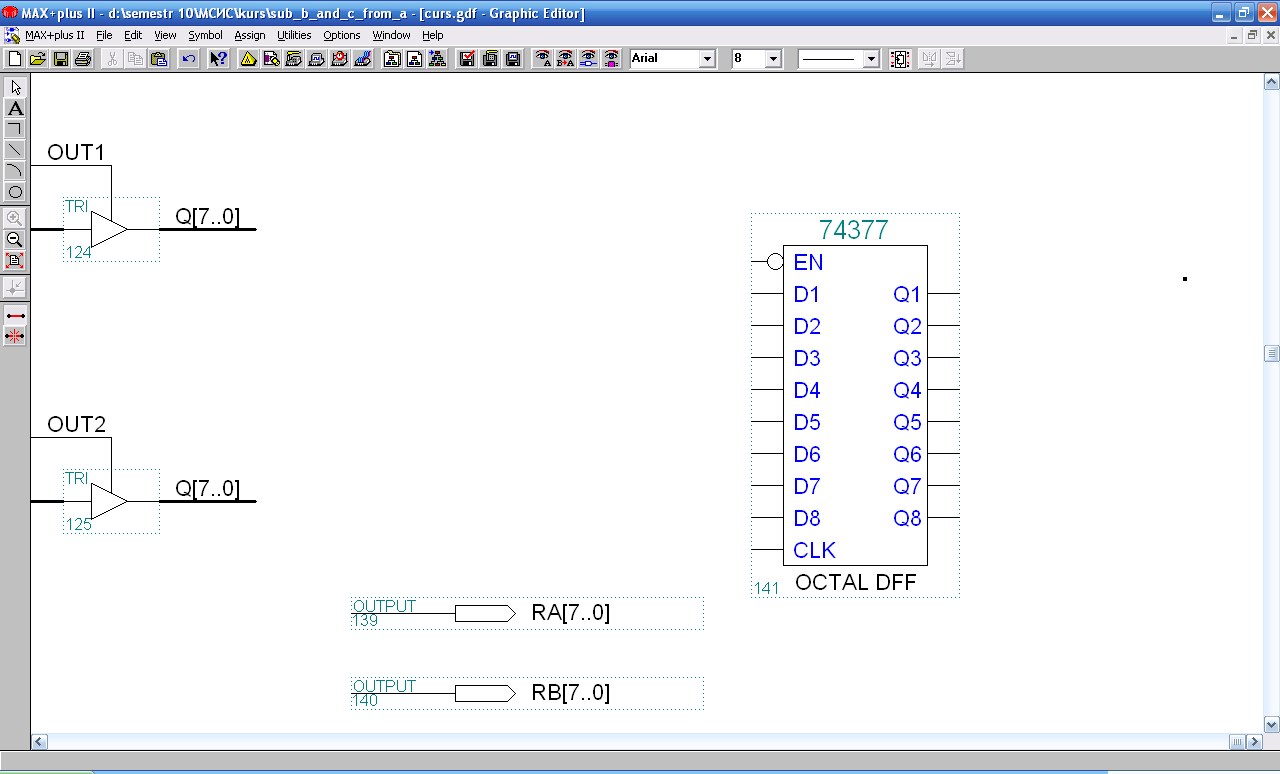

Устройство 74377, внешний вид представлен на рисунке 2.

Рисунок 2 – Устройство 74377

Данное устройство представляет собой регистр-защёлку с восьмиразрядной шиной входных данных (D[7..0]), восьмиразрядной шиной выходных данных (Q[7..0]), входом EN для выбора управляемой микросхемы и входом CLK, который по переднему фронту подаваемого сигнала копирует («защёлкивает») данные с входной шины в выходную. Вход EN осуществляет блокировку сигнала CLK и не позволяет сохранить регистру входное значение. Активное значение для входа EN (выбрать регистр текущим) является логический «0», то есть, подав «1» на вход EN, мы блокируем запись в регистр.

Устройство 74154, внешний вид представлен на рисунке 3.

Рисунок 3 – Устройство 74154

Данное устройство представляет собой дешифратор с четырёхразрядной шиной адреса и максимальными шестнадцатью управляемыми выходами. Подав на вход определённый адрес (от 0b0000 до 0b1111), получим активное логическое значение управляемого выхода, номер которого соответствует адресу. Активное выходное значение для данного устройства это логический «0», что удобно, так как управлять будем описанным выше устройством 74377, а вход EN у него имеет как раз активное значение – «0». Также имеются два входа G1N и G2N, предназначенные для отключения микросхемы на время. Подав логическую «1» на данный вход мы отключим микросхему, и все управляемые выходы примут неактивное состояние. Это также удобно, так как нет необходимости переключать дешифратор на адрес с «висящим» управляющим выходом для отмены выбора текущего выбранного устройства.

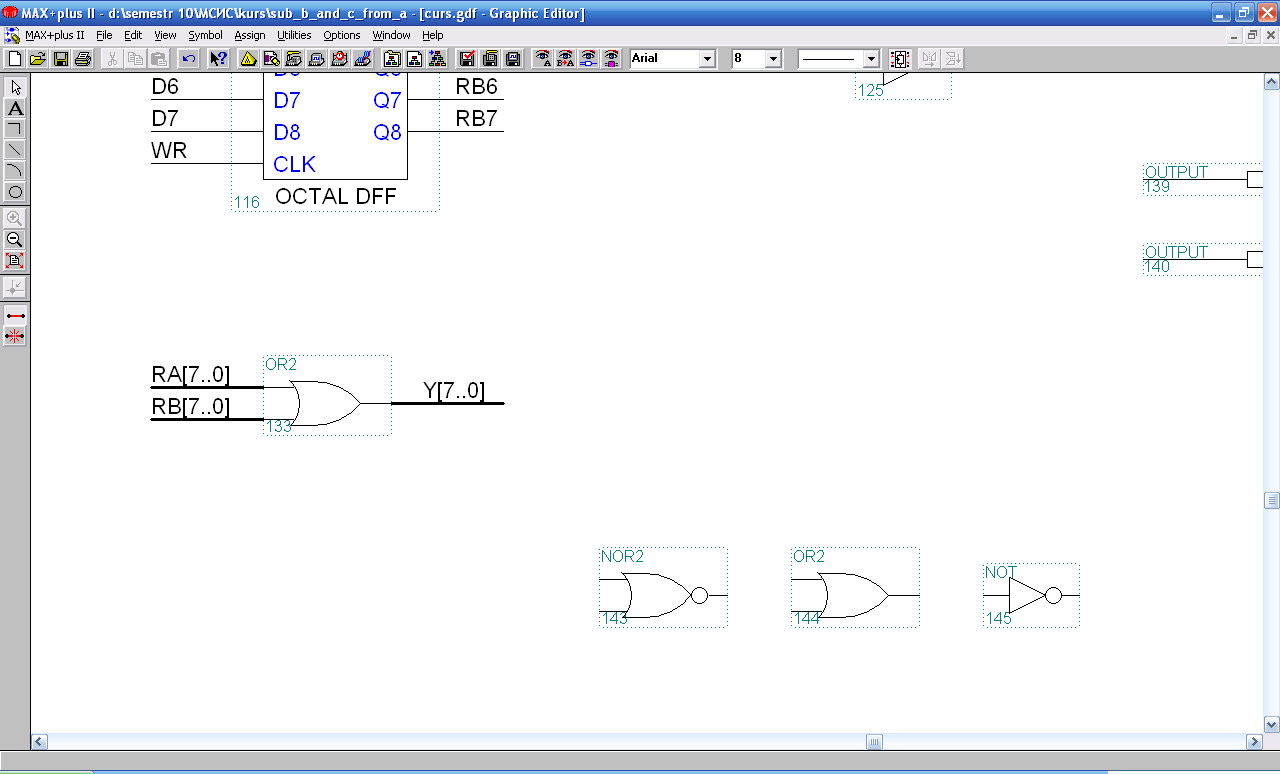

Логические элементы: 2ИЛИ-НЕ, 2ИЛИ и НЕ, представлены на рисунке 4.

Рисунок 4 – Элементы 2ИЛИ-НЕ, 2ИЛИ и НЕ (слева - направо)

Возможные логические состояния на входах и выходах элементов представлены в таблице 2.

Таблица 2. Таблица состояний логических элементов

|

2ИЛИ-НЕ |

|

2ИЛИ |

|

НЕ |

|||||

|

Вход 1 |

Вход 2 |

Выход |

|

Вход 1 |

Вход 2 |

Выход |

|

Вход |

Выход |

|

0 |

0 |

1 |

|

0 |

0 |

0 |

|

0 |

1 |

|

0 |

1 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

|

1 |

0 |

0 |

|

1 |

0 |

1 |

|

|

|

|

1 |

1 |

0 |

|

1 |

1 |

1 |

|

|

|

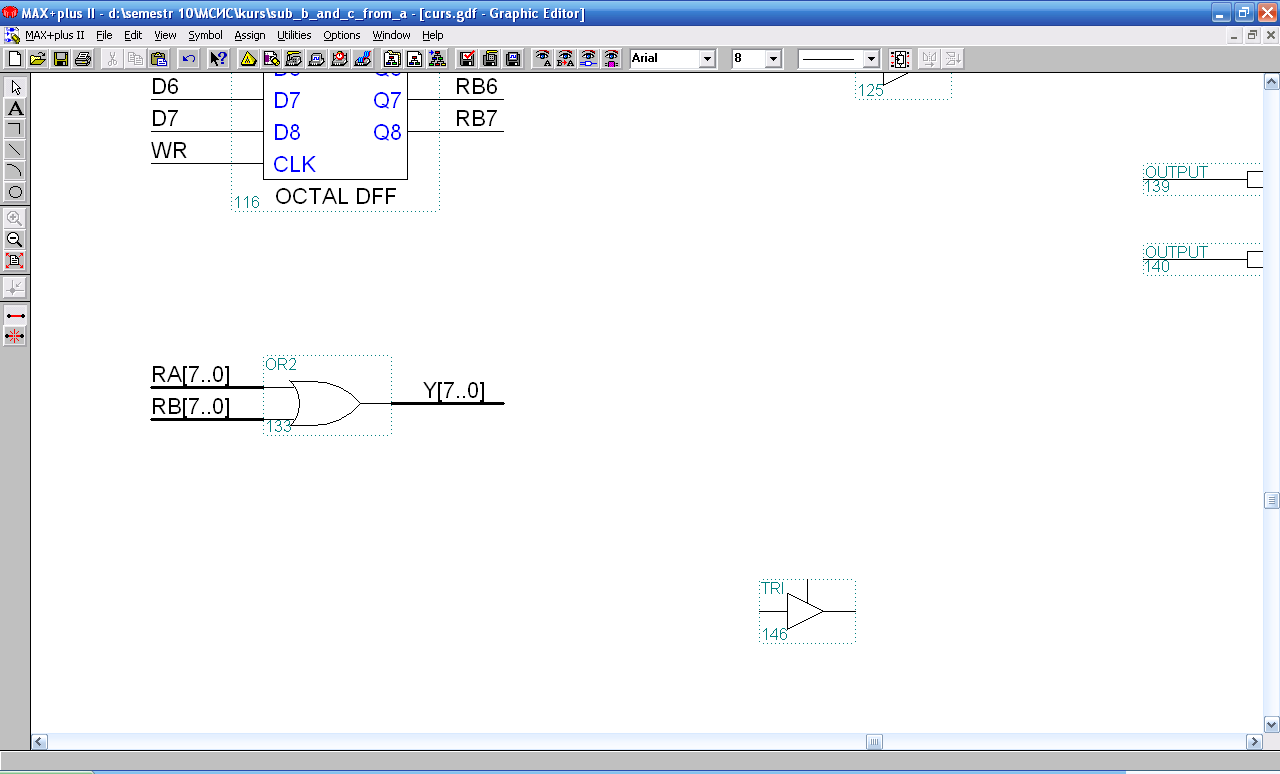

Буфер с тремя состояниями представлен на рисунке 5.

Рисунок 5 – Буфер с тремя состояниями

Данный элемент представляет собой устройство, формирующее на выходе такое же логическое значение, что и на входе при подаче на управляющий вход (на рисунке – сверху) логического значения «1». При логическом «0» на управляющем входе на выходе формируется третье состояние «Z-состояние», когда выход имеет бесконечно большое выходное сопротивление. Это позволит подключить к шине несколько устройств – «мастеров».

Элементы ввода-вывода.

Данные элементы позволяют задать входные и выходные шины всей схемы. САПР, формируя конечное устройство, задаёт в соответствие каждому из элементов ввода/вывода требуемое количество реальных ножек ПЛИС.