- •ПРЕДИСЛОВИЕ

- •1.1. Термины и определения. Общие сведения о сетях связи

- •1.1.1. Основные определения

- •1.1.2. Общие сведения о сетях связи

- •1.1.3. Типовые каналы передачи

- •1.1.4. Способы доставки сообщений

- •1.1.5. Топология сетей связи

- •1.1.6. Эталонная модель взаимодействия открытых систем

- •1.1.7. Краткие сведения о цифровых сетях интегрального обслуживания и об интеллектуальных сетях

- •1.2. Сигналы электросвязи

- •1.2.1. Единицы измерения параметров сигналов электросвязи

- •1.2.2. Аналоговые сигналы электросвязи

- •1.2.3. Цифровые сигналы электросвязи

- •1.2.4. Скорость передачи информации

- •1.2.5. Многомерные цифровые сигналы

- •2.1. Методы формирования и разделения многоканальных сигналов электросвязи

- •2.2. Методы многоканальной передачи сообщений

- •2.2.1. Метод частотного разделения каналов

- •2.2.2. Метод фазового разделения каналов

- •2.2.3. Метод временного разделения каналов

- •3. ДВУХСТОРОННЯЯ СВЯЗЬ

- •3.1. Двухсторонний телефонный канал

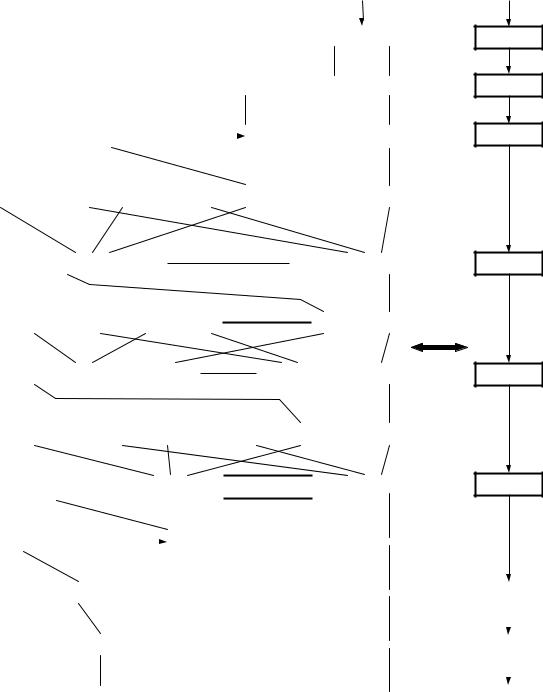

- •3.2. Многоканальные двухсторонние системы передачи

- •3.2.1. Однополосная четырехпроводная система связи

- •3.2.2. Двухполосная двухпроводная система связи

- •3.2.3. Однополосная двухпроводная система связи

- •3.3. Развязывающие устройства

- •3.3.1. Развязывающие устройства на трансформаторах

- •3.3.2. Развязывающие устройства на резисторах

- •3.4. Явление электрического эха

- •3.5. Групповое время замедления

- •3.6. Транзитные соединения и выделение каналов

- •4.1. Построение аналоговых систем передачи

- •4.1.2. Рабочие диапазоны частот аналоговых систем передачи с ЧРК

- •4.1.3. Линейный тракт аналоговых систем передачи

- •4.2. Преобразователи частоты

- •5.1. Равномерное квантование значений отсчетов по уровню

- •5.2. Импульсно-кодовая модуляция

- •5.2.1. Реализация ИКМ кодеков с линейной шкалой квантования

- •5.2.2. ИКМ кодеки с нелинейной шкалой квантования

- •5.5. Дельта-модуляция

- •5.6. Вокодеры

- •6. ЦИФРОВЫЕ СИСТЕМЫ ПЕРЕДАЧИ

- •6.1. Иерархия цифровых систем передачи

- •6.2. Группообразование в ЦСП PDH

- •6.2.1. Цикл передачи. Структура цикла первичного потока

- •6.2.2. Структурная схема оконечной станции первичной ЦСП

- •6.2.3. Временно́е объединение цифровых потоков

- •6.2.4. Циклы вторичного, третичного и четверичного потоков европейской иерархии ЦСП

- •6.2.5. Структурная схема оборудования временно́го группообразования

- •6.2.6. Организация каналов передачи дискретной информации

- •6.2.7. Организация каналов звукового вещания

- •6.3. Генераторное оборудование и системы синхронизации

- •6.3.1. Генераторное оборудование

- •6.3.2. Тактовая синхронизация. Выделитель тактовой частоты

- •6.3.3. Цикловая синхронизация

- •6.4. Цифровой линейный тракт

- •6.4.1. Структура цифрового линейного тракта

- •6.4.2. Коды цифровых сигналов в линии передачи

- •6.4.3. Регенерация цифрового сигнала

- •6.4.4. Требования к вероятности ошибки в линейном тракте

- •6.5. Транспортные сети синхронной цифровой иерархии (SDH)

- •6.5.1. Схема мультиплексирования в SDH

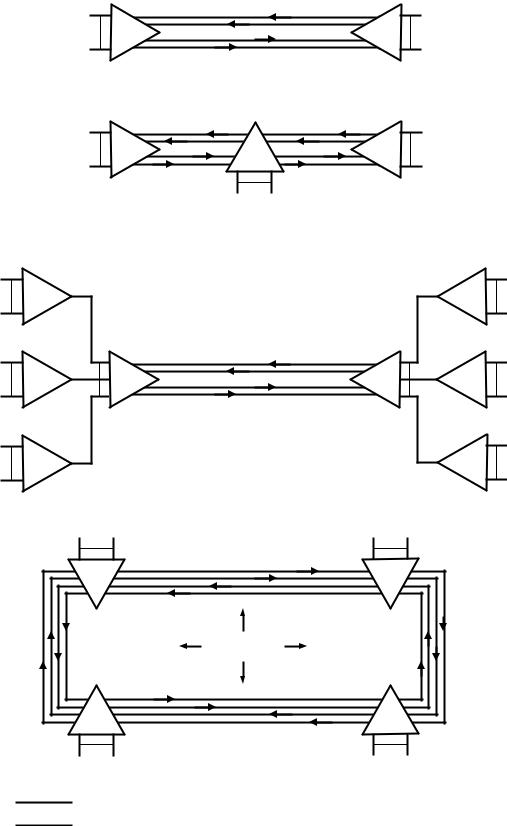

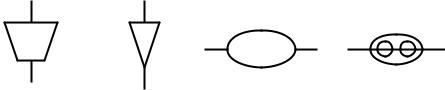

- •6.5.3. Мультиплексоры систем SDH

- •СПИСОК СОКРАЩЕНИЙ

- •АНГЛОЯЗЫЧНЫЕ АББРЕВИАТУРЫ

- •Список литературы

псофометрическая мощность помехи в полосе одного канала ТЧ определяется выражением

Pпсоф = 4123,1 Pошa2σ2kпсоф2 ∆f / (Nfд / 2) ,

где ∆f – ширина спектра группового телефонного сигнала; N – число каналов ТЧ в группе;

kпсоф – псофометрический коэффициент; a =Uогр / σ = 2m−1δ/ σ.

Расчеты показывают, что при вероятности ошибки в линейном тракте Pош =10−6 псофометрическая мощность помех в одном канале ТЧ не превышает 300 пВт. Таким образом, при Pош =10−6 шумы, вызванные ошибочной регенерацией цифрового сигнала в линейном тракте систем с ИКМ и ЧРК (ЧД-ИКМ), малы.

При передаче по системе связи с ИКМ сигналов телевидения наиболее заметными оказываются, как и в системах с ИКМ и ВРК, искажения, вызванные ошибочной регенерацией кодовых символов двухтрех старших разрядов. Эти искажения проявляются в виде мерцающих светлых или темных точек на изображении. Если допустить появление точек не чаще 1 раза в секунду, то при скорости потока, соответствующей передаче телевизионного сигнала 100 Мбит/с, и числе разрядов в кодовой группе m = 8…9 допустимая вероятность ошибочной регенерации составит Pош ≤ 0,5 10−8 .

6.5. Транспортные сети синхронной цифровой иерархии (SDH)

6.5.1. Схема мультиплексирования в SDH

Как уже отмечалось ранее, широкое внедрение волоконно-опти- ческих линий привело к созданию синхронной цифровой иерархии – SDH, предусматривающей, в отличие от PDH, использование синхронного объединения цифровых потоков. При группообразовании в системах SDH на каждой ступени формируется агрегатный сигнал, имеющий определенную структуру (цикл передачи) и названный синхронным транспортным модулем (STM). В качестве базовой скорости

336

в SDH принята скорость сигнала STM первого уровня иерархии (STM-1), равная 155520 кбит/с, а каждая следующая иерархическая скорость ровно в четыре раза превышает предыдущую. В соответствии с этим, различают следующие уровни иерархии:

STM-1 – 155520 кбит/с;

STM-4 – 622080 кбит/с;

STM-16 – 2488320 кбит/с;

STM-64 – 9953280 кбит/с;

STM-256 – 39813120 кбит/с.

Исключение составляет введенный несколько позже STM-0, скорость которого в три раза меньше, чем у STM-1, и равна 51840 кбит/с.

В качестве компонентных сигналов при формировании STM-1 используются потоки, соответствующие европейской и американской плезиохронным цифровым иерархиям (исключением является только европейский вторичный поток со скоростью 8448 кбит/с, использование которого в системах SDH не предусмотрено). Поскольку в данном случае присутствуют два первичных и два третичных потока (европейский и американский), то сигнал со скоростью 1544 кбит/с обозначают как Е11, 2048 кбит/с – Е12, 6312 кбит/с – Е2, 34368 кбит/с – Е31, 44736 кбит/с – Е32, и 139264 кбит/с – Е4.

При формировании STM-N компонентными сигналами могут быть как STM-1, так и STM-M, где M<N. Так, например, STM-16 может быть образован путем объединения шестнадцати STM-1, либо четырех STM-4, которые, в свою очередь, формируются из STM-1. В первом случае мультиплексирование называют прямым, а во втором – каскадным. Мультиплексирование компонентных потоков STM-M осуществляется путем объединения групп по M байт от каждого потока. Таким образом, если объединяются STM-1, то используется побайтное объединение (размер группы равен одному байту), если – STM-4, то объединяются группы по 4 байта от каждого потока и т. д. Данное правило позволяет получить одинаковую структуру модуля STM-N как при прямом, так и при каскадном мультиплексировании.

Независимо от уровня STM длительность цикла отдельного синхронного транспортного модуля равна 125 мкс, т. е. циклы STM передаются с частотой 8 кГц.

337

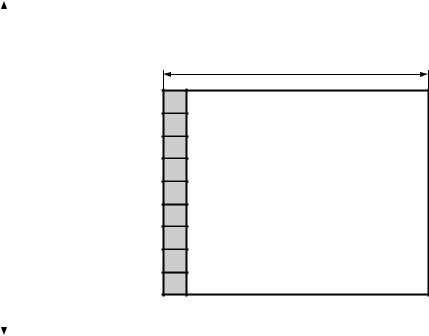

Структуру цикла синхронного транспортного модуля принято представлять в виде прямоугольной матрицы, количество строк в которой равно девяти, а количество столбцов определяется в зависимости от уровня STM. Каждый элемент такой матрицы содержит 1 байт информации, а следовательно, позволяет передавать информацию со скоростью 64 кбит/c.

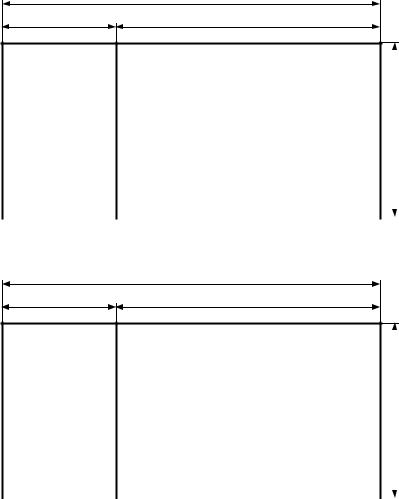

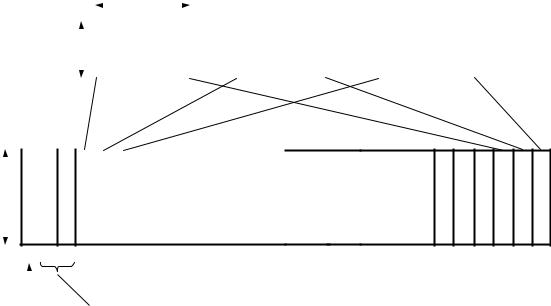

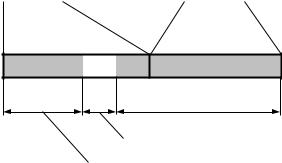

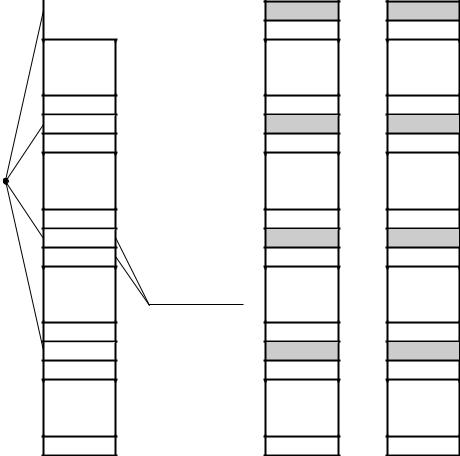

STM-1, структура цикла которого показана на рис. 6.56, а, состоит из 9 строк и 270 столбцов. Таким образом, скорость передачи информации составляет 9 × 270 × 8 бит × 8 кГц = 155 520 кбит/с. Тогда структура STM-N, согласно сказанному выше, будет как на рис. 6.56, б, а скорость передачи соответственно составит N×155520 кбит/с.

|

270 столбцов (байт) |

9 |

261 |

1 |

|

RSOH |

|

|

|

|

|

|

|

|

|

|

|

||

2 |

|

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

4 |

|

PTR |

|

Поле полезной нагрузки |

|

|

9 рядов |

5 |

|

|

|

|

|

||

|

|

|

STM-1 |

|

|

||

6 |

|

|

|

|

|

|

|

|

MSOH |

|

|

|

|

|

|

7 |

|

|

|

|

|

|

|

8 |

|

|

|

|

|

|

|

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а) |

|

|

|

|

270×N столбцов (байт) |

9×N |

261×N |

1 |

|

RSOH |

|

|

|

|

|

|

|

|

|

|

|

||

2 |

|

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

4 |

|

PTR |

|

Поле полезной нагрузки |

|

|

9 рядов |

5 |

|

|

|

|

|

||

|

|

|

STM-N |

|

|

||

6 |

|

|

|

|

|

|

|

|

MSOH |

|

|

|

|

|

|

7 |

|

|

|

|

|

|

|

8 |

|

|

|

|

|

|

|

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

б) |

|

|

|

Рис. 6.56. Структуры циклов

синхронных транспортных модулей STM-1 и STM-N

338

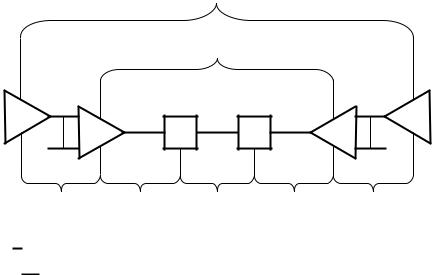

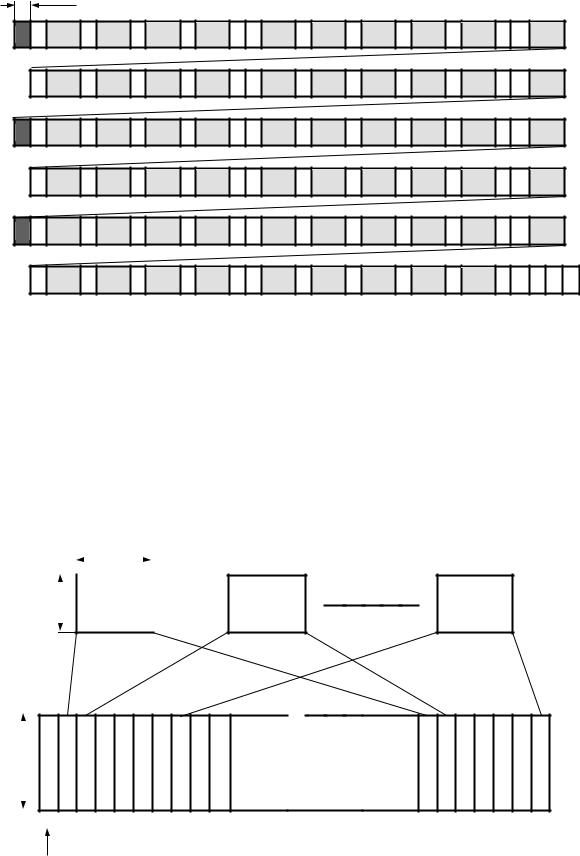

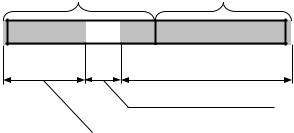

Рассмотрим структуру цикла STM-1 более подробно. Первые 9 столбцов занимает поле служебной информации, а оставшиеся 261 – поле полезной нагрузки. Поле служебной информации включает в себя так называемый секционный заголовок (SOH – Section Overhead) и указатель (PTR – Pointer), расположенный в 4-й строке. Секционный заголовок, содержащий сигналы синхронизации, управления и контроля, делится, в свою очередь, на заголовок регенерационной секции RSOH (Regenerator Section Overhead) и заголовок мультиплексной секции MSOH (Multiplex Section Overhead). Подобное разделение связано с тем, что в системе передачи формально выделяют мультиплексные секции и регенерационные секции (рис. 6.57), и, соответственно, заголовок регенерационной секции (RSOH) заполняется и считывается как

вмультиплексорах, так и в регенераторах, а заголовок MSOH – только

вмультиплексорах. Таким образом, данные заголовки имеют различные области действия (от мультиплексора на передаче до такого же мультиплексора на приеме, или от регенератора до регенератора), что позволяет оптимизировать систему управления сетью и упростить задачу, связанную с совершенствованием оборудования.

E1, 2, 3, 4

|

MSOH |

|

STM-1 |

|

MSOH |

|

STM-N |

STM-1 |

STM-1 |

STM-N R |

R STM-N |

E1, 2, 3, 4

E1, 2, 3, 4

RSOH |

RSOH |

RSOH |

RSOH |

RSOH |

STM-1 |

STM-N |

STM-N |

STM-N |

STM-1 |

– мультиплексор

– мультиплексор

– регенератор

– регенератор

Рис. 6.57. Область действия заголовков RSOH и MSOH

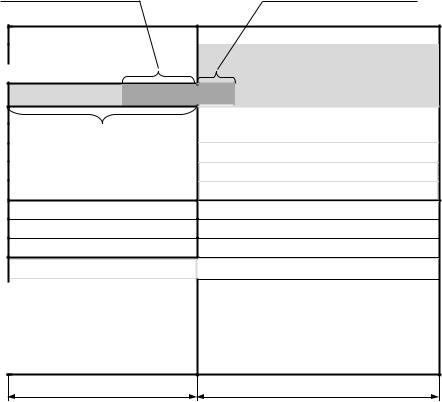

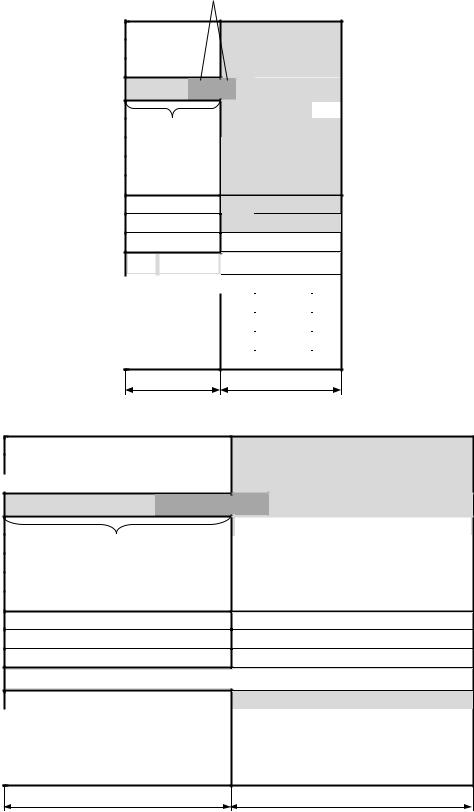

Заголовок регенерационной секции RSOH, структура которого приведена на рис. 6.58, содержит сигнал синхронизации, а также сигналы управления и контроля регенерационной секцией.

339

Шесть байт A1 и A2 отведены под передачу сигнала цикловой синхронизации. Здесь A1 – фиксированная кодовая комбинация вида 11110110, а A2 – 00101000.

Байты D1–D3 предназначены для организации канала сети управления DCC (Data Communication Channel), обеспечивающего передачу данных со скоростью 3 × 8 бит × 8 кГц = 192 кбит/с.

Байт E1 используется для организации канала служебной связи между регенераторами, позволяющего передавать речевой сигнал со скоростью 64 кбит/с.

|

|

|

|

|

9 байт |

|

|

|

|

||

1 |

|

|

|

|

|

|

|

|

|

|

|

A1 |

A1 |

A1 |

A2 |

|

A2 |

|

A2 |

J0 |

|

|

|

2 |

B1 |

|

|

E1 |

|

|

|

|

F1 |

|

|

3 |

D1 |

|

|

D2 |

|

|

|

|

D3 |

|

|

– байты, резервируемые для национального использования

– байты, резервируемые для национального использования

Рис. 6.58. Структура заголовка

регенерационной секции (RSOH) синхронного транспортного модуля STM-1

Контроль ошибок на уровне регенерационной секции осуществляется с использованием процедуры BIP-8 (Bit Interleaved Parity – битовый чередуемый паритет).

Основная идея алгоритма BIP-n заключается в том, что контролируемый блок данных (например, модуль STM) разбивается на n-раз- рядные кодовые комбинации, которые затем складываются друг с другом по модулю 2 (правила сложения по модулю 2 подробно рассматривались в п. 6.2.1. при анализе процедуры CRC-4). Результатом сложения является n-разрядное кодовое слово, используемое в дальнейшем в качестве контрольной суммы, и передаваемое на сторону приема. Приемное устройство снова выполняет расчет BIP-n и сравнивает полученную контрольную сумму с переданной. Если они совпадают, то принимается решение о том, что блок данных передан корректно (без ошибок), в противном случае фиксируются ошибки, причем BIP-n может обнаружить не более n ошибок в блоке, поскольку максимальное число несовпадений при сравнении контрольных сумм равно n.

340

Нетрудно видеть, что процедура BIP-n позволяет обнаруживать только ошибки нечетной кратности (одиночные, тройные и т. д.), а все ошибки четной кратности друг друга компенсируют и обнаружены быть не могут. Так, например, если в двух складываемых кодовых комбинациях окажутся искаженными разряды с одинаковыми номерами, то при сложении эти ошибки друг друга скомпенсируют и обнаружены не будут. Эффективность работы BIP-n зависит от вероятности ошибки в тракте pОШ , размеров контролируемого блока и величины n. Данная процедура позволяет получить объективную оценку качества работы системы лишь при малой вероятности ошибки ( pОШ <10−6 ). С учетом того, что системы SDH характеризуются малыми значениями pОШ , BIP-n оказывается достаточно эффективным инструментом контроля качества.

Как уже было сказано выше, на уровне регенерационной секции используется BIP-8. При этом контролируемым блоком является модуль STM-1, а контрольная сумма длиной восемь бит, или один байт, размещается в заголовке RSOH на позициях байта B1 следующего STM-1.

Байт F1 предназначен для организации так называемого канала пользователя. Данный канал может быть задействован оператором сети для эксплуатационных нужд как канал передачи данных или речи в пределах регенерационной секции.

Байт J0 – идентификатор трассы регенерационной секции, представляет собой фактически адрес узла назначения для данного агрегатного потока. Подобная информация позволяет осуществлять непрерывный контроль за прохождением сигнала с передающей стороны на приемную. Для передачи идентификатора организуется шестнадцатибайтный цикл, структура которого приведена в табл. 6.10 (передача осуществляется в шестнадцати последовательных синхронных транспортных модулях). Первые биты J0 отведены под передачу циклового синхросигнала, представляющего собой комбинацию 1000...0. Как видно из табл. 6.10, первый байт включает в себя результат вычисления CRC-7 по предыдущему циклу (процедура CRC была подробно рассмотрена в п. 6.2.1). Следующие 15 байт используются для передачи идентификатора.

341

Таблица 6.10

Номер байта |

|

|

|

|

|

|

Значение байта J0 |

|

|

|

|

|

|

|||||||

в цикле |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

1 |

|

|

C1 |

|

C2 |

|

C3 |

|

|

C4 |

|

C5 |

|

C6 |

|

|

C7 |

|

2 |

|

0 |

|

|

X |

|

X |

|

X |

|

|

X |

|

X |

|

X |

|

|

X |

|

3 |

0 |

|

|

X |

X |

|

X |

|

X |

X |

|

X |

|

X |

||||||

|

|

|

|

|

|

|||||||||||||||

. . . |

. . . |

. . . |

. . . |

. . . |

. . . |

. . . |

. . . |

. . . |

|

|||||||||||

|

||||||||||||||||||||

16 |

0 |

|

|

X |

|

|

X |

|

|

|

|

|

|

X |

||||||

|

|

X |

|

|

X |

X |

|

X |

|

|||||||||||

Примечание. C1C2 C3 C4 C5 C6 C7 – контрольная сумма CRC-7;

X...X – значение идентификатора

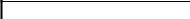

Заголовок мультиплексной секции MSOH модуля STM-1, показанный на рис. 6.59, содержит пять рядов (с 5-го по 9-й, как на рис. 6.56, а) по девять байт в каждом.

Три байта B2 предназначены для реализации процедуры контроля ошибок BIP-24. Поскольку данная процедура используется на уровне мультиплексной секции, то контролируемым блоком является весь модуль STM-1 за исключением заголовка регенерационной секции RSOH. Это объясняется тем, что заголовок RSOH в регенераторах может изменяться, и поэтому, чтобы исключить влияние изменений RSOH на значение байтов B2, заголовок RSOH при расчете контрольной суммы

всоответствии с процедурой BIP-24 не учитывается. Так же, как и

вслучае с заполнением B1 в RSOH, контрольная сумма длиной 24 бита или 3 байта размещается на позициях байтов B2 следующего STM-1.

|

|

|

|

9 байт |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

B2 |

B2 |

B2 |

K1 |

|

|

|

K2 |

|

|

D4 |

|

|

D5 |

|

|

|

D6 |

|

|

D7 |

|

|

D8 |

|

|

|

D9 |

|

|

D10 |

|

|

D11 |

|

|

|

D12 |

|

|

S1 |

|

|

|

|

|

M1 |

E2 |

|

|

– байты, резервируемые для национального использования

– байты, резервируемые для национального использования

Рис. 6.59. Структура заголовка мультиплексной секции (MSOH)

синхронного транспортного модуля STM-1

Байт M1 – индикация ошибки на удаленном конце мультиплексной секции MS-REI (MS Remote Error Indication). Процедура BIP-24 позволяет обнаружить на приемной стороне до 24 несовпадений

342

переданной и рассчитанной контрольных сумм. Число обнаруженных несоответствий кодируется, размещается на позициях байта M1 и передается в обратном направлении – от приемного конца мультиплексной секции к передающему. Возможные значения байта M1 и их интерпретация приведены в табл. 6.11.

|

Таблица 6.11 |

|

|

Байт M1, |

Интерпретация кодовой комбинации |

биты 2÷8 |

(число нарушений BIP) |

000 0000 |

0 |

000 0001 |

1 |

000 0010 |

2 |

. . . |

. . . |

001 0111 |

23 |

001 1000 |

24 |

001 1001 |

0 |

001 1010 |

0 |

. . . |

. . . |

111 1111 |

0 |

Примечание. Значение бита 1 байта M1 игнорируется.

Байт E2, по аналогии с E1 в RSOH, используется для организации канала служебной связи между мультиплексорами.

Байты D4–D12 предназначены для организации канала сети управления DCC на уровне мультиплексной секции, обеспечивающего передачу данных со скоростью 9 × 8 бит × 8 кГц = 576 кбит/с.

Байт S1, в котором задействованы только биты с 5-го по 8-й, несет информацию о статусе синхронизации, а именно, о качестве источника синхронизации (табл. 6.12), используемого в данном мультиплексоре.

|

Таблица 6.12 |

|

|

|

|

Байт S1, |

Уровни качества источника синхронизации |

|

биты 5–8 |

||

|

||

0000 |

Неизвестное качество |

|

0010 |

Первичный эталонный генератор PRC (Рек. G.811) |

|

0100 |

Транзитный (Рек. G.812) |

|

1000 |

Локальный (Рек. G.812) |

|

1011 |

Источник хронирования синхронной аппаратуры |

|

1111 |

Не используется для синхронизации |

Примечание. Все остальные четырехразрядные кодовые комбинации

являются резервными

343

Два байта K1 и K2 предназначены для формирования канала автоматического защитного переключения APS (Automatic Protection Switching) мультиплексной секции. Биты 6–8 байта K2 используются для передачи либо сигнала индикации аварийного состояния MS-AIS (Multiplex Section Alarm Indication Signal), либо сигнала индикации дефекта на удаленном конце мультиплексной секции MS-RDI (MS Remote Defect Indication). Сигнал MS-RDI поступает с приемной стороны на передающую и несет информацию о том, что на приемном конце обнаружен дефект (сигнал не принимается) или принимается сигнал MS-AIS.

MS-RDI представляет собой кодовую комбинацию «110», а MS-AIS – «111». Данные комбинации располагаются на позициях битов 6–8 байта K2. При возникновении аварийной ситуации и передающая, и приемная стороны должны переключиться на резерв. Чтобы это переключение было согласованным, используется байт K1.

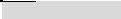

Если формируется STM-N, то заголовки входящих в него STM-1 объединяются. При этом байты A1, A2 и B2 модулей STM-1 включаются в состав заголовка STM-N без изменений, а все остальные байты (J0, B1, E1, E2, F1, D1 – D12, K1, K2, S1, M1), являясь общими для всего STM-N, располагаются только на соответствующих позициях первого модуля STM-1 (STM-1 №1) в составе STM-N. В данном случае процедура BIP-8, используемая на уровне регенерационной секции, выполняется для всего модуля STM-N, а контрольная сумма, соответственно, занимает позиции байта B1 первого модуля STM-1, входящего в состав следующего STM-N. В качестве примера на рис. 6.60 приведен секционный заголовок синхронного транспортного модуля STM-4.

|

|

|

36 байт |

|

|

|

|

|

|

|

|

|

|

A1 |

A1A1A1A1A1A1A1A1A1A1A1 |

A2 |

A2A2A2A2A2A2A2A2A2A2A2 |

J0 |

Z0Z0Z0 |

|

|

|

|

|

|

|

|

B1 |

|

E1 |

|

F1 |

|

|

|

|

|

|

|

|

|

D1 |

|

D2 |

|

D3 |

|

|

|

|

Указатели (PTR) |

|

|

|

|

|

|

|

||||

B2 |

B2B2B2B2B2B2B2B2B2B2B2 |

K1 |

|

K2 |

|

|

|

|

|

|

|

|

|

D4 |

|

D5 |

|

D6 |

|

|

D7 |

|

D8 |

|

D9 |

|

|

|

|

|

|

|

|

|

D10 |

|

D11 |

|

D12 |

|

|

|

|

|

|

|

|

|

S1 |

|

|

M1 |

E2 |

|

|

|

Z0 – байты, резервируемые для будущей международной стандартизации |

|

Рис. 6.60. Структура секционного заголовка (SOH) |

344 |

синхронного транспортного модуля STM-4 |

|

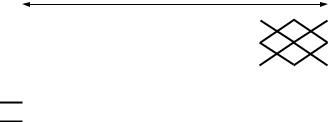

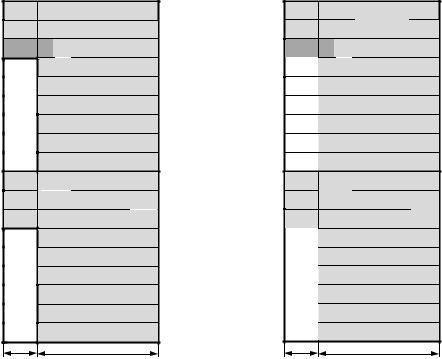

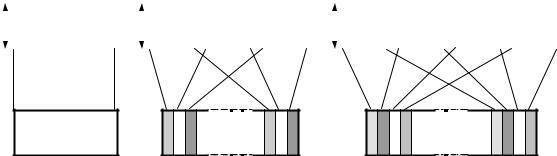

Заполнение поля полезной нагрузки синхронного транспортного модуля осуществляется в соответствии со схемой мультиплексирования, показанной на рис. 6.61. При этом, как следует из схемы, мультиплексирование выполняется поэтапно, т. е. на каждом шаге формируется некоторая промежуточная структура (сигнал, характеризуемый циклом передачи), включающая в себя помимо компонентных информационных сигналов еще и различные служебные сигналы. Представленная схема содержит следующие элементы: контейнер – C (Container); виртуальный контейнер – VC (Virtual Container); трибутивный блок – TU (Tributary Unit); группу трибутивных блоков – TUG (Tributary Unit Group); административный блок – AU (Administrative Unit) и группу административных блоков – AUG (Administrative Unit Group).

STM-N |

×N |

AU-4 VC-4 ×3 |

|

|

|

C-4 |

AUG |

|

TU-3 |

VC-3 |

|

||

|

|

TUG-3 |

|

|

||

|

|

|

|

|

|

|

|

|

×3 |

|

|

|

|

|

|

|

×7 |

|

|

C-3 |

|

|

AU-3 VC-3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

×7 |

TUG-2 |

TU-2 VC-2 |

C-2 |

|

|

|

|

|

|

||

|

|

|

|

×3 |

|

|

|

|

|

|

TU-12 VC-12 |

C-12 |

|

|

|

|

|

×4 |

|

|

|

|

|

|

TU-11 VC-11 C-11 |

||

|

Рис. 6.61. Схема мультиплексирования сигналов |

|

|

|||

Поступающие компонентные сигналы размещаются в контейнерах (C). Каждый контейнер представляет собой цикл передачи длительность которого составляет 125 мкс, а размеры позволяют обеспечить передачу соответствующего компонентного потока (табл. 6.13). Помимо позиций, предназначенных для передачи полезного сигнала, контейнер содержит позиции для размещения служебных сигналов, назначение которых будет рассмотрено ниже. Поскольку компонентные сигналы, как правило, являются плезиохронными, то при их размещении в контейнерах используется двухстороннее согласование скоростей, подробный анализ которого приведен в п. 6.2.3.

345

|

|

|

Таблица 6.13 |

|

|

|

|

Скорость передава- |

|

Размер контейнера, |

Скорость, необхо- |

емого компонент- |

Контейнер |

димая для передачи |

|

ного потока, кбит/с |

|

байт |

контейнера, кбит/с |

|

|

||

1544 |

С-11 |

25 |

1600 |

2048 |

С-12 |

34 |

2176 |

6312 |

С-2 |

106 |

6784 |

34368 или 44736 |

С-3 |

756 |

48384 |

139264 |

С-4 |

2340 |

149760 |

На следующем этапе к контейнеру добавляется заголовок, и получаемая в результате этого структура называется виртуальным контейнером (VC). Таким образом, контейнер представляет собой поле полезной нагрузки виртуального контейнера.

Следует заметить, что разделение процесса формирования виртуального контейнера на два этапа (формирование контейнера (С) и добавление заголовка) является условным и позволяет лишь упростить анализ выполняемых операций, особенно при рассмотрении VC-3 и VC-4, для которых возможны несколько вариантов заполнения поля полезной нагрузки (например, C-4→VC-4 или 3 × TUG-3→VC-4). Иными словами, структура VC формируется изначально, причем, как нетрудно видеть, процесс формирования виртуального контейнера аналогичен процессу формирования цикла в рассмотренных ранее системах PDH. Так, заполнение контейнера (C) эквивалентно размещению компонентного сигнала в цикле агрегатного потока, а заполнение заголовка можно интерпретировать как добавление служебных сигналов (например, сигнала цикловой синхронизации или команд согласования скоростей). Отличие в данном случае заключается лишь в том, что на уровне формирования контейнеров (C) отсутствует мультиплексирование потоков.

Виртуальные контейнеры разделяют на VC низкого порядка и VC высокого порядка. Если VC-m размещается в качестве полезной нагрузки внутри VC-n, то VC-m относят к виртуальным контейнерам низкого порядка, а в случае, когда VC-m располагается непосредственно внутри модуля STM, его относят к виртуальным контейнерам высокого порядка. Как следует из схемы мультиплексирования (рис. 6.61), VC-11, VC-12 и VC-2 всегда размещаются либо в VC-3, либо в VC-4,

346

а поэтому они относятся к виртуальным контейнерам низкого порядка. В свою очередь, VC-4 всегда является виртуальным контейнером высокого порядка, а VC-3, в зависимости от схемы преобразования (на рис. 6.61 показаны оба варианта формирования VC-3), может быть как высокого, так и низкого порядка.

Транспортные телекоммуникационные сети, как известно, предназначены для организации типовых каналов и трактов. В сетях SDH типовыми трактами являются тракты виртуальных контейнеров. В соответствии с введенной выше классификацией различают тракты высокого порядка (для VC-3, VC-4) и тракты низкого порядка (для VC-11, VC-12 и VC-2). Окончаниями тракта любого VC-n считаются точки создания на передающей стороне и считывания на стороне приема заголовка данного виртуального контейнера, а сам заголовок называется трактовым заголовком POH (Path Overhead).

Таким образом, в общем виде виртуальный контейнер представляет собой цикл передачи, содержащий поле полезной нагрузки и трактовый заголовок POH (рис. 6.62).

V5 |

|

|

|

|

|

|

|

|

|

||

Полезная |

|

|

|

|

|

нагрузка |

|

|

|

|

|

|

|

|

|

|

|

J2 |

|

|

|

|

|

Полезная |

|

|

|

|

|

нагрузка |

|

104 |

байта (VC-11) |

||

|

|

||||

|

|

140 |

байт (VC-12) |

||

N2 |

|||||

|

428 |

байт (VC-2) |

|||

Полезная |

|

|

|

|

|

нагрузка |

|

|

|

|

|

|

|

|

|

|

|

K4 |

|

|

|

|

|

Полезная |

|

|

|

|

|

нагрузка |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

85 столбцов для VC-3,

261 столбец для VC-4

J1 |

|

|

B3 |

|

|

C2 |

|

|

G1 |

Полезная нагрузка |

|

F2 |

||

VC-3 или VC-4 |

||

H4 |

||

|

||

F3 |

|

|

K3 |

|

|

N1 |

|

б)

а)

– трактовый заголовок

– трактовый заголовок

Рис. 6.62. Структуры циклов виртуальных контейнеров

а) VC-11, VC-12, VC-2; б) VC-3, VC-4

347

Длительность циклов VC-3 и VC-4 (рис. 6.62, б) составляет 125 мкс, заголовок POH занимает 9 байт, а размеры поля полезной нагрузки совпадают с размерами соответствующих контейнеров C-3 и C-4. Основной особенностью циклов виртуальных контейнеров VC-11, VC-12 и VC-2 (рис. 6.62, а) является то, что циклы имеют длительность 500 мкс, т. е. трактовый заголовок, содержащий в данном случае 4 байта, добавляется не к одному контейнеру, а к структуре из четырех контейнеров C-11, C-12 или C-2.

Сучетом трактовых заголовков, размеры виртуальных контейнеров

искорости, необходимые для их передачи, принимают значения, приведенные в табл. 6.14.

|

|

|

Таблица 6.14 |

|

|

|

|

|

|

|

Размер |

|

Скорость, необходи- |

|

Виртуальный |

Длительность |

мая для передачи вир- |

||

виртуального контейнера, |

||||

контейнер |

байт |

цикла, мкс |

туального контейнера, |

|

|

|

кбит/с |

||

|

|

|

||

VС-11 |

104 |

500 |

1664 |

|

VС-12 |

140 |

500 |

2240 |

|

VС-2 |

428 |

500 |

6848 |

|

VС-3 |

765 |

125 |

48960 |

|

VС-4 |

2349 |

125 |

150336 |

Трактовые заголовки POH виртуальных контейнеров высокого порядка (VC-3 и VC-4) состоят, как уже говорилось ранее, из девяти байт.

J1 – идентификатор трассы тракта виртуального контейнера, используемый для осуществления непрерывного контроля наличия соединения между передающим и приемным терминалами (оконечными устройствами), т. е. между точками формирования на передающей стороне и считывания и обработки на стороне приема данного виртуального контейнера. Для передачи J1 может быть использован свободный формат, когда идентификатор представляет собой кодовое слово длиной 64 байта, либо формат идентификатора точки доступа с организацией шестнадцатибайтного цикла, как для J0, приведенного в табл. 6.10.

Байт B3 предназначен для реализации процедуры внутреннего контроля ошибок с использованием BIP-8 в трактах виртуальных контейнеров высокого порядка. В соответствии с рассмотренным выше

348

алгоритмом BIP-8 (данная процедура применялась при заполнении байта B1 в SOH) осуществляется расчет контрольной суммы по всем битам текущего виртуального контейнера и ее размещение на позициях байта B3 следующего VC.

Байт C2 – метка сигнала (Signal label), указывает состав полезной нагрузки или статус обслуживания виртуального контейнера. Возможные значения байта C2 представлены в табл. 6.15.

Таблица 6.15

Старшие |

Младшие |

Шестнадцате- |

|

|

разряды |

разряды |

Интерпретация |

||

b1–b4 |

b5–b8 |

ричный код |

|

|

|

|

|||

0 0 0 0 |

0 0 0 0 |

00 |

Необорудованный тракт VC |

|

0 0 0 0 |

0 0 0 1 |

01 |

Оборудованный тракт VC, |

|

но тип нагрузки не определен |

||||

|

|

|

||

0 0 0 0 |

0 0 1 0 |

02 |

Нагрузкой являются TUG-3 |

|

0 0 0 0 |

0 0 1 1 |

03 |

Нагрузкой являются TUG-2 |

|

0 0 0 0 |

0 1 0 0 |

04 |

Нагрузкой является контейнер C-3 |

|

0 0 0 1 |

0 0 1 0 |

12 |

Нагрузкой является контейнер C-4 |

|

0 0 0 1 |

0 0 1 1 |

13 |

Нагрузкой являются ячейки ATM |

|

0 0 0 1 |

0 1 0 0 |

14 |

Тракт используется для сети MAN (Metropoli- |

|

tan Area Network – сеть большого города) |

||||

|

|

|

||

|

|

|

Тракт используется для сети FDDI (Fiber Dis- |

|

0 0 0 1 |

0 1 0 1 |

15 |

tributed Data Interface – распределенный ин- |

|

терфейс передачи данных по волоконно-опти- |

||||

|

|

|

||

|

|

|

ческому кабелю) |

|

1 1 1 1 |

1 1 1 0 |

FE |

Нагрузкой является тестовый сигнал согласно |

|

рекомендации O.181 |

||||

|

|

|

||

1 1 1 1 |

1 1 1 1 |

FF |

Сигнал индикации аварийного состояния |

|

VC-AIS |

||||

|

|

|

С помощью байта G1 осуществляется передача в обратном направлении (с приемной стороны на передающую) информации о статусе или состоянии тракта виртуального контейнера. Старшие четыре бита (b1–b4) предназначены для передачи информации о количестве ошибок, обнаруженных процедурой BIP-8. Поскольку максимальное число событий при использовании BIP-8, включая отсутствие обнаруженных ошибок, равно 9, то значения, превышающие 8 (1000), интерпретируются как отсутствие ошибок.

349

Пятый бит (b5) используется для передачи сигнала об аварии на дальнем конце (RDI – Remote Defect Indication – индикация дефекта на удаленном конце). В рабочем состоянии на данной позиции передается «0», а при возникновении аварии – «1».

Биты b6 и b7 позволяют дифференцировать аварийные состояния. Так, передача комбинации 01 на позициях b6-b7 (b5 – «1») интерпретируется как сигнал индикации аварийного состояния – AIS (Alarm Indication Signal), или как потеря указателя – LOP (Loss of Pointer), назначение которого будет рассмотрено ниже. Передача на тех же позициях b6–b7 комбинации 10 интерпретируется как удаленный дефект возможности соединения: TIM (Trace Identifier Mismatch) – несовпадение идентификатора трассы тракта VC, и UNEQ (Unequipped) – необорудованный тракт VC.

Бит b8 является резервным, и его значение приемником игнорируется.

Байты F2 и F3 предназначены для организации каналов пользователей тракта (Path user channels). Иными словами, с помощью этих байтов обеспечивается связь между элементами тракта для пользователей данного тракта.

Байт H4 является индикатором положения полезной нагрузки. В частности, при размещении в циклах VC-3 или VC-4, длительность которых 125 мкс, виртуальных контейнеров низкого порядка (VC-11, VC-12 и VC-2) с длительностью циклов 500 мкс, H4 используется в качестве индикатора сверхцикла, т. е. определяет какая часть цикла VC-11, VC-12 или VC-2 передается в данном VC-3 или VC-4.

Байт K3, в котором задействованы только биты b1–b4, по аналогии с K1 и K2 в MSOH, используется для формирования канала автоматического защитного переключения APS, но на уровне трактов виртуальных контейнеров VC-3 и VC-4.

Байт N1 предназначен для обеспечения функции контроля тандемного соединения TCM (Tandem Connection Monitoring).

Тандемное соединение TC (Tandem Connection) представляет собой соединение сетей нескольких операторов. Тогда можно считать, что тракт виртуального контейнера, передаваемого через тандемное соединение, состоит из трактов, организованных с помощью входящих

350

в TC отдельных сетей. При этом возникает необходимость осуществления контроля ошибок в каждом отдельном тракте.

В качестве процедуры контроля ошибок используется BIP-8. А именно, на входе тракта виртуального контейнера в сети данного оператора выполняется расчет контрольной суммы по всем битам текущего VC, и с помощью байта B3 определяется количество нарушений BIP-8 (количество ошибок) в текущем виртуальном контейнере, которое затем кодируется и размещается на позициях битов b1–b4 байта N1

вследующем VC (табл. 6.16). На выходе данного тракта с помощью процедуры BIP-8 и байта B3 снова определяется количество ошибок

втекущем VC. При этом разность между рассчитанным значением и числом ошибок, записанным в N1, позволяет оценить количество ошибок, появившихся в сигнале при прохождении по сети данного оператора.

|

Таблица 6.16 |

|

|

Количество нарушений |

Байт N1, |

BIP-8 |

биты b1–b4 |

0 |

1 0 0 1 |

1 |

0 0 0 1 |

2 |

0 0 1 0 |

3 |

0 0 1 1 |

4 |

0 1 0 0 |

5 |

0 1 0 1 |

6 |

0 1 1 0 |

7 |

0 1 1 1 |

8 |

1 0 0 0 |

На входе присутствует AIS |

1 1 1 0 |

Бит b5 байта N1 используется для передачи сигнала индикации ошибок в тандемном соединении на дальнем конце TC-REI (TC Remote Error Indication), а бит b6 – для индикации ошибок в выходном сигнале OEI (Outgoing Error Indication). Эти сигналы передаются в противоположных направлениях, и в рабочем состоянии на данных позициях присутствует «0», а при обнаружении блока с ошибками устанавливается «1».

Трактовые заголовки виртуальных контейнеров низкого порядка содержат, как показано на рис. 6.62, а, четыре байта V5, J2, N2 и K4.

351

Байт V5 выполняет те же функции, что и байты B3, G1 и C2 трактовых заголовков VC-3 и VC-4, а его структура приведена на рис. 6.63.

Байт V5

b1 |

|

b2 |

b3 |

b4 |

b5 |

b6 |

b7 |

b8 |

BIP |

-2 |

|

REI |

RFI |

Метка сигнала |

RDI |

||

Рис. 6.63. Структура байта V5

Первые два бита (b1 и b2) используются для реализации процедуры контроля ошибок BIP-2 (аналог байта B3 в трактовых заголовках VC-3, VC-4).

Бит b3 предназначен для передачи сигнала индикации ошибок на дальнем конце (REI). Если при проверке с помощью BIP-2 на приемной стороне ошибок в виртуальном контейнере не обнаружено, то на позиции бита b3 в обратном направлении передается «0», а при обнаружении ошибок – «1».

Четвертый бит (b4) в V5 используется для передачи сигнала индикации отказа на дальнем конце RFI (Remote Failure Indication). Под отказом понимают неисправность, которая фиксируется в течение времени, превышающего время защитного переключения системы. В рабочем состоянии на позиции этого бита передается «0», а при возникновении отказа – «1».

Биты b5–b7 представляют собой метку сигнала, указывающую состав полезной нагрузки и статус обслуживания VC (аналогично байту C2 в заголовке POH виртуальных контейнеров VC-3 и VC-4). Значения этих битов указаны в табл. 6.17.

Таблица 6.17

Байт V5, |

Интерпретация |

|

биты b5–b7 |

||

|

||

0 0 0 |

Необорудованный тракт VC |

|

0 0 1 |

Оборудованный тракт VC, но тип нагрузки |

|

не определен |

||

|

||

0 1 0 |

Асинхронное отображение |

|

0 1 1 |

Бит – синхронное отображение |

|

1 0 0 |

Байт – синхронное отображение |

|

1 0 1 |

Резерв |

|

1 1 0 |

Нагрузкой является тестовый сигнал согласно |

|

рекомендации O.181 |

||

|

||

1 1 1 |

Сигнал индикации аварийного состояния VC-AIS |

352

Бит b8 используется для передачи сигнала индикации дефекта на дальнем конце (RDI). В рабочем состоянии на данной позиции передается «0», а при появлении дефекта, под которым понимают отсутствие возможности нормального приема, на позиции данного бита устанавливается «1».

Байт J2 – идентификатор трассы тракта виртуального контейнера низкого порядка заполняется аналогично байту J1, описание которого было приведено выше.

Байт N2 так же, как и байт N1, используется для обеспечения функции контроля тандемного соединения. Различие в структуре N2 и N1 состоит лишь в том, что в N2 только первые два бита, b1 и b2, предназначены для размещения числа ошибок, обнаруженных с помощью BIP-2 и байта V5. На позиции бита b3 передается фиксированная «1», а бит b4 используется для индикации входящего сигнала AIS.

Байт K4 полностью совпадает с рассмотренным ранее байтом K3, т. е. предназначен для организации канала защитного переключения APS.

Заполнение полей полезной нагрузки виртуальных контейнеров рассмотрим на примерах формирования VC-12 и VC-4, а для случаев VC-11, VC-2 и VC-3 приведем лишь структуры циклов.

Напомним, что полезной нагрузкой виртуального контейнера VC-12 являются четыре контейнера C-12 (рис. 6.62, а) размером 34 байта каждый, позволяющие обеспечить передачу первичного цифрового потока E12 со скоростью 2048 кбит/с. При этом первичный поток может быть как структурированным, т. е. иметь структуру стандартного цикла (рис. 6.2), так и неструктурированным, т. е. представлять собой поток данных со скоростью 2048 кбит/с.

Размещение (отображение или mapping) первичного потока в VC-12 может быть синхронным и асинхронным. В первом случае задающие генераторы источника сигнала и мультиплексора SDH синхронизированы между собой, а во втором – работают независимо.

При асинхронном размещении, которое используется чаще всего, применяется механизм двухстороннего согласования скоростей, подробно

353

рассмотренный в п. 6.2.3. Однако здесь следует заметить, что согласование скоростей в системах SDH имеет особенность. А именно, заполнение виртуальных контейнеров информационными символами осуществляется в соответствии с так называемыми картами – MAP-n , где n – число балластных символов в цикле VC. При выполнении согласования скоростей происходит переход с карты MAP- n к карте MAP- n +1 или MAP- n −1, т. е. число балластных символов увеличивается или уменьшается на единицу, а соответственно количество информационных символов уменьшается или увеличивается также на единицу. Далее заполнение виртуального контейнера осуществляется по карте MAP- n +1 или MAP- n −1 до момента следующей цифровой коррекции. Таким образом, в отличие от плезиохронных систем, в системах SDH, после выполнения операции согласования, возврата в исходное состояние не происходит.

Структура цикла VC-12, соответствующая асинхронному отображению, представлена на рис. 6.64, а. Как следует из рисунка, в цикле VC-12 присутствуют две управляемые вставки S1 и S2, и для каждой из них предусмотрена отдельная команда согласования скоростей – биты C1, C1, C1 и С2, С2, С2, соответственно. Если на позиции вставки передается информационный символ, то команда согласования представляет собой комбинацию 000, а если балластный символ, то – 111.

Поскольку в цикле две управляемые вставки, то количество карт, используемых при заполнении VC-12, равно трем (табл. 6.18).

|

|

|

Таблица 6.18 |

|

|

|

|

|

|

|

Количество |

Количество |

Скорость передачи |

|

|

информационных |

балластных |

||

Карты VC-12 |

информационного |

|||

|

символов в цикле |

символов в цикле |

сигнала, кбит/с |

|

|

VC-12 |

VC-12 |

||

|

|

|||

|

|

|

|

|

MAP-0 |

1025 |

0 |

2050 |

|

|

|

|

|

|

MAP-1 |

1024 |

1 |

2048 |

|

MAP-2 |

1023 |

2 |

2046 |

|

|

|

|

|

354

V5 |

|

|

|

V5 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

||

R R R R R R R R |

|

|

|

R R R R R R R R |

|

|

|

32 байта |

|

|

|

32 байта |

|

|

|

|

|

|

|

|

|

|

|

R R R R R R R R |

|

|

|

R R R R R R R R |

|

|

|

J2 |

|

|

|

J2 |

|

|

|

|

|

|

|

|

|

||

C1 C2 O O O O R R |

|

|

|

1 0 O O O O R R |

|

|

|

32 байта |

|

|

|

32 байта |

|

|

|

|

|

|

|

|

|

|

|

R R R R R R R R |

|

|

140 байт |

R R R R R R R R |

|

|

140 байт |

N2 |

|

|

N2 |

|

|

||

|

|

|

|

||||

|

|

|

|

|

|

||

C1 C2 O O O O R R |

|

|

|

1 0 O O O O R R |

|

|

|

32 байта |

|

|

|

32 байта |

|

|

|

|

|

|

|

|

|

|

|

R R R R R R R R |

|

|

|

R R R R R R R R |

|

|

|

K4 |

|

|

|

K4 |

|

|

|

|

|

|

|

|

|

||

C1 C2 R R R R R S1 |

|

|

|

1 0 R R R R R R |

|

|

|

S2 D D D D D D D |

|

|

|

|

|

|

|

31 байт |

|

|

|

32 байта |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R R R R R R R R |

|

|

|

R R R R R R R R |

|

|

|

|

|

|

|

|

|

||

а) |

|

|

|

б) |

|

|

|

– трактовый заголовок

– трактовый заголовок

R – бит фиксированной вставки;

C – бит команды согласования скоростей;

O – резервный бит заголовка;

S – бит управляемой вставки;

D – информационный бит.

Рис. 6.64. Структуры циклов VC-12 при асинхронном и бит-синхронном

размещении потока E12 со скоростью 2048 кбит/с

Заполнение VC-12 начинается по карте MAP-1. В данном случае на позиции бита S1 передается балластный символ, а на позиции S2 – информационный. Подобное состояние системы соответствует передаче

355

сигнала с номинальной скоростью 2048 кбит/с при отсутствии согласования скоростей. В случае положительного согласования происходит переход к карте MAP-2, т. е. на позициях S1 и S2 передаются балластные символы, а при отрицательном согласовании – наоборот, осуществляется переход к карте MAP-0, а на позициях S1 и S2 передаются информационные символы. Соответственно команды согласования для перечисленных трех вариантов заполнения S1 и S2 принимают вид:

111 (C1 C1 C1), 000 (С2 С2 С2) – MAP-1 (отсутствие согласования); 111 (C1 C1 C1), 111 (С2 С2 С2) – MAP-2 (положительное согласо-

вание);

000 (C1 C1 C1), 000 (С2 С2 С2) – MAP-0 (отрицательное согласование).

При синхронном (бит-синхронном) отображении, которое является частным случаем асинхронного, согласование скоростей отсутствует, а структура цикла VC-12 приобретает вид как на рис. 6.64, б.

Если первичный поток E12 является структурированным, то для его размещения в VC-12 может быть использован синхронный побайтовый ввод (байт-синхронное отображение). Структура цикла VC-12, соответствующая данному варианту размещения, показана на рис. 6.65, а.

Как уже отмечалось ранее, первичный поток позволяет организовать 31 основной цифровой канал (ОЦК) со скоростью 64 кбит/с. В этом случае в цикле VC-12 на позициях КИ0 (рис. 6.65, а) размещаются биты фиксированных вставок (R), и цикл виртуального контейнера имеет вид как на рис. 6.65, б.

При формировании виртуального контейнера VC-4, как следует из схемы мультиплексирования (рис. 6.61), возможны несколько вариантов заполнения его поля полезной нагрузки. Первый вариант предусматривает размещение в VC-4 контейнера C-4 (рис. 6.62, б) размером 2340 байт, позволяющего обеспечить передачу четверичного цифрового потока E4 со скоростью 139264 кбит/с. При использовании второго варианта заполнение поля полезной нагрузки VC-4 осуществляется путем синхронного побайтного мультиплексирования трех групп трибутивных блоков TUG-3.

356

V5 |

|

|

|

V5 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

||

R R R R R R R R |

|

|

|

R R R R R R R R |

|

|

|

КИ0 |

|

|

|

R R R R R R R R |

|

|

|

КИ1 – КИ15 |

|

|

|

Каналы 1 – 15 |

|

|

|

КИ16 |

|

|

|

Канал 16 |

|

|

|

КИ17 – КИ31 |

|

|

|

Каналы 17 – 31 |

|

|

|

R R R R R R R R |

|

|

|

R R R R R R R R |

|

|

|

J2 |

|

|

|

J2 |

|

|

|

R R R R R R R R |

|

|

|

R R R R R R R R |

|

|

|

КИ0 |

|

|

|

R R R R R R R R |

|

|

|

КИ1 – КИ15 |

|

|

|

Каналы 1 – 15 |

|

|

|

КИ16 |

|

|

|

Канал 16 |

|

|

|

КИ17 – КИ31 |

|

|

|

Каналы 17 – 31 |

|

|

|

R R R R R R R R |

|

|

140 байт |

R R R R R R R R |

|

|

140 байт |

N2 |

|

|

N2 |

|

|

||

|

|

|

|

||||

|

|

|

|

|

|

||

R R R R R R R R |

|

|

|

R R R R R R R R |

|

|

|

КИ0 |

|

|

|

R R R R R R R R |

|

|

|

КИ1 – КИ15 |

|

|

|

Каналы 1 – 15 |

|

|

|

КИ16 |

|

|

|

Канал 16 |

|

|

|

КИ17 – КИ31 |

|

|

|

Каналы 17 – 31 |

|

|

|

R R R R R R R R |

|

|

|

R R R R R R R R |

|

|

|

K4 |

|

|

|

K4 |

|

|

|

R R R R R R R R |

|

|

|

R R R R R R R R |

|

|

|

КИ0 |

|

|

|

R R R R R R R R |

|

|

|

КИ1 – КИ15 |

|

|

|

Каналы 1 – 15 |

|

|

|

КИ16 |

|

|

|

Канал 16 |

|

|

|

КИ17 – КИ31 |

|

|

|

Каналы 17 – 31 |

|

|

|

R R R R R R R R |

|

|

|

R R R R R R R R |

|

|

|

а) |

|

|

|

б) |

|

|

|

|

|

|

|

|

|

Рис. 6.65. Структуры циклов VC-12

при байт-синхронном размещении потока E12

со скоростью 2048 кбит/с и 31-го сигнала со скоростью 64 кбит/с

Рассмотрим размещение в VC-4 потока E4. Так же, как и в общем случае формирования VC-12, при заполнении VC-4 используется асинхронное отображение потока E4 с применением механизма двухстороннего согласования скоростей.

357

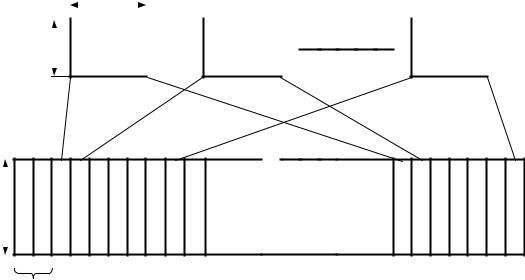

Как видно из рис. 6.62, б, цикл VC-4 состоит из девяти строк. Первый байт каждой строки относится к трактовому заголовку, а оставшиеся 260 байт входят в состав поля полезной нагрузки. Структура одной строки цикла VC-4 при асинхронном отображении потока E4 показана на рис. 6.66.

12 байт

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

POH |

W |

96 D |

X |

96 D |

Y |

96 D |

Y |

96 D |

Y |

96 D |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X |

96 D |

Y |

96 D |

Y |

96 D |

Y |

96 D |

X |

96 D |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Y |

96 D |

Y |

96 D |

Y |

96 D |

X |

96 D |

Y |

96 D |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Y |

96 D |

Y |

96 D |

X |

96 D |

Y |

96 D |

Z |

96 D |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

– трактовый заголовок

– трактовый заголовок

R – бит фиксированной вставки;

C – бит команды согласования скоростей; O – резервный бит заголовка;

S – бит управляемой вставки;

D – информационный бит.

W = DDDDDDDD, X = CRRRRROO, Y = RRRRRRRR, Z = DDDDDDSR

Рис. 6.66. Структура одной строки цикла VC-4

при асинхронном размещении потока E4 со скоростью 139264 кбит/с

Каждая строка цикла VC-4 содержит один символ управляемой вставки – бит S и сигнал управления этой вставкой (команда согласования скоростей), состоящий из пяти символов – биты C. Если на позиции вставки передается информационный символ, то команда согласования представляет собой комбинацию 00000, а если балластный символ, то – 11111.

Поскольку в цикле содержится девять управляемых вставок, то заполнение VC-4 может осуществляться по десяти картам – MAP-0 –MAP-9, параметры которых приведены в табл. 6.19.

358

|

|

|

Таблица 6.19 |

|

|

|

|

|

|

|

Количество |

Количество |

Скорость передачи |

|

|

информационных |

балластных |

||

Карты VC-4 |

информационного |

|||

символов в цикле |

символов в цикле |

|||

|

сигнала, кбит/с |

|||

|

VC-4 |

VC-4 |

||

|

|

|||

|

|

|

|

|

MAP-0 |

17415 |

0 |

139320 |

|

|

|

|

|

|

MAP-1 |

17414 |

1 |

139312 |

|

|

|

|

|

|

MAP-2 |

17413 |

2 |

139304 |

|

|

|

|

|

|

MAP-3 |

17412 |

3 |

139296 |

|

|

|

|

|

|

MAP-4 |

17411 |

4 |

139288 |

|

|

|

|

|

|

MAP-5 |

17410 |

5 |

139280 |

|

|

|

|

|

|

MAP-6 |

17409 |

6 |

139272 |

|

|

|

|

|

|

MAP-7 |

17408 |

7 |

139264 |

|

|

|

|

|

|

MAP-8 |

17407 |

8 |

139256 |

|

|

|

|

|

|

MAP-9 |

17406 |

9 |

139248 |

|

|

|

|

|

Заполнение VC-4, как видно из табл. 6.19, начинается по карте MAP-7, которая соответствует передаче сигнала с номинальной скоростью 139264 кбит/с. При этом в двух строках цикла на позиции бита S передаются информационные символы, а в оставшихся семи строках – балластные символы. В случае выполнения согласования скоростей происходит переход либо к карте MAP-6, либо к карте MAP-8, и в данном состоянии система будет находиться до момента следующей цифровой коррекции.

Второй вариант заполнения VC-4, как уже отмечалось ранее, предусматривает побайтное объединение трех групп TUG-3 (структура TUG-3 будет рассмотрена ниже). При этом размещение TUG-3 в VC-4 осуществляется в соответствии со схемой мультиплексирования, представленной на рис. 6.67.

Аналогично формированию VC-12 и VC-4 происходит заполнение полей полезной нагрузки VC-11, VC-2 и VC-3. Структуры циклов данных виртуальных контейнеров показаны на рис. 6.68–6.71, а параметры соответствующих карт приведены в табл. 6.20–6.23.

359

|

|

|

|

|

|

|

|

|

|

|

|

|

86 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

9 |

|

|

|

|

TUG-3 |

|

|

|

|

TUG-3 |

|

|

|

TUG-3 |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

(A) |

|

|

|

|

|

(B) |

|

|

|

(C) |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

86 |

1 |

|

86 |

|

1 |

86 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VC-4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

A |

B |

C |

A |

B |

C |

A |

|

|

|

|

A B C A B C |

||||||||

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

2 |

3 |

|

4 |

5 |

6 |

|

7 |

|

8 |

9 |

10 |

|

|

|

|

|

|

261 |

||||||

|

|

|

|

|

|

|

|

|

Фиксированные вставки |

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

POH |

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

Рис. 6.67. Мультиплексирование трех TUG-3 в VC-4 |

||||||||||||||||||

Помимо приведенных выше вариантов заполнения VC-3, данный виртуальный контейнер может быть сформирован путем побайтового объединения семи групп TUG-2 (рис. 6.61). Процесс мультиплексирования показан на рис. 6.72, а структура TUG-2 так же, как и упомянутой ранее группы TUG-3 (рис. 6.67), будет приведена ниже.

|

|

|

|

|

Таблица 6.20 |

|

|

|

|

|

|

Карты |

Количество |

|

Количество |

|

Скорость передачи |

информационных |

|

балластных символов |

|

информационного |

|

VC-11 |

|

|

|||

символов в цикле VC-11 |

|

в цикле VC-11 |

|

сигнала, кбит/с |

|

|

|

|

|||

|

|

|

|

|

|

MAP-0 |

773 |

0 |

|

1546 |

|

|

|

|

|

|

|

MAP-1 |

772 |

1 |

|

1544 |

|

MAP-2 |

771 |

2 |

|

1542 |

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 6.21 |

|

|

|

|

|

|

Карты |

Количество |

|

Количество |

|

Скорость передачи |

информационных |

|

балластных символов |

|

информационного |

|

VC-2 |

|

|

|||

символов в цикле VC-2 |

|

в цикле VC-2 |

|

сигнала, кбит/с |

|

|

|

|

|||

|

|

|

|

|

|

MAP-0 |

3160 |

|

0 |

|

6320 |

|

|

|

|

|

|

MAP-1 |

3159 |

|

1 |

|

6318 |

|

|

|

|

|

|

MAP-2 |

3158 |

|

2 |

|

6316 |

|

|

|

|

|

|

360

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Окончание табл. 6.21 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Карты |

Количество |

|

|

Количество |

|

|

Скорость передачи |

||||||||

|

информационных |

|

балластных символов |

информационного |

||||||||||||

|

VC-2 |

|

||||||||||||||

|

символов в цикле VC-2 |

|

в цикле VC-2 |

|

|

сигнала, кбит/с |

||||||||||

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MAP-3 |

3157 |

|

|

|

3 |

|

|

6314 |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MAP-4 |

3156 |

|

|

|

4 |

|

|

|

6312 |

|

||||||

MAP-5 |

3155 |

|

|

|

5 |

|

|

6310 |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MAP-6 |

3154 |

|

|

|

6 |

|

|

6308 |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MAP-7 |

3153 |

|

|

|

7 |

|

|

6306 |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MAP-8 |

3152 |

|

|

|

8 |

|

|

6304 |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V5 |

|

|

|

V5 |

|

|

|

V5` |

|

|

|

|

|

|

|

R R R R R R D R |

|

|

1 0 R R R R D R |

|

P1 P0 H1 H2 H3 H4 F R |

|

|||||

|

|

|

|

|

|

24 байта |

|

|

|

24 байта |

|

|

|

Каналы 1 – 24 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

64 кбит/с |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

J2 |

|

|

|

J2 |

|

|

|

|

J2 |

|

|

|

|

|

|

C1 C2 O O O O D R |

|

|

1 0 O O O O D R |

|

P1 P0 H1 H2 H3 H4 F R |

|

|||||

|

|

|

|

|

|

24 байта |

|

|

|

24 байта |

|

|

|

Каналы 1 – 24 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

64 кбит/с |

|

|||

104 |

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

байта |

|

N2 |

|

|

|

N2 |

|

|

|

N2 |

|

|||||

|

|

|

|

|

C1 C2 O O O O D R |

|

|

1 0 O O O O D R |

|

P1 P0 H1 H2 H3 H4 F R |

|

|||||

|

|

|

|

|

|

24 байта |

|

|

|

24 байта |

|

|

|

Каналы 1 – 24 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

64 кбит/с |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

K4 |

|

|

|

K4 |

|

|

|

K4 |

|

|

|

|

|

|

|

C1 C2 R R R S1 S2 R |

|

|

1 0 R R R R D R |

|

P1 P0 H1 H2 H3 H4 F R |

|

|||||

|

|

|

|

|

|

24 байта |

|

|

|

24 байта |

|

|

|

Каналы 1 – 24 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

64 кбит/с |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а) |

|

б) |

|

|

|

|

в) |

|||

|

|

|

|

– трактовый заголовок |

|

|

H – биты сигнализации (СУВ); |

|||||||||

|

|

|

|

|

|

|||||||||||

|

R – бит фиксированной вставки; |

|

|

|||||||||||||

|

C – бит команды согласования скоростей; |

F – первый бит цикла (рис. 6.6-6.7); |

||||||||||||||

|

O – резервный бит заголовка; |

|

|

P – биты индикатора фазы между H |

||||||||||||

|

S – бит управляемой вставки; |

|

|

и F (сигнал СЦС, поскольку |

||||||||||||

|

D – информационный бит. |

|

|

в данном случае используются |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

выделенные сигнальные каналы). |

|||||

Рис. 6.68. Структуры циклов VC-11 при асинхронном (а), бит-синхронном (б)

и байт-синхронном (в) размещении потока E11 со скоростью 1544 кбит/с

361

байт №1 |

байт №2 |

байты №№3 – 26 |

байт № 27 |

||

|

|

|

|

|

|

V5 |

D D D D D D D R |

(24×8)D |

R R R R R R R R |

|

|

R R R R R R R R |

C1 C2 O O O O D R |

(24×8)D |

R R R R R R R R |

|

|

D D D D D D D D |

C1 C2 O O O O D R |

(24×8)D |

R R R R R R R R |

|

|

R R R R R R R R |

C1 C2 D D D S1 S2 R |

(24×8)D |

|

125 мкс |

|

J2 |

D D D D D D D R |

(24×8)D |

R R R R R R R R |

|

|

R R R R R R R R |

C1 C2 O O O O D R |

(24×8)D |

R R R R R R R R |

|

|

D D D D D D D D |

C1 C2 O O O O D R |

(24×8)D |

R R R R R R R R |

|

|

R R R R R R R R |

C1 C2 D D D S1 S2 R |

(24×8)D |

|

250 мкс |

|

N2 |

D D D D D D D R |

(24×8)D |

R R R R R R R R |

|

|

R R R R R R R R |

C1 C2 O O O O D R |

(24×8)D |

R R R R R R R R |

|

|

D D D D D D D D |

C1 C2 O O O O D R |

(24×8)D |

R R R R R R R R |

|

|

R R R R R R R R |

C1 C2 D D D S1 S2 R |

(24×8)D |

|

375 мкс |

|

K4 |

D D D D D D D R |

(24×8)D |

R R R R R R R R |

|

|

R R R R R R R R |

C1 C2 O O O O D R |

(24×8)D |

R R R R R R R R |

|

|

D D D D D D D D |

C1 C2 O O O O D R |

(24×8)D |

R R R R R R R R |

|

|

R R R R R R R R |

C1 C2 D D D S1 S2 R |

(24×8)D |

|

500 мкс |

|

|

|

а) |

|

|

|

|

|

|

|

||

V5 |

D D D D D D D R |

(24×8)D |

R R R R R R R R |

|

|

R R R R R R R R |

1 0 O O O O D R |

(24×8)D |

R R R R R R R R |

|

|

D D D D D D D D |

1 0 O O O O D R |

(24×8)D |

R R R R R R R R |

|

|

R R R R R R R R |

1 0 D D D R D R |

(24×8)D |

|

125 мкс |

|

J2 |

D D D D D D D R |

(24×8)D |

R R R R R R R R |

|

|

R R R R R R R R |

1 0 O O O O D R |

(24×8)D |

R R R R R R R R |

|

|

D D D D D D D D |

1 0 O O O O D R |

(24×8)D |

R R R R R R R R |

|

|

R R R R R R R R |

1 0 D D D R D R |

(24×8)D |

|

250 мкс |

|

N2 |

D D D D D D D R |

(24×8)D |

R R R R R R R R |

|

|

R R R R R R R R |

1 0 O O O O D R |

(24×8)D |

R R R R R R R R |

|

|

D D D D D D D D |

1 0 O O O O D R |

(24×8)D |

R R R R R R R R |

|

|

R R R R R R R R |

1 0 D D D R D R |

(24×8)D |

|

375 мкс |

|

K4 |

D D D D D D D R |

(24×8)D |

R R R R R R R R |

|

|

R R R R R R R R |

1 0 O O O O D R |

(24×8)D |

R R R R R R R R |

|

|

D D D D D D D D |

1 0 O O O O D R |

(24×8)D |

R R R R R R R R |

|

|

R R R R R R R R |

1 0 D D D R D R |

(24×8)D |

|

500 мкс |

|

б)

R – бит фиксированной вставки; D – информационный бит;

O – резервный бит заголовка; S – бит управляемой вставки; C – бит команды согласования скоростей.

Рис. 6.69. Структуры циклов VC-2 при асинхронном (а), бит-синхронном (б)

размещении потока E2 со скоростью 6312 кбит/с

362

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 6.22 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Карты VC-3 |

|

|

Количество |

|

|

|

Количество |

|