- •1. Счетчики Основные параметры и классификация

- •4. Счётчики с параллельным переносом

- •5. Счетчики с параллельным занесением информации

- •7. Счетчики с произвольным модулем счета и управляемым сбросом

- •8. Генераторы чисел на основе счетчиков

- •9. РегистрыНазначение и классификация

- •11. Параллельно-последовательные регистры

- •12. Использование сдвиговых регистров в качестве счётчиков

- •13. Кольцевой счётчик

- •Счётчик Джонсона

- •14. Одновибраторы

- •14_2 Мультивибраторы

- •15. Формирователи коротких импульсов

- •16. Антидребезговые формирователи импульсов

- •Линейные дешифраторы

- •Многоступенчатые дешифраторы

- •Демультиплексоры

- •19. Мультиплексоры

- •Переключательная функция и синтез мультиплексоров

- •Другие области применения мультиплексоров

- •20. Мультиплексор как генератор логических функций

- •21. Сумматоры

- •Одноразрядные двоичные сумматоры

- •22. Полный одноразрядный сумматор

- •23. Многоразрядные последовательные сумматоры

- •24. Многоразрядные параллельные сумматоры

- •25 Двоично-десятичные сумматоры

- •27. Схема сравнения на равенство

- •28. Схема сравнения на больше

- •29. Контроль по чётности

- •30. Классификация полупроводниковых бис зу

- •Основные параметры зу

- •31. Структурные схемы статических озу с произвольной выборкой

- •32. Элементы памяти статических озу на биполярн транз

- •33. Элементы памяти статических озу на мдп транзисторах

- •Элементы памяти статических озу на кмдп транзисторах

- •34. Элементы памяти и бис озу динамического типа

- •35. Общие сведения, основные параметры и классификация постоянных запоминающих устройств

- •Масочные пзу

- •36. Программируемые пзу

- •37. Репрограммируемые пзу

- •Рпзу с электрическим стиранием информации

- •38. Рпзу с ультрафиолетовым стиранием информации

- •51 Ацп параллельного типа

25 Двоично-десятичные сумматоры

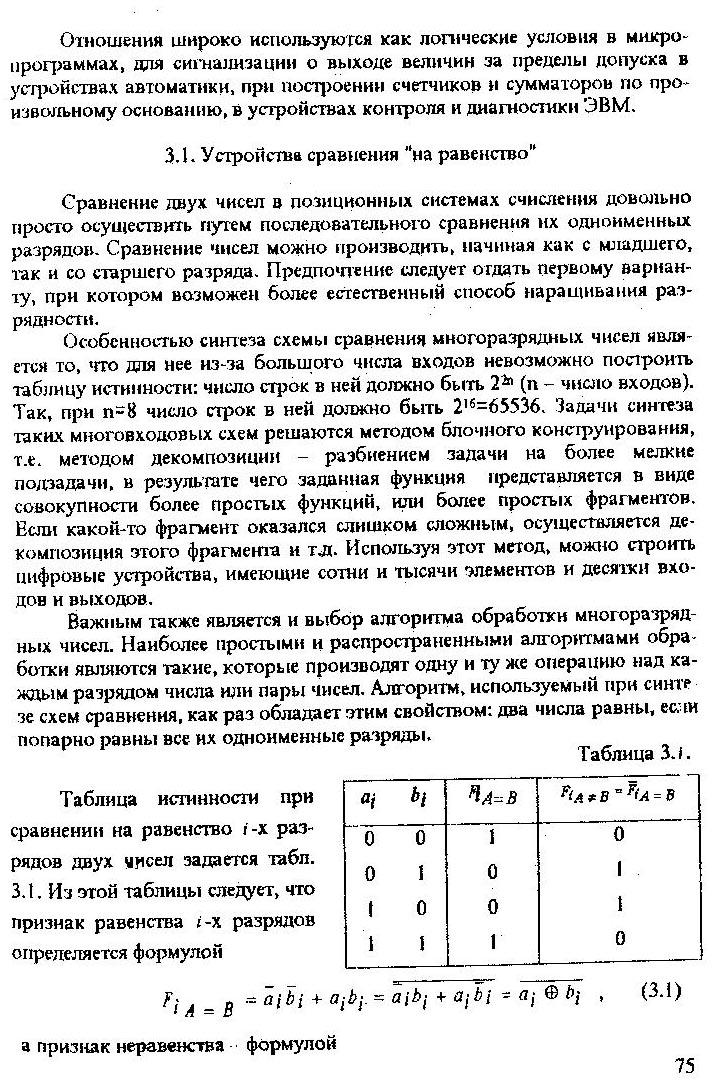

Эти сумматоры выполняют действия над десятичными цифрами, разряды которых закодированы двоичными тетрадами. Если при первичном суммировании тетрад результат не превышает число 9, то коррекция не нужна. Во всех остальных случаях она необходима. Если при первичном суммировании тетрад результат находится в пределах 10... 15, то сигнал переноса не вырабатывается, а полученная тетрада результата не является двоично-десятичной. В этом случае коррекция заключается в выработке сигнала переноса и одновременном уменьшении результата на 10. Вычитание из результата числа 10 можно заменить операцией прибавления к нему дополнительного кода числа 10, имеющим двоичное представление 0110, соответствующее числу 6. Таким образом в данном случае к результату нужно прибавить корректирующую поправку 6 и обеспечить сигнал переноса в старшую тетраду.

Если при первичном суммировании результат превысит число 15, то вырабатывается сигнал переноса в старшую тетраду, цена которого равна 16. Поскольку для двоично-десятичных чисел цена переноса равна 10, то к полученному результату необходимо прибавить число 6.

Схема двоично-десятичной тетрады показана на рис. 15.14. Она содержит сумматоры 1 и 2 и цепи коррекции. Сумматор 1 осуществляет первичное сложение двоично-десятичных тетрад a3a2a1a0 и b3b2b1b0. Коррекция результата первичного суммирования осуществляется сумматором 2, на одни входы которого подается первичное значение суммы, а на другие - корректирующая поправка 0110. При результате 10 и 11, полученном в сумматоре 1, единица переноса в старшую тетраду c1 = l образуется на выходе схемы ИЛИ благодаря конъюнктору И2, а при результате 12 и 13-благодаря конъюнктору И1. В образовании переноса c1 = l при результатах первичного суммирования, равных 14 и 15, участвуют оба конъюнктора, а при результатах, превышающих число 15, в качестве переноса с1 используется перенос с выхода переноса с4 сумматора 1. Во всех этих случаях на входы b3b2b1b0 сумматора 2 поступает корректирующая поправка 0110. Из рис. 15.14 видно, что младший разряд s0 сумматора 1 передается на вход младшего разряда сумматора 2 без изменения (т.к b0 =0), поэтому сумматор 2 может быть 3-разрядным.

26.АЛУ

27. Схема сравнения на равенство

28. Схема сравнения на больше

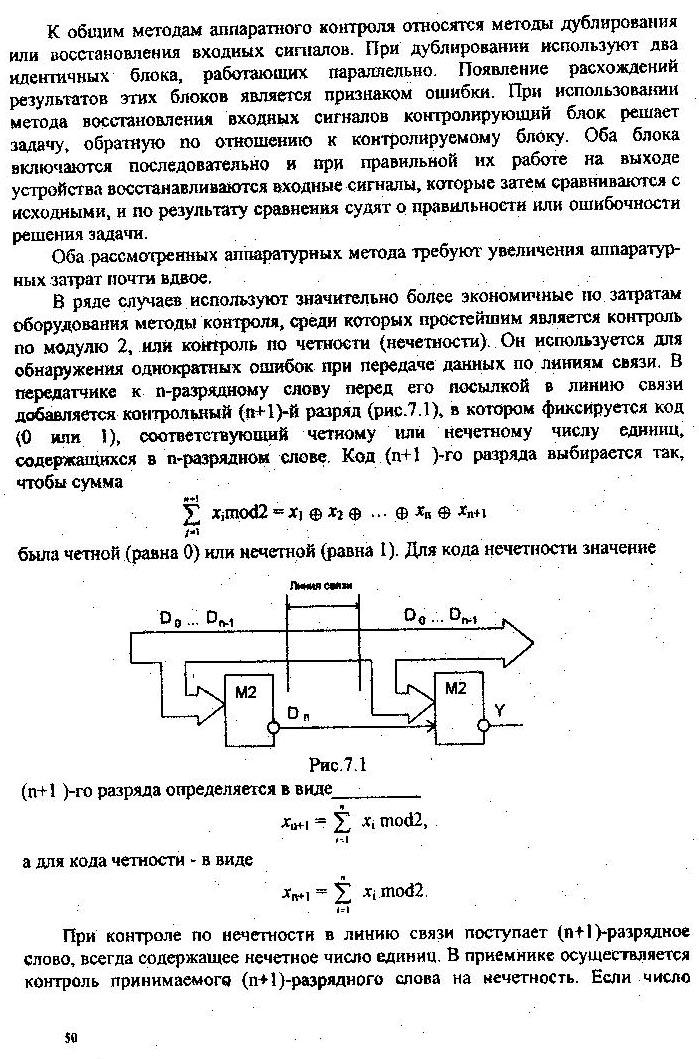

29. Контроль по чётности

30. Классификация полупроводниковых бис зу

Запоминающие устройства (ЗУ) предназначены для хранения, записи и выдачи информации, необходимой для решения задач на ЭВМ. Записываемая, хранимая и считываемая информация представляется в виде слов или слогов в двоичном коде. Каждое слово (слог) располагается в ячейке памяти (ЯП), состоящей из элементов памяти (ЭП). Число ЭП в ЯП определяет разрядность ЯП и разрядность записываемого в неё слова. Конструктивно ЯП объединяются в устройство, называемое блоком памяти.

В современных ЭВМ можно выделить устройства внутренней, внешней и буферной памяти.

Устройства внутренней памяти непосредственно участвуют в процессе преобразования информации, обмениваясь данными с процессором ЭВМ и вычислительной системой.

Внешняя память хранит большие массивы информации в течение длительного времени и обменивается данными с внутренней памятью.

Буферные ЗУ предназначены для промежуточного хранения данных при обмене между внешней и внутренней памятью.

По функциональному назначению БИС ЗУ делят на постоянные (ПЗУ) и оперативные (ОЗУ).

ПЗУ предназначены для хранения данных, однократно фиксируемых при изготовлении (неизменяемых программ, констант и т.п.). Основными требованиями, предъявляемыми к ПЗУ, являются неразрушающее считывание и энергонезависимость хранения информации.

ОЗУ относятся к внутренней памяти, служат для хранения переменных данных и программ в процессе текущих вычислений. В обычных ОЗУ информация разрушается после отключения питания, хотя существуют БИС энергонезависимых ОЗУ.

По технологии изготовления (типу элемента памяти) БИС ЗУ делятся на биполярные, использующие схемотехнику ТТЛ, ТТЛШ, ЭСЛ, И2Л, и униполярные на основе МДП - технологии, использующей структуры р-МДП, n-МДП, КМДП. Новейшими разработками являются ЗУ на основе арсенида галлия, у которых ЭП выполнены на основе полевых транзисторов с барьером Шотки.

По способу хранения информации БИС ЗУ делятся на статические и динамические.

В статических ЗУ применяются бистабильные триггерные элементы. Они управляются потенциальными сигналами и считывание информации происходит без ее разрушения.

В динамических ЗУ для хранения информации используются запоминающие конденсаторы или междуэлектродные ёмкости транзисторов, в которых информация храниться в виде заряда. За счёт токов утечки заряд на конденсаторе с течением времени уменьшается, поэтому его необходимо периодически восстанавливать путём подзарядки. Этот процесс носит название регенерации.

По способу размещения и поиска информации различают БИС ЗУ адресные и безадресные.

В адресных ЗУ поиск информации производиться по номеру (адресу) ячеек памяти, в которых она размещается. Адресные ЗУ бывают с произвольным обращением (произвольной выборкой), когда допустим любой порядок выборки адресов, и с последовательным обращением (последовательной выборкой), когда выбор ЯП возможен только в порядке возрастания или убывания адресов.

Среди безадресных ЗУ можно выделить ЗУ типа "очередь", стековые или магазинные и ассоциативные ЗУ. В ЗУ типа "очередь" считывание информации производится в том же порядке, в котором она была записана (FIFO - первый вошёл, первый вышел ). В ЗУ типа стек (LIFO - последним зашёл, первым вышел) считывание информации производится в порядке, обратном тому, в котором она была записана. В ассоциативных ЗУ поиск информации осуществляется по значению признака поиска, харатеризующего информацию, т.е. по её содержанию.