Постоянные запоминающие устройства (ПЗУ) или память типа ROM (Read Only Memory — память только для чтения) хранят информацию которая вообще не меняется или изменяется редко не в оперативном, а в специальном режиме программирования. В ПЗУ хранится предварительно занесенная информация в виде стандартных подпрограмм, кодов физических констант, постоянных коэффициентов, букв русского и латинского алфавита и т. п. поэтому ПЗУ работают только в режимах хранения и считывания. Одним из основных узлов ЗУ является накопитель, имеющий матричную структуру. Функции элементов памяти накопителя в ПЗУ выполняют программируемые перемычки в виде полупроводниковых диодов или транзисторов, включенные между строками и столбцами матрицы. Наличие перемычки соответствует, например, логической единице, а ее отсутствие — нулю. Это придает свойство энергонезависимости ПЗУ, т. е. сохранения информации при отключении питающих напряжений.

Микросхемы ПЗУ имеют, словарную организацию, при которой информация считывается в форме многоразрядного кода (слова). Совокупность элементов памяти в матрице накопителя, хранящих слово, называют ячейкой памяти. Каждая ячейка памяти имеет свой адрес. Число элементов памяти в ячейке определяет ее разрядность N. Если число адресных входов составляет М, то число ячеек равно 2м, а информационная емкость микросхемы — 2м N бит. Таким образом общим свойством ПЗУ является их многоразрядная (словарная) организация, режим считывания как основной режим работы и энергонезависимость. Вместе с тем выделенные в отдельные группы ПЗУ имеют свои особенности, что делает целесообразным рассмотрение каждой группы ПЗУ отдельно.

1. Масочные пзу

В масочные ЗУ типа ROM(M) данные заносятся при изготовлении микросхем с помощью маски (шаблона) на завершающем этапе технологического процесса. Пользователь не может изменить содержимое памяти. Элементом памяти или связи между строками и столбцами могут быть полупроводниковые диоды, биполярные транзисторы, МОП-транзисторы и другие. В матрице с диодными элементами в узлах, символизирующих логическую единицу изготавливается полноценный диод, а в узлах, символизирующих логический нуль, присутствует неработоспособный диод. Это позволяет использовать один шаблон при изготовлении микросхемы и удешевить производство. Для матриц с МОП-транзисторами при изготовлении транзисторов, символизирующих логический нуль, увеличивают толщину подзатворного слоя. В таких транзисторах paбочее напряжение ЗУ не в состоянии открыть транзистор, что равноценно его отсутствию.

Микросхемы ПЗУ(М) изготовляют согласно биполярной ТТЛ, ТТЛШ-технологии, n-канальной, р-канальной и КМДП-технологиям.

Микросхемы на биполярных транзисторах программируют путем формирования перемычек между строками и столбцами в тех точках матрицы, куда следует занести логическую "1" . В тех точках матрицы, где должен быть логический "0", перемычку не формируют.

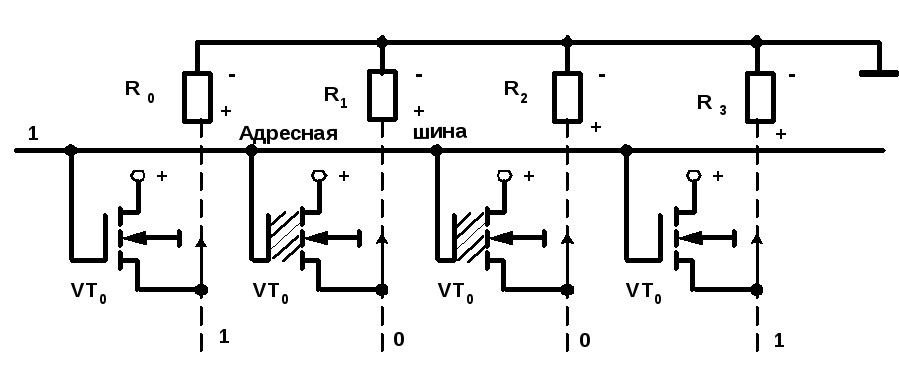

В микросхемах ПЗУ(М), изготовленных по МДП-технологии, элементами памяти являются МДП-транзисторы с каналами n-типа, р-типа. Они включены на пересечениях строк и столбцов матрицы. Программирование таких микросхем осуществляют или по способу формирования перемычек, т. е. по схеме подключения транзисторов к шинам столбцов, или по способу формирования МДП-транзисторов с двумя порогами отпирания: низким и высоким. В матрицах, программируемых по второму способу, все транзисторы соединены с шинами строк и столбцов, как показано на рис.1, но имеют разную толщину подзатворного диэлектрика и разное предельное напряжение: более низкое у транзистора VT0, VT3, что отвечает "1", и более высокое в VT1, VT2, что отвечает "0". При возбуждении адресной строки Xj напряжением, значение которого лежит между двумя предельными напряжениями, транзисторы VT0, VT3 будут открыты, a VT1, VT2 останутся в закрытом состоянии. В результате на разрядные шины РШ0 , РШ3 передается потенциал высокого уровня, а потенциал РШ2 , РШ1 не изменяется. Расхождение в потенциалах разрядных шин исходные усилители трансформируют в стандартные равные напряжения "1" и "0" соответственно.

На рис.1. изображен фрагмент матрицы с МОП-транзисторами. Штриховкой обозначен утолщенный подзатворный слой транзисторов VT1 VT2. С выхода ЗУ снимается код 1001.

Рис.1. Фрагмент матрицы с МОП-транзисторами

Структурные и функциональные особенности ПЗУ(М) рассмотрим на примере устройства с организацией 4х8 (рис.2).

Рис.2. Структурно-функциональная организация ПЗУ с однокоординатной адресацией

Постоянное запоминающее устройство содержит:

матрицу 4x8, в которой функции элементов памяти выполняют элементы односторонней связи между строками и столбцами или отсутствие таковой. Так же, как и в ОЗУ, строки служат для адресации и позволяют произвести выборку требуемого слова. Столбцы играют роль разрядных линий данных или линий считывания. Элементами связи могут быть диоды как в рассматриваемом случае, так и другие полупроводниковые приборы. Включенный между i-й строкой и j -м столбцом (i = 0,1, 2,3 — номера строк, j = 0 1,2,..., 7 – номера столбцов или разрядов хранимого слова) полупроводниковый диод позволяет при определенных условиях создать одностороннюю электрическую связь между ними. При отсутствии диода между i-й строкой и j -м столбцом таковой связи никогда нет. Наличие связи кодируется логической единицей, отсутствие связи — логическим нулем (или наоборот);

дешифратор DC (2x4) адресного кода А1,А0, предназначенный для активизации одной из адресных шин (строк i = 0,1,2,3) с помощью сигнала CS = 0 (Chip Select — выбор кристалла, микросхемы). Для этой же цели используются сигналы с другими названиями, например «чтение памяти»;

резисторы Rо-R7, предназначенные для фиксации логических уровней. Их функции могут выполнять входные сопротивления усилителей считывания подключенных к столбцам матрицы.

Рассмотрим принцип работы ПЗУ. Напомним, что основными режимами работы ПЗУ являются режим хранения и режим считывания.

Если сигнал выбора микросхемы CS = 1, то на всех выходах дешифратора формируются нулевые сигналы, через резисторы Rо-R7 токи не протекают и нулевые сигналы устанавливаются на всех выходах ПЗУ. Такое состояние ПЗУ соответствует режиму хранения.

Режим считывания активизируется путем подачу на входы дешифратора DC адресного кода, например А1,А0 = 01 и сигнала CS = 0. При этом на выходе 1 дешифратора формируется высокий уровень напряжения (логическая единица). Через все диоды, подключенные к строке i = 1, начнет протекать ток, создавая падение напряжения на резисторах R7, R6, R 5, R2,, R1 (рис. 6.17). Из-за отсутствия связей между строкой i = 1 и столбцами j = 4, 3, 0 токи через резисторы R 4, R 3, R0, не протекают и падение напряжения на этих резисторах равно нулю. В результате на выходе запоминающего устройства формируется 8-разрядное слово DO7DO6DO5DO4DO3DO2DO1DO0=11100110.

Еще раз подчеркнем необходимость использования элементов с односторонней проводимостью для организации связи между i-й строкой и /-м столбцом, благодаря которым под напряжением находится только активная строка. Если вместо полупроводниковых диодов включить обычные перемычки с двухсторонней проводимостью, то под напряжением могут оказаться все строки и запоминающее устройство не будет выполнять свои функции.

Недостаток однокоординатной адресации состоит в том, что с увеличением емкости памяти, или числа хранимых слов, растет число выходов дешифратора, что приводит к усложнению его схемы.

Аналогично оперативным ЗУ существуют два пути устранения этого недостатка: каскадирование запоминающих устройств и использование двухкоординатной адресации.

Среди микросхем ПЗУ(М) разных серий многие имеют стандартные прошивки. Например, в микросхемах ПЗУ(М) К155РЕ21—К155РЕ24 записаны соответствующие коды букв русского (РЕ21), латинского (РЕ22) алфавитов, арифметических знаков и цифр (РЕ23), дополнительных знаков (РЕ24). В совокупности эти микросхемы образуют генератор символов на 96 знаков формата 7x5 точек. Одна из микросхем серии КР555РЕ4 содержит прошивки 160 символов, которые отвечают 8-разрядному коду обмена информации КОИ 2-8 с форматом знаков 7x11. Прошивку кодов алфавитно-цифровых символов содержит микросхема КМ1656РЕ2.

Основным динамическим параметром микросхем ПЗУМ является время выборки адреса. При необходимости стробирования исходных сигналов на управляющие входы CS следует подавать импульсы после поступления кода адреса. В таком случае в расчет времени считывания надо принимать время установления сигнала CS относительно адреса и время выбора. У микросхемы KN610PE1 предусмотрен дополнительный сигнал ОЕ для управления выходом.

Исходные сигналы во всех микросхемах ПЗУ(М) имеют ТТЛ-равные уровни. Выходы построены в основном по схеме с тремя состояниями.

Для снижения потребляемой мощности некоторые микросхемы, например, допускают применение режима импульсного питания при котором питание на микросхему подают только при считывании информации.

Особенностью микросхем, обусловленной их назначением, является соединение адресных входов А1 —А15 и выходов данных DO0—DO15 . Исходные формирователи выполнены по схеме на трех состояниях. Три старших разряда кода адреса А15 —А13 предназначены для выбора микросхемы, другие разряды А12 —А1 для выборки слова, которое считывается. Разрешение на прием основного адреса формирует схема сравнения по результату сопоставления принятого и "зашитого" адреса микросхемы. Принятый адрес фиксируется на адресном регистре, а входы/выходы переходят в третье состояние.

Система

управляющих сигналов включает:

![]() —

разрешение чтения данных с ЗУ (иначе

—

разрешение чтения данных с ЗУ (иначе![]() );

);

![]() —синхронизация

обмена (иначе

—синхронизация

обмена (иначе

![]() —разрешение

обращения);

—разрешение

обращения);![]() —

выбор микросхемы,RPLY

—

исходный сигнал готовности данных

сопровождает информацию DO0—DO15

,которая

считывается в магистраль. Режим хранения

обеспечивается сигналами

—

выбор микросхемы,RPLY

—

исходный сигнал готовности данных

сопровождает информацию DO0—DO15

,которая

считывается в магистраль. Режим хранения

обеспечивается сигналами

![]() =

1 или

=

1 или

![]() -

1. В режиме считывания время обращения

к микросхеме определяет сигнал

-

1. В режиме считывания время обращения

к микросхеме определяет сигнал

![]() =

0. Кроме него поступают сигналы кода

адреса на выходы ADO0—АDO15

и

=

0. Кроме него поступают сигналы кода

адреса на выходы ADO0—АDO15

и

![]() =

0. При совпадении адреса ADO15—АDO13

с

адресом микросхемы во входной регистр

поступает адрес слова, которое считывается,

а выходы A

DO0—АDO15

переходят

в третье состояние. Считанное слово из

матрицы записывается в исходный регистр

данных и по сигналу

=

0. При совпадении адреса ADO15—АDO13

с

адресом микросхемы во входной регистр

поступает адрес слова, которое считывается,

а выходы A

DO0—АDO15

переходят

в третье состояние. Считанное слово из

матрицы записывается в исходный регистр

данных и по сигналу

![]() = 0

появляется на выходах DO0—DO15

и

передается

в магистраль. Одновременно на выходе

= 0

появляется на выходах DO0—DO15

и

передается

в магистраль. Одновременно на выходе

![]() формируется

сигнал "0". Исходные регистры

возвращаются в исходное состояние после

снятия сигнала

формируется

сигнал "0". Исходные регистры

возвращаются в исходное состояние после

снятия сигнала

![]() .

.