Дешифрация адреса

Средства сопряжения с системной шиной обеспечивают согласование временных соотношений работы ЗУ и операций чтения/записи, выполняемых на системной шине, а также согласование по нагрузочной способности сигналов и по уровням. Для сопряжения запоминающего устройства необходимо сформировать входные сигналы в соответствии с временными соотношениями работы ЗУ. Состав и структура средств сопряжения с системной шиной определяется архитектурой и нагрузочной способностью системной шины. Оперативные запоминающие устройства реализуются на БИС ОЗУ статического (СТ) или динамического (ДТ) типа.

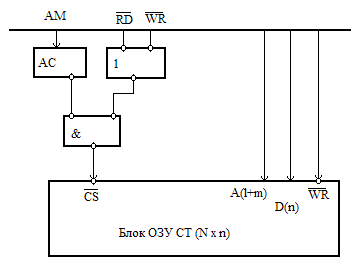

ОЗУ СТ с двунаправленными входами данных сопрягаются с системной шиной данных, а ее адресные входы подключаются непосредственно к соответствующим разрядам адресной шины. На вход записи/чтения необходимо подавать сигнал с управляющей линии записи/чтения, а на вход CS — строб записи/чтения.

ОЗУ ДТ построены на запоминающих элементах емкостного типа и требуют периодической регенерации содержимого ячеек памяти. Для регенерации ОЗУ ДТ, мультиплексирования адресов при выполнении операции записи/чтения ОЗУ, арбитража доступа к ОЗУ используется контроллер ОЗУ ДТ.

Структура дешифратора зависит от элементной базы. Рассмотрим некоторые из них.

Дешифратор на элементах логики

Существует 2 способа задания адреса:

Полная дешифрации (адресация до отдельной ячейки);

Частичная дешифрации (адресация с точностью до области).

Полная дешифрация

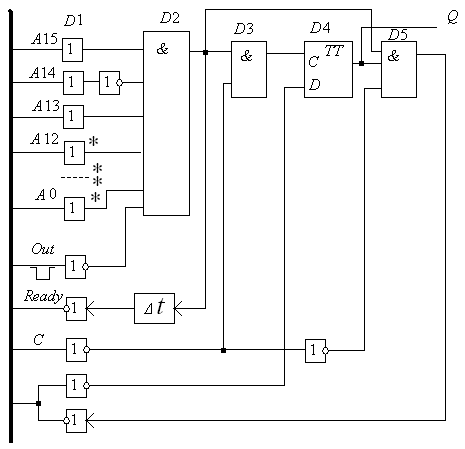

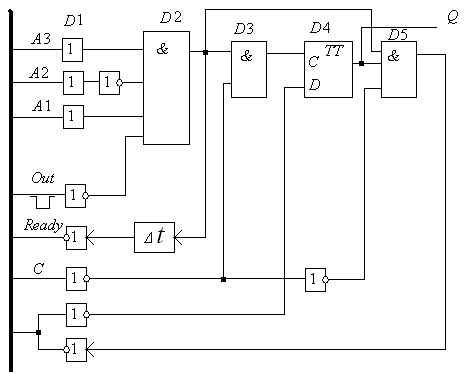

Выберем триггер с адресом BFFF. Нарисуем схему связи триггера с магистралью.

|

|

|

|

Загрузка триггера D4 может производиться при выполнении операции пересылки типа регистр -> память. Предполагается, что младший разряд данных, D0, будет занесен в триггер. При выполнении команды код BFFF выдается в магистраль, проходит адресные приемники D1, на D2 вызывает формирование единичного сигнала на его выходе. В режиме записи D3 срабатывает, дальше по положительному фронту сигнала на входе С триггер D4 принимает информацию с входа D.

Выдача информации из триггера D4 в линию D0 производится при выполнении процессором команды чтения ([BFFF]->A). В результате ее выполнения в младший разряд регистра процессора (аккумулятор) поступает информационный бит из триггера D4. Дополнительно для обмена информацией можно использовать иные команды, имеющие конечным адресом ячейку BFFF.

Частичная дешифрация

Данный метод позволяет сэкономить аппаратуру дешифрации в результате присвоения триггеру не отдельной ячейки адресного пространства, а группы ячеек.

В данном варианте магистральные приемники D1, транслируют 3 старших разряда адреса вместо 16. А число входов элемента D2 сокращается до 4. Адреса, на которые реагирует дешифратор, образуют массив размером 8К ячеек A000-BFFF. Т.е. адрес триггера можно представить 101- - - - -. «-» означает, что данный разряд не имеет значения и может быть задан произвольно. Экономия достигается путем уменьшения количества аппаратуры, снижения массы, потребления электроэнергии и т.д.

Стандартный дешифратор

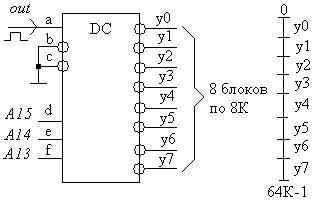

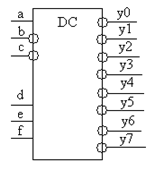

Рассмотрим стандартный дешифратор, у которого есть входа выбора кристалла (a, b, c) и три информационных входа (d, e, f).

Тогда если (a, b, c)≠(100), то y0=y1=…=y7=1. Т.е. дешифратор выключен (a, b, c)=(100), то условие выбора кристалла обеспечивается и его работа описывается таблицей.

|

d e f |

y0 y1 y2 y3 y4 y5 y6 y7 |

|

000 001 010 011 100 101 110 111 |

0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 |

|

|

|

|

Если подключить входы выбора кристалла к линии сопровождения и к общему проводу, а информационные входы подключить к трем старшим линиям адреса шины, то такое включение DC позволяет разбить адресное пространство объемом 64К на 8 зон по 8К ячеек.

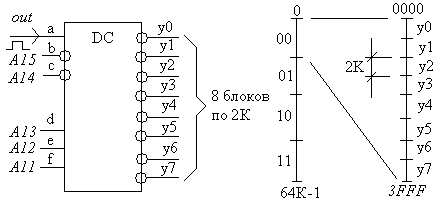

Еще один пример позволяет выделять в адресном пространстве 8 блоков по 2К ячеек. Дешифратор сработает только тогда, когда на входах А15 А14 будут нули, а это обусловливает область в первой 16К, т.е. определяет область адресов от 0000 до 3FFF. В зависимости от сочетаний 0 и 1 на входах А13, А12, А11 можно попасть в одну из 8-ми 2К зон в первой 16К зоне.

|

|

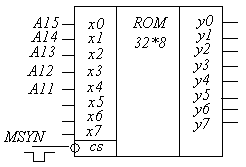

Дешифрация на ПЗУ

Например, пусть требуется выделить зоны адресного пространства для размещения в них адресов отдельных устройств:

1) ПЗУ1 зона F000-FFFF 4К ячеек

2) ПЗУ2 зона E000-EFFF 4К ячеек

3) ОЗУ1 зона A000-A7FF 2К ячеек

4) УВВ зона 8000-87FF 2К ячеек

5) ОЗУ2 зона 0000-3FFF 16К ячеек.

Наименьший блок имеет размеры 2К ячеек, следовательно разрешающая способность дешифратора должна быть не ниже 2К ячеек. Адресное пространство размером 64К ячеек можно разделить используя пять старших разрядов 25=32 части по 2 К.

Исходя из этого нам потребуется ПЗУ с 5-ю адресными входами и 8-ю выходами данных.

|

|

|

|

Далее разработаем таблицу кодировки.

|

Диапазон адресов |

Входы |

Выходы | |||||||||||

|

А15 |

А14 |

А13 |

А12 |

А11 |

Y0 |

Y1 |

Y2 |

Y3 |

Y4 |

Y5 |

Y6 |

Y7 | |

|

0000-07FF |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

X |

X |

X |

|

0800-0FFF |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

X |

X |

X |

|

1000-17FF |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

X |

X |

X |

|

- - - |

|

|

|

|

|

ОЗУ2 |

X |

X |

X | ||||

|

3800-3FFF |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

X |

X |

X |

|

4000-47FF |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

X |

X |

X |

|

- - - |

|

|

|

|

|

пусто |

X |

X |

X | ||||

|

7800-7FFF |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

X |

X |

X |

|

8000-87FF |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

X |

X |

X |

|

8800-8FFF |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

X |

X |

X |

|

|

|

|

|

|

|

пусто |

X |

X |

X | ||||

|

97FF-9FFF |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

X |

X |

X |

|

A000-A7FF |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

X |

X |

X |

|

- - - |

|

|

|

|

и т.д. |

X |

X |

X | |||||

|

E800-EFFF |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

X |

X |

X |

|

F000-F7FF |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

X |

X |

X |

|

F800-FFFF |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

X |

X |

X |

Перераспределение адресного пространства достигается заменой кодировки ПЗУ. При уменьшении кванта деления адресного пространства увеличивается число адресных входов ПЗУ, а объем накопительной матрицы растет пропорционально 2n, где n- число входов. Из-за этого применение ПЗУ оправдано при сравнительно грубом делении.

Дешифрация на ПЛМ

При программировании ПЛМ существует возможность реализовать систему логических выражений, представленную в терминах булевой алгебры.

В начале, все выходы предыдущего уровня связывают с входом ближайшего следующего уровня. Ненужные связи устраняются на этапе программирования ПЛМ. При выполнении операции логического умножения не может быть в выражении более 16-ти членов, так как количество входов элемента «И» не превышает 16. Число самих произведений не может превышать 48 – по числу входов на элементе «ИЛИ.