Триггеры

.pdf

ГЛАВА 1. ЦИФРОВЫЕ УСТРОЙСТВА

1.1. Цифровые последовательностные устройства

1.1.1. Триггер

1.1.1.1. Общие сведения. Классификация

Триггер – простейшее последовательностное устройство, которое может длительно находиться в одном из нескольких возможных устойчивых состояний и переходить из одного в другое под воздействием входных сигналов. Триггер – это один из базовых элементов цифровой техники. Триггер предназначен для хранения значения одной логической переменной (или значения однозначного двоичного числа; при хранении многоразрядных двоичных чисел для запоминания значения каждого разряда числа используется отдельный триггер). В соответствии с этим триггер имеет два состояния: одно из них обозначается как состояние 0, другое – как состояние 1. Воздействуя на входы триггера, его устанавливают в нужное состояние.

При изготовлении триггеров применяются преимущественно полупроводниковые приборы (обычно полевые транзисторы), в прошлом – электронные лампы. В настоящее время логические схемы, в том числе с использованием триггеров, создают в интегрированных средах разработки под различные программируемые логические интегральные схемы (ПЛИС).

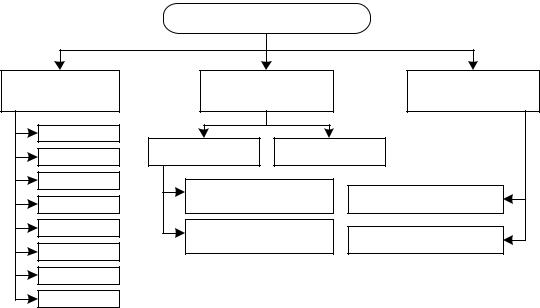

Классификация триггеров приведена на рис. 1.1. Триггеры различают по способу управления, по типу синхронизации и по внутренней организации.

|

Триггеры |

|

||

по способу |

по типу |

по внутренней |

||

управления |

синхронизации |

организации |

||

RS |

|

|

|

|

JK |

синхронные |

асинхронные |

||

|

|

|

||

T |

со статической |

|

||

|

одноступенчатые |

|||

D |

синхронизацией |

|||

|

||||

RR |

с динамической |

двухступенчатые |

||

SS |

синхронизацией |

|||

|

||||

|

|

|

||

EE |

|

|

|

|

DV |

|

|

|

|

Рис. 1.1. Классификация триггеров

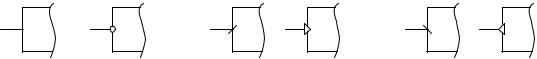

По способу работы с сигналами различают синхронные и асинхронные триггерные схемы. Асинхронный триггер изменяет свое состояние непосредственно в момент появления соответствующего информационного сигнала. Синхронные триггеры реагируют на информационные сигналы только при наличии соответствующего сигнала на так называемом входе синхронизации С (от англ. clock). Этот вход также иногда обозначают терминами строб, такт. Синхронные триггеры в свою очередь подразделяют на триггеры со статическим (статические) и динамическим (динамические) управлением по входу синхронизации С. Статические триггеры воспринимают информационные сигналы при подаче на вход

С логической 1 (прямой вход) или логического 0 (инверсный вход). Динамические триггеры воспринимают информационные сигналы при изменении (перепаде) сигнала на входе С от 0 к 1 (прямой динамический С-вход) или от 1 к 0 (инверсный динамический С-вход). Наиболее распространенные условно-графические обозначения входов синхронизации приведены на рис. 1.2.

C |

C |

C |

C |

C |

C |

Лог. 1 |

Лог. 0 |

Передним фронтом |

Задним фронтом |

||

Рис. 1.2. Условно-графические обозначения входов синхронизации

По внутренней организации триггеры подразделяют на одноступенчатые (однотактные) и двухступенчатые (двухтактные). В одноступенчатом триггере имеется одна ступень запоминания информации, а в двухступенчатом – две такие ступени. Вначале информация записывается в первую ступень, а затем переписывается во вторую и появляется на выходе. Двухступенчатый триггер обозначают ТТ.

По способу управления различают RS, D, JK, T, RR, SS, EE и DV триггеры. Каждый тип триггера имеет собственную таблицу истинности. Выходное состояние триггера обычно обозначают буквой Qt или Qt+1. Индекс возле буквы означает состояние до подачи сигнала (t) или после подачи сигнала (t+1).

Если триггер синхронный, то существует также дополнительный вход синхронизации. Для того чтобы такой триггер учел информацию на синхронных входах, на входе синхронизации необходимо сформировать активный сигнал.

Как правило, входы триггеров обозначают следующим образом:

-S (от англ. Set, установить) – вход в RS-триггере;

-R (от англ. Reset, сброс) – вход в RS-триггере;

-J (от англ. Jump, прыжок) – вход в JK-триггере;

-К (от англ. Kill, убить) – вход в JK-триггере;

-Т (от англ. Toggles, переключить) – счетный вход в Т-триггере;

-С (от англ. Clock, время) вход синхронизирующего сигнала (при тактировании по фронту он часто обозначается стрелкой: стрелка внутрь – тактирование по переднему фронту, наружу – по заднему);

-D (от англ. Delay, задержка) – вход в D-триггере;

-E или EN (от англ. Enable, разрешить) – дополнительный асинхронный управляющий вход для разрешения приема информации (иногда используют букву

V).

Входы J, К, Т, D всегда синхронные, т.е. тактируются по синхронизирующему сигналу на входе C. Разумеется, в каждом конкретном триггере имеются лишь некоторые из перечисленных входных линий. Входы S и R зачастую присутствуют не только в RS триггерах, но и в других типах триггеров, где предназначены, в основном, для асинхронного сброса устройства в 0 или установки в 1.

1.1.1.2. SR-триггер или RS-триггер

RS-триггер или SR-триггер – триггер, который сохраняет свое предыдущее состояние при нулевых входах, и меняет свое выходное состояние при подаче на один из его входов единицы (или наоборот – сохраняет состояние при единичных входах и меняет состояние при нулевых). При подаче 1 на вход S выходное состояние становится равным логической 1, а при подаче 1 на вход R выходное

состояние становится равным логическому 0. Если RS-триггер синхронный, то состояние его входов учитывается только в момент тактирования, например по переднему фронту импульса.

Таблица истинности RS-триггера имеет вид:

S |

R |

Qt+1 |

Функция |

|

|

|

|

|

|

0 |

0 |

Qt |

Хранение |

|

1 |

0 |

1 |

Установка в 1 |

|

|

|

|

|

|

0 |

1 |

0 |

Установка в 0 |

|

|

|

|

|

|

1 |

1 |

х |

Запрещенная |

|

комбинация |

||||

|

|

|

||

|

|

|

|

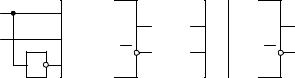

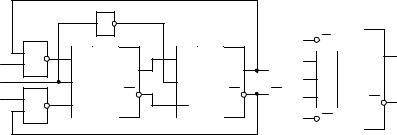

Простейшая логическая схема RS-триггера, реализующая эту таблицу, приведена на рис. 1.3, а. Состояние, при котором на оба входа R и S одновременно поданы логические 1, является запрещенным. Так, согласно схемы RS-триггера (рис. 4.3, а), при подаче на оба инверсных входа лог. 1 триггер перейдет в состояние, когда на обоих выходах будут лог. 0, что не соответствует логике его функционирования, поскольку инверсный выход будет равен неинверсному, т.е. 0 = 1.

RS-триггер также можно реализовать на логических элементах 2И-НЕ. Простейшая схема такого RS-триггера приведена на рис. 1.3, б. Отличие в работе этой схемы заключаться в том, что входы являются инверсными, поэтому сброс и установка триггера осуществляется нулевыми логическими уровнями, а запрещенной комбинацией является подача на оба входа логического 0. Таблица истинности у такого RS-триггера имеет вид:

|

|

|

|

|

|

Qt+1 |

Функция |

S |

|

R |

|

||||

|

|

|

|

|

|

|

|

0 |

|

0 |

|

х |

Запрещенная |

||

|

|

комбинация |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

0 |

|

1 |

|

1 |

Установка в 1 |

||

|

|

|

|

|

|

||

1 |

|

0 |

|

0 |

Установка в 0 |

||

|

|

|

|

|

|

||

1 |

|

1 |

|

Qt |

Хранение |

||

Серийно выпускаемые синхронные одноступенчатые RS-триггеры снабжены дополнительным входом С, на который подается синхросигнал, разрешающий обработку входных сигналов S и R (см. рис. 1.3, в). Неактивное значение синхросигнала обеспечивает на входах запоминающей ячейки состояние управляющих сигналов S = R = 1, что соответствует для нее режиму хранения.

На рис. 1.3, е-ж приведены условно-графические обозначения RS-триггера с различной синхронизацией. Рис. 1.3, г и д иллюстрируют RS-триггер со статической синхронизацией (прямой и инверсной), рис. 1.3, е и ж – с динамической синхронизацией соответственно передним и задним фронтом синхросигнала.

R |

1 |

|

S |

& |

|

S |

& |

& |

|

Q |

Q |

|

Q |

||||||

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

C |

|

|

|

|

1 |

Q |

|

& |

Q |

|

& |

& |

Q |

S |

|

R |

|

|

|

||||

|

|

R |

|

|

|||||

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

а |

|

|

б |

|

|

|

в |

|

|

S T |

Q |

S T |

Q |

S T |

Q |

|

S T |

Q |

|

C |

C |

C |

|

C |

||||

|

|

|

|

|

|

||||

|

R |

Q |

R |

Q |

R |

Q |

|

R |

Q |

|

|

|

|

|

|

||||

|

г |

|

д |

|

е |

|

|

ж |

|

Рис. 1.3. Логическая схема RS-триггера (а, б – упрощенные,

в– серийно выпускаемого синхронного одноступенчатого)

иего условно-графические обозначения (со статической г, д и динамической е, ж синхронизацией)

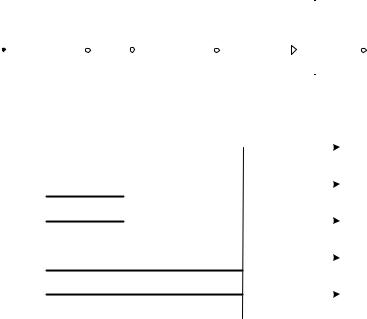

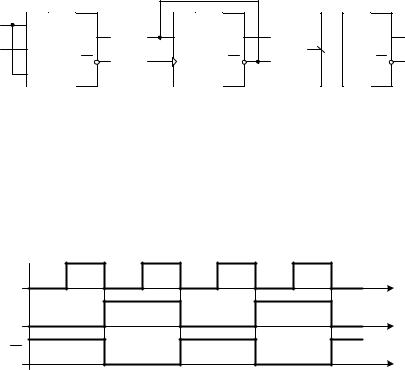

На рис. 1.4 приведена идеализированная (без учета задержек) временная диаграмма работы RS-триггеров с различными типами синхронизации. На временной диаграмме представлены следующие сигналы: C – сигнал синхронизации, R – сигнал сброса триггера в состояние лог. 0, S – сигнал установки триггера в состояние лог. 1, Q0 – прямой выход триггера со статической синхронизацией высоким уровнем синхросигнала, Q1 – прямой выход триггера со статической синхронизацией низким уровнем синхросигнала, Q2 – прямой выход триггера с динамической синхронизацией передним фронтом синхросигнала, Q3 – прямой выход триггера с динамической синхронизацией задним фронтом синхросигнала. Рассмотрим представленную временную диаграмму отдельно для каждого выхода.

Выход Qг. До первого импульса на входе синхронизации C выход триггера находится в состоянии лог. 0, входами R и S задан режим установки. Как только на входе С появляется лог. 1, триггер меняет свое выходное состояние. Как видно из диаграммы, между вторым и третьим синхроимпульсами состояние входов R и S соответствует режиму сброса. Триггер вновь изменил сигнал на своем выходе в момент появление высокого уровня синхросигнала. Между четвертым и пятым импульсами на входе C входы R и S снова задают режим установки, но триггер не меняет свое состояние, поскольку на входе C нет высокого логического уровня сигнала. В течение пятого синхроимпульса входы R и S определили режим сброса, и триггер переключился в низкий логический уровень, так как на входе C в данный момент времени действует высокий уровень сигнала.

Выход Qд. Первое переключение выходного состояния произошло в момент времени между вторым и третьим импульсами синхронизации. В этот момент входы R и S соответствовали режиму сброса, и, так как на входе C действовал низкий уровень сигнала, на выходе триггера установился лог. 0.

Выход Qе. Переключения триггера с данным типом синхронизации на временных диаграммах часто схожи с переключениями триггера со статической синхронизацией лог. 1 (сравните переключения выходов Qг и Qе в моменты времени первого и третьего импульсов синхросигнала). Однако, выход триггера с динамической синхронизацией по переднему фронту синхроимпульса переключается иначе в моменты времени пятого и шестого импульсов на входе C. Данная временная диаграмма показывает (длительность пятого импульса на

входе C), что изменения состояний управляющих входов R и S не влияют на состояния выхода Qе, если при этом на входе синхронизации нет переднего фронта импульса.

Выход Qж. Состояние входов R и S изменяет состояние выхода только в момент перехода сигнала синхронизации от высокого логического уровня к низкому.

C

t

R

t

S

t

Qг

t

Qд

t

Qе

Qж

t1 |

t2 |

t3 t4 |

t5 |

t6 t7 t8 t9 t10 t11 t12 |

t |

Рис. 1.4. Идеализированная временная диаграмма работы RS-триггеров с различными типами синхронизации

|

|

|

|

|

DD3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

С |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

DD1 |

|

|

|

DD2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

S |

|

|

|

|

|

|

S |

T |

Q |

|

|

|

S |

T |

Q |

|

|

Q |

|

|

|

S |

ТТ |

Q |

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||

C |

|

|

|

|

|

|

C |

|

|

|

|

|

C |

|

|

|

|

|

|

|

C |

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

R |

|

|

|

|

|

|

R |

|

|

Q |

|

|

|

R |

|

|

Q |

|

|

Q |

|

|

|

R |

|

|

Q |

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

б |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

С |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

S |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

QDD1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

|

QDD1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

Q |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

Q |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

t1 |

t2 |

|

|

t3 |

t4 |

|

|

|

t |

|

|||||||||||||||

в

Рис. 1.5. Логическая схема двухступенчатого RS-триггера (а), его условно-графическое обозначение (б) и

идеализированная временная диаграмма работы (в)

Выпускаются также двухступенчатые RS-триггер, построенные на основе двух одноступенчатых триггеров с прямой статической синхронизацией (см. рис. 1.5). Информация в первую ступень триггера DD1 заносится во время действия высокого уровня синхросигнала. После того как синхросигнал на входе принимает низкое значение, элемент DD1 переходит в режим хранения, а значение высокого сигнала на выходе инвертора DD3 обеспечивает запись состояния триггера DD1 в триггер DD2.

1.1.1.3.D-триггер

ВRS-триггерах для записи логического 0 и логической 1 требуются разные входы, что не всегда удобно. При записи и хранении данных один бит может принимать значение, как нуля, так и единицы. Для его передачи достаточно одного провода. Как мы уже видели ранее, сигналы установки и сброса триггера не могут появляться одновременно, поэтому можно объединить эти входы при помощи инвертора, как показано на рис. 1.6. Такой триггер получил название D- триггер. Название происходит от английского слова delay – задержка. Конкретное значение задержки определяется частотой следования импульсов синхронизации.

D |

S T |

|

D |

T |

C |

C |

Q |

Q |

|

|

C |

|

||

|

R |

Q |

Q |

|

|

|

|

|

|

|

а |

|

|

б |

Рис. 1.6. Логическая схема D-триггера (а) и его условно-графическое обозначение (б)

Таблица истинности D-триггера достаточно проста

C |

D |

Qt |

Qt+1 |

Функция |

|

0 |

х |

0 |

0 |

Режим |

|

|

|

|

|

хранения |

|

0 |

х |

1 |

1 |

||

информации |

|||||

|

|

|

|

||

|

|

|

|

|

|

1 |

0 |

х |

0 |

Режим записи |

|

1 |

1 |

х |

1 |

информации |

|

|

|

|

|

|

Как видно из этой таблицы, D-триггер способен запоминать по синхросигналу и хранить один бит информации.

Так как информация на выходе остается неизменной до прихода очередного импульса синхронизации, D-триггер называют также триггером с запоминанием информации или триггером-защелкой. Для снятия 32 бит информации с параллельной шины, берут 32 D-триггера и объединяют их входы синхронизации для управления записью информации, а 32 D-входа подсоединяют к шине.

При описании работы всех рассмотренных выше триггеров предполагалось, что сигнал на входе триггера может принимать только два состояния: логический 0 и логическая 1. Этот факт определялся тем, что в рассматриваемых случаях синхроимпульс приходил только тогда, когда сигналы на входе триггера имели установившиеся значения. Однако при работе реальных цифровых устройств синхроимпульс может прийти в любой момент времени, в том числе и в момент смены состояния сигнала на входе триггера.

Если синхросигнал попадет точно на момент перехода входным сигналом

порогового уровня, то триггер на некоторое время может попасть в неустойчивое метастабильное состояние, при котором напряжение на его выходе будет находиться между уровнем логического нуля и логической единицы. Это может привести к нарушению правильной работы цифрового устройства в целом.

Подобного недостатки лишен триггер с динамической синхронизацией, запоминающий входную информацию по фронту. Действительно, фронт сигнала синхронизации, в отличие от высокого (или низкого) потенциала, не может длиться продолжительное время. В идеале длительность фронта стремится к нулю. Поэтому в триггере, запоминающем входную информацию по фронту, неустойчивое метастабильное состояние исключено.

D-триггер, запоминающий входную информацию по фронту, может быть построен из двух триггеров, работающих по потенциалу. Схема такого триггера приведена на рис. 1.7, а. Сигнал синхронизации подается на эти триггеры в противофазе.

|

|

|

|

|

DD1 |

|

|

|

|

|

|

|

|

|

|

|

DD2 |

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D |

|

|

D |

|

|

T |

Q |

|

|

|

|

|

|

|

D |

T |

|

|

|

|

|

Q |

|

|

D |

ТТ |

Q |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

Q |

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

C |

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|||

|

|

|

|

|

Q |

|

|

|

|

|

|

|

|

Q |

|

|

Q |

|

|

|

|

Q |

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

|

|

|

|

|

|

|

|

|

|

б |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

QDD1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

С |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

Q |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

предыдущее |

новое |

t |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

состояние |

состояние |

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

в

Рис. 1.7. Логическая схема D-триггера работающего по фронту (а), его условное обозначение (б) и идеализированная временная

диаграмма работы (в)

Идеализированные временные диаграммы приведены на рис. 1.7, в. На них обозначение QDD1 соответствует сигналу на выходе триггера DD1. Так как на вход синхронизации триггера DD2 тактовый сигнал поступает через инвертор, то когда первый триггер находится в режиме хранения, второй триггер пропускает сигнал на выход схемы. И наоборот, когда первый триггер пропускает сигнал с входа схемы на свой выход, второй триггер находится в режиме хранения.

Сигнал на выходе всей схемы в целом не зависит от сигнала на входе D схемы. Если первый триггер пропускает сигнал данных со своего входа на выход, то второй триггер в это время находится в режиме хранения и поддерживает на выходе предыдущее значение сигнала, то есть сигнал на выходе схемы тоже не может измениться.

Таким образом, сигнал в рассматриваемой схеме запоминается только в момент изменения сигнала на синхронизирующем входе C с единичного потенциала на нулевой.

Динамические D-триггеры выпускаются в виде готовых микросхем или входят в виде блоков в состав больших интегральных схем, таких как базовый матричный кристалл (БМК) или программируемых логических интегральных схем (ПЛИС).

Условное обозначение D-триггера, запоминающего информацию по фронту тактового сигнала, приведено на рис. 1.7, б. То, что триггер запоминает входной сигнал по фронту, отображается на условном обозначении треугольником, изображенным на выводе входа синхронизации. То, что внутри этого триггера находится два триггера, отображается в среднем поле условно-графического изображения двойной буквой TТ.

1.1.1.4. JK-триггер

JK-триггер работает также как RS-триггер, с одним лишь исключением: при подаче логической 1 оба входа J и K состояние выхода триггера изменяется на противоположное. Таблица истинности имеет вид:

J |

K |

Qt+1 |

Функция |

||

|

|

|

|

|

|

0 |

0 |

Qt |

Хранение |

||

0 |

1 |

0 |

|

Установка в 0 |

|

|

|

|

|

|

|

1 |

0 |

1 |

|

Установка в 1 |

|

|

|

|

|

|

|

|

|

|

|

|

инвертирование |

|

|

|

|

|

|

1 |

1 |

Qt |

предыдущего |

||

|

|

|

|

|

состояния |

|

|

|

|

|

|

Вход J (от англ. Jump – прыжок) аналогичен входу S у RS-триггера, вход K (от англ. Kill – убить) аналогичен входу R. При подаче 1 на вход J и 0 на вход K выходное состояние триггера становится равным логической 1. А при подаче 1 на вход K и 0 на вход J выходное состояние триггера становиться равным логическому 0. JK-триггер в отличие от RS-триггера не имеет запрещенных состояний на основных входах, однако это никак не помогает при нарушении правил разработки логических схем. На практике применяются только синхронные JK-триггеры, то есть состояния основных входов J и K учитываются только в момент тактирования, например по положительному фронту импульса на входе синхронизации.

В качестве примера на рис. 1.8, а приведен один из вариантов логических схем JK-триггера.

|

& |

S T |

|

S T |

|

|

J |

|

Q |

Q |

Q |

||

|

|

|

||||

C |

|

C |

C |

|||

|

|

|

|

|||

K |

& |

R |

Q |

R |

Q |

Q |

|

|

|

|

|

а

S |

ТТ |

J |

Q |

|

|

C |

|

K |

Q |

|

|

R |

|

|

б |

Рис. 1.8. Логическая схема JK -триггера (а)

иего условное обозначение (б)

Впромышленно выпускающихся микросхемах триггеров обычно реализуются как входы J и K, так и входы R и S, что позволяет устанавливать триггер в заранее определенное исходное состояние.

1.1.1.5. T-триггер

Т-триггер – это триггер, логическое состояние выходного сигнала которого изменяется на противоположное по каждому такту синхроимпульса при условии наличия логической 1 на входе Т. Т-триггер часто называют счетным триггером. Он может строиться как на JK, так и на D-триггерах (рис. 1.9). Как можно видеть в таблице истинности JK-триггера (см. п.1.1.1.4), он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединяя входы J и К. Наличие в D-триггере динамического С входа также позволяет получить на его основе T-триггер. При этом вход D соединяется с инверсным выходом, а на вход С подаются счетные импульсы. В результате триггер при каждом счетном импульсе запоминает значение, т.е. будет переключаться в противоположное состояние.

J T |

|

D |

ТТ |

TT |

|

Q |

Q |

Q |

|

C |

|

C |

|

C |

K |

Q |

Q |

Q |

|

|

|

|

|

|

а |

|

|

б |

в |

Рис. 1.9. Логическая схема T-триггера, построенная на основе JK-триггера (а) и D-триггера (б) и его условно-графическое обозначение (в)

Временная диаграмма T-триггера, работающего по заднему фронту синхронизирующего сигнала приведена на рис. 1.10. Переключение выходного состояния триггера на противоположное происходит по заднему фронту каждого импульса на входе синхронизации.

C

t

Q

t

Q

t

Рис. 1.10. Идеализированная временная диаграмма работы T-триггера с переключением по заднему фронту синхросигнала

В цифровых электронных устройствах Т-триггер часто применяют для понижения частоты в 2 раза, при этом на Т вход подают единицу, а на С – сигнал с частотой, которая будет поделена. Кроме того, Т-триггеры используются при построении схем различных счетчиков. Поэтому Т-триггеры выпускаются промышленностью как в виде отдельных микросхем, так и включаются в состав больших интегральных схем (БИС) различного назначения.