- •1. Определение информации. Семиотика и ее составные части. Фазы обращения информации.

- •2. Структура системы связи. Основные задачи каждого блока системы связи.

- •3. Измерение информации. Дискретный источник информации. Мера информации по Хартли и ее свойство

- •4. Измерение информации по Шеннону.

- •5. Свойства информации по Шеннону.

- •6. Энтропия нескольких источников информации.

- •7. Энтропия непрерывного источника. Относительная энтропия.

- •8. Избыточность источника сообщений.

- •9. Взаимосвязь между энтропией и числом сообщений.

- •10. Пропускная способность двоичного канала.

- •11. Согласование характеристик сигнала и канала.

- •Амплитудная модуляция

- •12. Пропускная способность непрерывного канала с помехами.

- •13. Классификация методов преобразования непрерывной информации в дискретную форму.

- •14. Теорема дискретизации Котельникова в.А. И ее особенности.

- •Свойства ряда Котельникова:

- •15. Корреляционный критерий дискретизации.

- •16. Адаптивные методы дискретизации.

- •Нулевая степень воспроизводящей функции

- •Первая степень приближающего многочлена

- •17. Квантование по уровню. Шум квантования.

- •О терминах

- •Основные принципы построения цап с резистивными цепочками Первый вариант

- •19. Ацп поразрядного взвешивания. Ацп поразрядного уравновешивания на конденсаторах

- •Первый шаг

- •Быстродействие

- •20. Устройство выборки - хранения. Принцип действия и схемы увх

- •21. Распределение мощности в спектре периодического сигнала.

- •22. Спектр периодической последовательности прямоугольных импульсов. Пример.

- •23. Спектр одиночного прямоугольного импульса. Пример.

- •24.Теорема Парсеваля о распределении энергии в спектре непериодического сигнала.

- •25. Взаимосвязь между длительностью импульса и шириной его спектра.

- •26. Спектральная плотность мощности случайного процесса.

- •27. Цели кодирования. Эффективное кодирование. Методы эффективного

- •Цели изучения темы «Эффективное кодирование».

- •Задачи эффективного кодирования.

- •28. Техническая реализация кодирующего и декодирующего устройств эффективного кода.

- •29. Теорема Шеннона о пропускной способности канала без помех и

- •30. Теорема Шеннона о пропускной способности канала при наличии помех. Классификация помехоустойчивых кодов.

- •31. Общие принципы использования избыточности в блоковых кодах.

- •32. Групповой код. Математическое введение. Определение количества

- •33. Таблицы опознавателей и проверочные уравнения для различных кодов (7;4); (7;3); (8;2); (9;3).

- •34. Техническая реализация группового кода и его матричная запись.

- •35. Циклический код. Математическое введение. Выбор образующего многочлена по требуемой корректирующей способности кода.

- •36.Методы построения циклического кода.

- •6.4.1. Методом умножения

- •6.4.2. Методом деления

- •6.4.3. По методу группового кода

- •37. Техническая реализация кодирующих устройств циклического кода по методу умножения (примеры).

- •38. Техническая реализация кодирующих устройств циклического кода по методу деления (примеры).

- •39. Техническая реализация кодирующих устройств циклического кода по методу группового кода (примеры).

- •40. Техническая реализация декодирующих устройств циклического кода, исправляющих одиночную ошибку. Пример.

- •41. Техническая реализация декодирующих устройств циклического кода, исправляющего 2-ые смежные ошибки. Пример.

- •42. Рекуррентный код. Кодирующее и декодирующее устройства. Пример.

- •43.Итеративные коды. Код с повторениями.

- •Модифицированный код с повторением

40. Техническая реализация декодирующих устройств циклического кода, исправляющих одиночную ошибку. Пример.

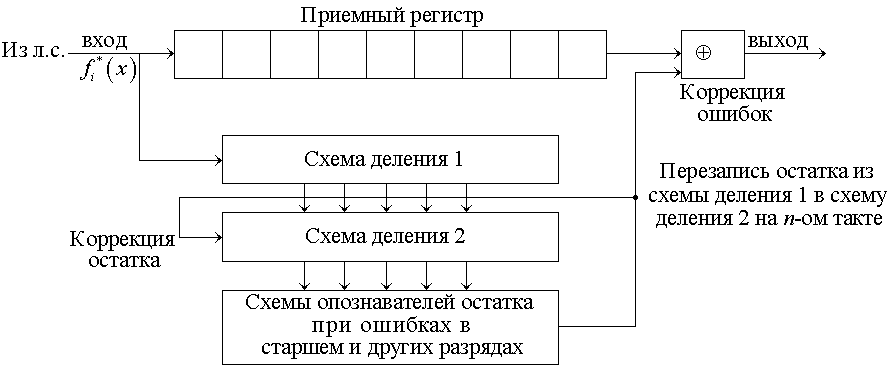

Нарисуем общую схему декодирующего устройства с двумя схемами деления.

Рис. 6.10. Схема декодирующего устройства с двумя схемами деления

Пусть имеет место ошибка в старшем разряде К.К., принятой из линии связи. Пока она доберется до выхода из приемного регистра, все n тактов она делится в схеме деления 1. На n-ном такте остаток переписывается в схему деления 2. На (n + 1) такте ошибка выходит из регистра и поступает на сумматор. Одновременно из схемы деления 2 кодовая комбинация, соответствующая ошибке в старшем разряде, поступает на схему опознавателя остатка ошибки в старшем разряде. Последняя вырабатывает сигнал на исправление ошибки и обнуление схемы деления 2, если других ошибок нет. Если же ошибка имеет место не в старшем разряде, то остаток, переписанный из схемы деления 1 в схему деления 2, продолжает делиться до тех пор, пока ошибка не доберется до выхода из регистра, то есть в обеих схемах деления 1 и 2 ошибка будет всегда делиться n раз.

Разберем конкретный пример.

Имеем: ai(x) = x3 Е 1 = 1001; g(x) = x3 Е x2 Е 1 = 1101.

Циклический код (7; 4), исправляющий одиночные ошибки.

ƒi(x) - послали в линию связи. Из линии связи получили ƒi*(x): 1101011. Необходимо построить схему Д.У., исправляющего одиночные ошибки.

Решение.

1. Выберем схему деления. Пусть это будет схема деления с первого такта.

Рис. 6.11

2. Определим

остаток, который получается в схеме

деления на n-ном

такте ( в нашем случае n

= 7), если имеет место ошибка в старшем

разряде, то есть

![]() .

Для этого поделим

.

Для этого поделим![]() наg(x):

наg(x):

Остаток на седьмом такте деления r7(x) = 100.

3. Спроектируем схему распознавания остатка. Минимальные затраты оборудования (считаются по числу входов-выходов) будут иметь место при инверсии «1» в «0» и установки схемы «исключающего или», когда при входе трех нулей на выходе берется инверсный выход, дающий «1», т.е.

Рис. 6.12

Для построения логических схем можно использовать схемы «И» с прямым и инверсным выходами и схемы «ИЛИ» с прямым и инверсным выходами.

4. Нарисуем схему декодирующего устройства с заведением обратной связи от сигнала коррекции ошибки на обнуление схемы деления 2.

Рис. 6.13

5. Приведем таблицу потактовой работы декодирующего устройства.

Таблица 6.6

|

№/№ тактов |

Вход |

Ячейки |

Выход |

Примечание 1 |

Примечание 2 | ||

|

x0 |

x1 |

x2 | |||||

|

1 |

1 |

1 |

0 |

1 |

– |

Идет заполнение приемного регистра и деление ƒi*(x) на g(x) в схеме деления 1 |

|

|

2 |

1 |

0 |

1 |

0 |

– | ||

|

3 |

0 |

0 |

0 |

1 |

– | ||

|

4 |

1 |

0 |

0 |

0 |

– | ||

|

5 |

0 |

0 |

0 |

0 |

– | ||

|

6 |

1 |

1 |

0 |

1 |

– | ||

|

7 |

1 |

0 |

1 |

0 |

– |

Переписывается r(x) в схему деления 2 | |

|

8 |

1 |

0 |

0 |

1 |

1 |

Соответствует r7(x) |

Входной сигнал из регистра начинает поступать на выход |

|

9 |

– |

0 |

0 |

0 |

1 Е 1 = 0 |

Идет сигнал коррекции | |

|

10 |

– |

0 |

0 |

0 |

0 |

Исправление шестого символа и сброс схемы деления 2 в ноль | |

|

11 |

– |

0 |

0 |

0 |

1 | ||

|

12 |

– |

0 |

0 |

0 |

0 | ||

|

13 |

– |

0 |

0 |

0 |

1 | ||

|

14 |

– |

0 |

0 |

0 |

1 | ||

На 9-том такте на первый сумматор в схеме деления 2 приходят две единицы: одна от обратной связи с x2 и вторая со схемы коррекции. Они дают «0» и все содержание схемы деления 2 превращается в «0». Однако, это не всегда так получается. Особенно, когда n ≠ 2m – 1 и обращение схемы деления 2 в «0» следует проектировать особо.