- •If (Interrupt Flag, бит 9) — флаг прерывания, определяющий реакцию процессора на запросы внешних прерываний по входу int (0 — прерывания запрещены, 1 — разрешены);

- •Способы адресации

- •Влияние команд на регистр флагов

- •Конвейерная обработка в процессоре Pentium

- •Развитие архитектуры Pentium

- •Расширенные регистры и типы данных процессоров x86

- •Дескрипторы

- •Порядок работы процессора в защищенном режиме

Развитие архитектуры Pentium

Микроархитектура P6

Процессоры Pentium Pro — Pentium III составляют семейство P6. Они имеют в своей основе микроархитектуру P6 (рис.).

Основные особенности микроархитектуры P6:

-

динамическое исполнение:

-

предсказание переходов;

-

динамический анализ потока данных через процессор для определения зависимостей и выяснения целесообразности внеочередного выполнения команд;

-

выполнение команд с опережением;

-

двухуровневый кэш: L1 — по 8 Кбайт для команд и данных; L2 — 256 Кбайт, 512 Кбайт или 1Мбайт;

-

64-разрядная шина между ядром процессора и кэшем L2;

-

12-стадийный конвейер.

В P6 впервые было введено переупорядочивание команд (out-of-order) для повышения производительности.

Рис. Микроархитектура P6

Видно, что элементы диаграммы соответствуют стадиям конвейера процессора Pentium, хотя процессоры P6 имеют 12-стадийный конвейер.

На стадии завершения (Retirement) происходит сохранение результатов и обновление состояния. Здесь результаты выполненных микроопераций обрабатываются так, что состояние процессора обновляется в соответствии с первоначальным порядком программы.

Микроархитектура Intel NetBurst

Процессор Pentium 4 имеет микроархитектуру Intel NetBurst (рис.).

Рис. Микроархитектура NetBurst

Основные черты микроархитектуры NetBurst:

-

20-стадийный гиперконвейер;

-

системная шина с частотой 400 МГц и пропускной способностью 3,2 Гбит/с;

-

кэш второго уровня — с улучшенной передачей данных (Advanced Transfer Cache, ATC);

-

кэш команд первого уровня — с отслеживанием выполнения команд (Execution Trace Cache);

-

блок быстрого исполнения команд (Rapid Execution Engine);

-

улучшенная технология динамического исполнения;

-

расширенный блок вычислений с плавающей запятой и обработки мультимедиа);

-

потоковые SIMD-расширения SSE2.

Системная шина Pentium 4 использует схему передачи сигналов, организованную на физическом уровне с использованием схем буферизации таким образом, что по 100-МГц шине передается 4-кратно увеличенный пакет данных, т. е. обеспечивается передача данных с частотой 400 МГц.

Максимальная производительность процессора Pentium 4 достигается при работе с двухканальной памятью типа RDRAM. Однако из-за ее дороговизны были выпущены чипсеты, обеспечивающие работу Pentium 4 с памятью SDRAM, а впоследствии — DDR.

Помимо кэш-памяти данных объемом 8 КБ, процессор Pentium 4 имеет кэш-память первого уровня с отслеживанием выполнения команд, которая хранит до 12 000 декодированных микроопераций в порядке их выполнения. Это увеличивает производительность за счет исключения декодера из основного исполнительного устройства и делает более эффективным использование кэш-памяти за счет уменьшения количества обменов данными между кэшем и основной памятью из-за наличия команд ветвления и возможности неправильного предсказания переходов. В результате удается передать больший объем команд в исполнительные блоки процессора и уменьшить общее время, требуемое на возврат из тех ветвлений, которые были неправильно предсказаны.

Блок быстрого исполнения команд (Rapid Execution Engine) включает два АЛУ процессора Pentium 4, которые работают с частотой, превышающей тактовую частоту процессора в 2 раза. Это позволяет выполнять основные целочисленные команды (сложение, вычитание, логическое И, логическое ИЛИ) с двойной тактовой частотой. Например, блок быстрого исполнения команд процессора Pentium 4 с тактовой частотой 1,5 ГГц работает с частотой 3 ГГц.

Кэш-память с улучшенной передачей данных (Advanced Transfer Cache, ATC) — это неблокируемая, полноскоростная кэш-память второго уровня с 8-канальной организацией. Для первого Pentium 4 она имеет объем 256 КБ. Канал данных между кэш-памятью второго уровня и ядром процессора имеет разрядность 256 бит (32 байта) и работает на частоте ядра процессора. В результате процессор Pentium 4 с тактовой частотой 1,5 ГГц может обеспечить скорость обмена данными с кэшем второго уровня 48 ГБ/с. Соответствующая скорость передачи данных для процессора Pentium III с тактовой частотой 1 ГГц равна 16 ГБ/с.

Блок улучшенного динамического исполнения команд состоит из отдельных блоков, отвечающих за выполнение команд. Процессор Pentium 4 может просматривать на лету 126 команд, осуществлять до 48 загрузок из конвейера и 24 размещений в конвейере. Он также имеет усовершенствованный алгоритм предсказания ветвлений, обеспечивающий уменьшение числа ложных предсказаний примерно на 33% по сравнению с аналогичным показателем процессоров поколения P6. Это осуществляется с помощью буфера ветвлений объемом 4 КБ, который хранит больше информации об истории ветвлений, имевших место ранее, а также более совершенного алгоритма предсказания ветвлений.

Потоковые SIMD-расширения SSE2 — это 144 новые команды MMX и SSE, включающие 128-разрядные целочисленные арифметические SIMD-операции и 128-разрядные SIMD-операции с плавающей точкой двойной точности. Эти новые команды уменьшают общее число команд, требуемых для выполнения конкретной программной задачи, в результате давая дополнительный выигрыш в производительности. Они ускоряют выполнение целого ряда приложений, включая приложения обработки видео, речи, изображений и фотоснимков, шифрования, а также финансовые, технические и научные приложения.

В Pentium 4 Prescott (2004) появились 13 новых инструкций SSE3.

Средства тестирования и мониторинга системы:

-

встроенный алгоритм самотестирования (Built-In Self Test, BIST), осуществляющий поиск ошибки в микрокоде и в больших логических матрицах, а также тестирование кэш-памяти команд, кэш-памяти данных, буферов ассоциативной трансляции (Translation Lookaside Buffers, TLB) и устройств постоянной памяти (ROM);

-

порт доступа к тестированию IEEE 1149.1 (Test Access Port, TAP);

-

внутренние счетчики, контролирующие работу процессора и осуществляющие подсчет событий;

-

мониторинг термического состояния, позволяющий получить реальную величину потребляемой энергии и конструировать более экономичные системные платы.

Технология Hyper-Threading

В Pentium 4 3,06 ГГц (Northwood, 2002 г.) появилась технология Hyper-Threading (HT).

Вначале HT была тесно связана с микроархитектурой NetBurst. В Core она отсутствовала, а в Intel (Nehalem) появилась вновь. Она позволяет одному процессору одновременно (параллельно) выполнять два различных потока управления (две нити — threads). Архитектурно процессор с HT представляет собой два логических процессора (рис.), каждый из которых имеет свое собственное архитектурное состояние (AS, Architectural State). AS — это значения регистров данных, сегментных, управляющих, отладочных и большинства машинно-специфичных регистров. Также каждый логический процессор имеет свой APIC (advanced programmable interrupt controller — улучшенный программируемый контроллер прерываний).

Рис. Сравнительная схема обычной двухпроцессорной системы

и системы на одном процессоре Pentium 4 с технологией HT

После включения питания и инициализации каждый логический процессор может быть отдельно остановлен, прерван или запущен для выполнения собственной нити независимо от других логических процессоров. Но в отличие от двухпроцессорной системы логические процессоры разделяют общие ресурсы ядра процессора, которые включают операционное устройство, кэш, устройство шинного интерфейса и др.

Это позволяет увеличить загрузку операционного устройства процессора и, соответственно, существенно уменьшить число циклов ожидания (простаивания) (рис.).

Рис. Иллюстрация повышения эффективности работы

операционного устройства благодаря HT

Элементарная прямоугольная ячейка на рисунке символизирует загрузку одного операционного ресурса в течение одного такта. Если ячейка закрашена, то ресурс загружен. Если нет, то простаивает. Один горизонтальный блок из трех ячеек соответствует одному такту. Три ячейки в одном горизонтальном блоке означают три операционных ресурса, работающих параллельно (один суперскалярный процессор может выполнять до трех команд за один такт). Циклы простаивания образуются по причине отсутствия необходимых данных в кэше, ошибочных предсказаний переходов, командных зависимостей в пределах каждой нити.

Технология HT в многозадачных приложениях дает повышение производительности до 25%. Величина прироста эффективности, конечно, зависит от того, как в приложении реализована многопоточность. Для реализации процессором возможностей технологии HT необходимо, чтобы HT поддерживали чипсет, BIOS и операционная система.

Микроархитектура Intel Core

Основные черты микроархитектуры Intel Core (рис.):

-

Wide Dynamic Execution (внеочередное исполнение микроопераций, до 4 команд за такт на ядро):

-

14-стадийный конвейер;

-

3 АЛУ;

-

4 декодера для декодирования до 5 команд за такт;

-

улучшенное предсказание переходов;

-

Advanced Smart Cache L2 размером до 4 Мбайт и 256-битной внутренней шиной;

-

SSE4.

Рис. Микроархитектура Intel Core

Процессоры с микроархитектурой Intel Core: Core 2 Duo, Core 2 Quad, Core 2 Extreme, Xeon.

Архитектура многоядерных процессоров

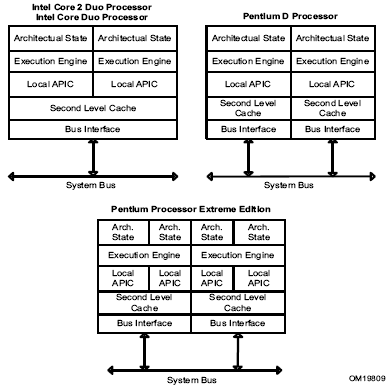

Двухядерные процессоры — Intel Core 2 Duo (рис.), Intel Core 2 Extreme, Pentium D, Pentium Extreme Edition, AMD Athlon 64 x2.

Рис. Архитектура двухядерных процессоров

Четырехядерные процессоры — Intel Core 2 Quad (рис.), четырехядерный Intel Xeon, четырехядерный AMD Opteron.

Рис. Архитектура четырехядерных процессоров

Существуют процессоры и с большим количеством ядер:

-

8 — Sun Niagara;

-

9 — STI (Sony-Toshiba-IBM) Cell;

-

80 — Intel Larrabee.

Микроархитектура Intel (Nehalem)

Микроархитектуру Intel (Nehalem) имеют процессоры Intel Core i7, Intel Core i5, Intel Core i3. Они производятся по технологическим нормам 45 и 32 нм.

Основные характеристики микроархитектуры Intel (Nehalem):

-

улучшенное предсказание переходов с защитой от неправильных предсказаний;

-

глубокая буферизация в конвейере с переупорядочиванием команд для лучшего распараллеливания кода;

-

интегрированный контролер памяти с масштабируемой пропускной способностью канала памяти;

-

новая иерархическая организация кэш-памяти;

-

двухуровневые TLB увеличенного размера;

-

быстрый невыровненный доступ к памяти;

-

HyperThreading Technology;

-

интегрированный микроконтроллер со встроенной оптимизированной программой управления энергопотреблением;

-

встроенные датчики температуры, тока и мощности;

-

интегрированный механизм включения-выключения ядер для регулирования энергопотребления.