- •If (Interrupt Flag, бит 9) — флаг прерывания, определяющий реакцию процессора на запросы внешних прерываний по входу int (0 — прерывания запрещены, 1 — разрешены);

- •Способы адресации

- •Влияние команд на регистр флагов

- •Конвейерная обработка в процессоре Pentium

- •Развитие архитектуры Pentium

- •Расширенные регистры и типы данных процессоров x86

- •Дескрипторы

- •Порядок работы процессора в защищенном режиме

Влияние команд на регистр флагов

Классификация команд по отношению к регистру флагов

По отношению к регистру флагов выделяются следующие группы команд:

-

Влияющие на флаги.

-

Проверяющие флаги (команды условных переходов, вызовов, возвратов, цикла).

-

Использующие флаги при выполнении действий в качестве операндов (команды сложения с переносом и т. п.).

-

Не имеющие отношения к регистру флагов.

Способы влияния команд на регистр флагов

Влияние команд на флаги бывает следующих типов:

-

В соответствии с результатом операции.

-

Установка (в единицу).

-

Сброс (установка в ноль).

-

Восстановление предыдущих значений, например, IRET.

-

Неопределенное.

Правила определения влияния команды на флаги

Основные правила определения влияния команды на флаги таковы:

-

Не влияют на регистр флагов команды передачи данных и передачи управления.

-

Команды арифметических и логических операций влияют на регистр флагов.

Из этих правил имеются исключения. Они определяются назначением (спецификой) команд и вполне очевидны. Это, например, команды SAHF и POPF.

Среди команд управления процессором имеются такие, которые не влияют на регистр флагов, например, HLT, и такие, которые влияют на него в соответствии со своим назначением, например, STI.

РАЗВИТИЕ АРХИТЕКТУРЫ x86. IA-32 и INTEL 64

Архитектура процессора Pentium

Процессоры архитектуры x86, IA-32, Intel64

Процессоры, являющиеся развитием i8086: i80286, i80386, i486, Pentium, Core2, Core i7 (i5, i3) — относятся к семейству архитектуры x86. 32-разрядные процессоры этого семейства (начиная с i80386) составляют подсемейство архитектуры IA-32. 64-разрядное расширение, которое появилось в поздних моделях Pentium 4 относит данные процессоры к подсемейству Intel64. Рассмотрим основные особенности архитектуры процессоров семейств x86 IA-32 и Intel64.

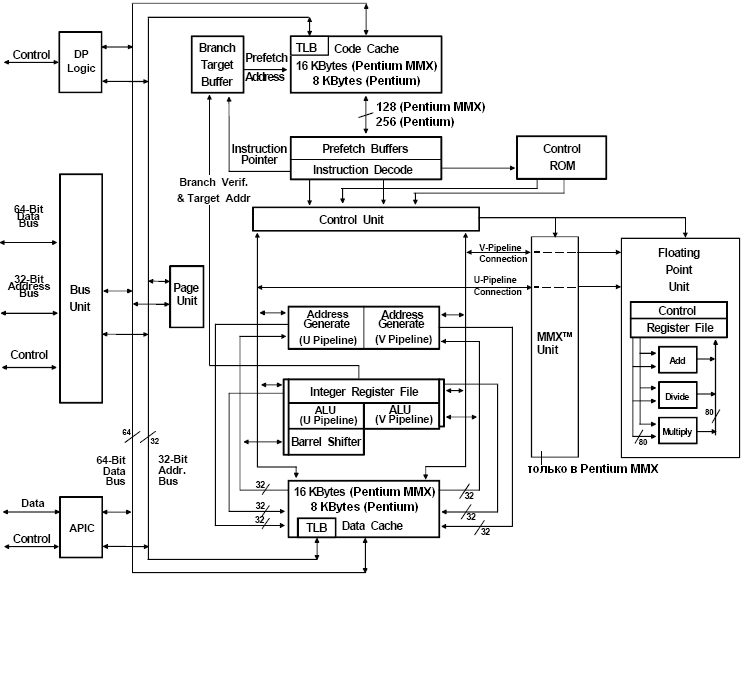

Структурная схема процессора Pentium

На рис. изображена структурная схема процессора Pentium.

Рис. Структурная схема процессора Pentium

Здесь DP Logic — Dual Processing Logic, логика двухпроцессорной обработки. При этом оба процессора работают с одинаковым уровнем приоритета (симметрично), разделяя кэш второго уровня.

Примечания:

-

Кэш команд и кэш данных для процессора Pentium (75/90/100/120/133/150/166/200) имеют размер 8 Кбайт каждый.

-

Устройство MMX имеется только в процессоре Pentium с технологией MMX™.

-

Внутренняя шина команд процессора Pentium (75/90/100/120/133/150/166/200) имеет ширину 256 бит.

Особенности архитектуры процессора Pentium

Процессор Pentium поддерживает все особенности архитектуры предшествующих процессоров фирмы Intel и имеет новые важные характеристики. В их число входят:

-

суперскалярная архитектура (Superscalar Architecture);

-

динамическое предсказание переходов (Dynamic Branch Prediction);

-

конвейеризованное устройство с плавающей точкой (Pipelined Floating-Point Unit);

-

улучшенное выполнение команд (Improved Instruction Execution Time);

-

раздельный кэш для кода и данных (Separate Code and Data Caches);

-

протокол обратной записи для кэша данных MESI (Modified, Exclusive, Shared, Invalid) (Writeback MESI Protocol in the Data Cache);

-

64-разрядная шина данных (64-Bit Data Bus);

-

конвейеризация цикла шины (Bus Cycle Pipelining);

-

контроль по четности адреса (Address Parity);

-

внутренний контроль по четности (Internal Parity Checking);

-

проверка на основе функциональной избыточности (Functional Redundancy Checking and Lock Step operation) (не поддерживается Pentium MMX);

-

отслеживание исполнения команд (Execution Tracing);

-

контроль производительности (Performance Monitoring);

-

тестирование и отладка в соответствии со стандартом IEEE 1149.1 (IEEE 1149.1 Boundary Scan);

-

режим управления системой (System Management Mode);

-

расширения виртуального режима 8086 (Virtual Mode Extensions);

-

возможность модернизации процессором Pentium OverDrive (Upgradable with a Pentium OverDrive processor);

-

поддержка двухпроцессорной системы (Dual processing support);

-

расширенное управление питанием (Advanced SL Power Management Features);

-

раздельное управление шиной (Fractional Bus Operation);

-

встроенный контроллер прерываний (APIC, Advanced Programmable Interrupt Controller).

Особенности архитектуры процессора Pentium MMX

В дополнение к свойствам процессора Pentium процессор Pentium MMX имеет следующие характеристики:

-

поддержка технологии MMX (Intel MMX (MultiMedia eXtensions) technology);

-

двойное напряжение питания (VCC2 (core) and VCC3 (I/O));

-

раздельный 4-проходной ассоциативный кэш кода и данных, каждый с улучшенным полностью ассоциативным буфером трансляции адресов (TLB, Translation Lookaside Buffer) (Separate 16 Kbyte 4-way set-associative code and data caches, each with improved fully associative TLBs);

-

четыре 16-байтных буфера предвыборки;

-

расширенный алгоритм предсказания переходов (Enhanced branch prediction algorithm);

-

дополнительная стадия конвейера, стадия выборки, между стадиями предвыборки и декодирования команды (New Fetch pipeline stage between Prefetch and Instruction Decode).

Некоторые свойства процессора Pentium не поддерживаются процессором Pentium MMX. Это, например, проверка на основе функциональной избыточности и управление шагом блокировки.

Характеристика архитектурных особенностей Pentium и Pentium MMX

Устройство управления памятью (MMU , Memory Management Unit) процессора Pentium полностью совместимо с устройством управления памятью процессоров i80386 и i486.

Состав команд Pentium MMX включает 57 новых команд и 4 новых типа данных для увеличения производительности мультимедийного и коммуникационного программного обеспечения. Технология MMX основана на технике SIMD (Single Instruction, Multiple Data — одиночная команда, множественные данные).

Два конвейера команд (u-pipe и v-pipe) и устройство с плавающей точкой способны работать независимо. Каждый конвейер обычно выполняет команду за один такт. Таким образом, процессор способен выполнять за один такт две целочисленные команды и одну команду с плавающей точкой (при некоторых условиях — две). U-конвейер может выполнять все команды целочисленной арифметики и арифметики с плавающей точкой. V-конвейер — простые команды целочисленной арифметики и команду арифметики с плавающей точкой FXCH.

Для поддержки предсказания переходов в процессоре имеется два буфера предвыборки. Один осуществляет предвыборку в линейном режиме, другой — в соответствии с буфером флагов переходов (BTB, Branch Target Buffer). Таким образом, почти всегда нужный код предварительно выбран перед тем, как возникает необходимость его выполнения. В Pentium MMX алгоритм предсказания переходов улучшен для увеличения точности предсказания.

Процессоры Pentium и Pentium MMX имеют раздельный кэш первого уровня (L1) — кэш данных и кэш кода, что является признаком Гарвардской архитектуры. Кэш L1 процессора Pentium —двухпроходной частично ассоциативный (2-way set-associative), размером по 8 килобайт для команд и данных, Pentium MMX —- четырехпроходной (4-way set-associative), размером по 16 килобайт для команд и данных. Каждый кэш имеет выделенный буфер трансляции адресов (TLB , Translation Lookaside Buffer) для перевода линейных адресов в физические.

Кэш данных соответствует протоколу MESI (Modified, Exclusive, Shared, Invalid). Он может быть сконфигурирован как кэш с обратной записью (writeback) или со сквозной записью (writethrough) на line-by-line основе. Кэш данных имеет два порта — по одному на каждый конвейер. Тэги кэша данных имеют три порта для поддержки передачи данных двум конвейерам и одновременно цикла запроса в одном такте.

Кэш кода защищен от записи. Его тэги также имеют три порта для поддержки snooping и split-line доступов (Pentium MMX не поддерживает split-line доступа к кэшу кода, соответственно его кэш кода имеет два порта). Отдельные страницы могут быть сконфигурированы как кэшируемые или некэшируемые аппаратно или программно. Также могут быть разрешены или запрещены аппаратно или программно кэши в целом.

Кэш кода, буфер предсказания переходов и буфер предвыборки вместе отвечают за доставку последовательности команд исполнительным устройствам. Команды выбираются из кэша кода или поступают с внешней шины. Адреса переходов запоминаются в BTB. Устройство декодирования содержит два параллельных декодера, которые декодируют и посылают команды в исполнительный конвейер.

Режим кэширования определяется двумя битами CD (Cache Disable) и NW (Not Writethrough) управляющего регистра CR0.

Управляющее ПЗУ (Control ROM) содержит микрокод, контролирующий последовательность операций, выполняемых процессором.

Управляющее устройство (Control Unit) осуществляет прямое управление обоими конвейерами.

Pentium имеет 64-разрядную шину данных. Поддерживаются пакетные циклы чтения и обратной записи. Дополнительно к этому конвейеризация циклов шины позволяет выполняться одновременно двум циклам.

В процессоре Pentium существенно расширены средства повышения надежности — проверки целостности данных и обнаружения ошибок. Проверка четности данных поддерживается на уровне байтов. Добавлены контроль по четности адреса и внутренний контроль по четности наряду с новым исключением — исключением машинного контроля (machine check exception).

Pentium реализует контроль на основе функциональной избыточности (functional redundancy checking) для повышения надежности обнаружения ошибок процессора и его интерфейса. Когда используется контроль на основе функциональной избыточности, второй процессор, “контролер”, используется для выполнения в шаге блокировки (lock step) с главным процессором. Контролер осуществляет выборку значений с выходов главного процессора и сравнивает их со значениями, рассчитанными им самим. В случае несоответствия он вырабатывает сигнал ошибки. Pentium MMX контроль функциональной избыточности не поддерживает.

Поскольку количество функций, выполняемых процессором, растет, то растет и сложность тестирования. Pentium повышает возможности тестирования и отладки, реализуя IEEE Boundary Scan (Standard 1149.1).

Режим управления системой реализован в соответствии с расширениями архитектуры SMM (System Management Mode).

Сделаны расширения режима Virtual 8086 для повышения производительности путем уменьшения времени выполнения ловушки (trap) монитора этого режима.

Pentium имеет средства реализации многопроцессорных систем — расширенный контроллер прерываний (APIC, Advanced Programmable Interrupt Controller). Он реализует управление многопроцессорным прерыванием (multiprocessor interrupt management) с симметричным распределением прерываний по всем процессорам, поддержку подсистемы множественного ввода-вывода и поддержку межпроцессорного прерывания. APIC совместим с 8259А.