Лаб шифратори дешифратори

.pdfМіністерство Освіти і науки України Технічний коледж НУ «Львівська політехніка»

Циклова комісія

«Інформаційні технології»

Лабораторна робота

Дослідження роботи шифраторів і дешифраторів в програмі

EWB.

Схвалено на засіданні циклової комісії

«Інформаційні технології»

28.08.09 р.

Львів 2009

1

2

Мета роботи: ознайомлення з принципами роботи комбінаційних логічних схем, дослідження впливу керуючих сигналів на роботу комбінаційних логічних схем, реалізація і дослідження функціональних модулів на основі комбінаційних логічних схем.

Теоретична частина.

Дешифратори і шифратори по суті належать до перетворювачів коду. З поняттям шифрації пов'язано уявлення про стискання даних, з поняттям дешифрування - зворотне перетворення.

Комбінаційна схема, що перетворює код, який поступає на входи, в сигнал лише на одному з її виходів, називається дешифратором.

В умовних позначеннях дешифраторів і шифраторів використовуються букви DC і CD (від слів decoder і coder відповідно).

Якщо кількість двійкових розрядів коди, що дешифрується, позначити через n то кількість виходів дешифратора має бути 2n.У зв’язку із тим, що за допомогою n-розрядного двійкового коду можна відображувати 2n кодових комбінацій, кількість виходів повного дешифратора дорівнює 2n. Таким чином, дешифратор містить кількість виходів, що дорівнює кількості комбінацій вхідних змінних, наприклад, кількість входів дорівнює 3, то кількість виходів дорівнює 23=8.

Якщо частина вхідних наборів не використовується, то дешифратор називають неповним і у нього Nвих<2n. В ЕОМ за допомогою дешифраторів здійснюється вибірка необхідних комірок запам’ятовуючих пристроїв, розшифровка кодів операцій з видачею відповідних керуючих сигналів тощо.

Якщо вхідні змінні представити в якості двійкової системи запису чисел, то логічна одиниця формується в тому виході, номер якого відповідає десятковому запису того самого числа. Наприклад, A = 1, B = 0, C = 0, D = 1, число 1001 в двійковому коді. У десятковій коді це число відповідає 9, тобто при даній комбінації вхідних змінних F9 = 1. Дешифратори широко використовуються як перетворювачі двійкового коду у десятковий, а також в багатьох інших пристроях.

Функціонування дешифратора описується системою логічних рівнянь складених на основі таблиці істинності.

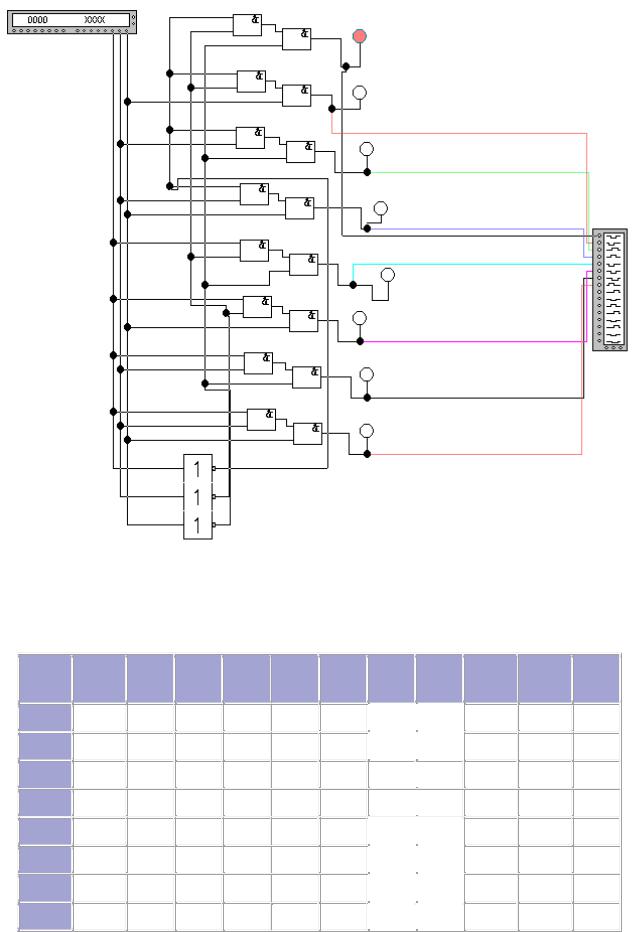

Одноступінчатий дешифратор(лінійний) - найбільш швидкодіючий, але його реалізація при значній розрядності вхідного слова є утрудненою, оскільки вимагає вживання логічних елементів з великою кількістю входів (яка дорівнює n+1 для варіантів із стробуванням по виходу) і супроводжується великим навантаженням на джерела вхідних сигналів. Зазвичай одноступінчатими виконуються дешифратори на невелику кількість входів, яка визначається можливостями елементів використаної серії мікросхем (див. малюнок 1).

3

Мал. 1 Приклад, кількість входів дорівнює 3, кількість виходів дорівнює 23=8.

Побудова дешифратора на основі простих елементів, за допомогою таблиці істинності (див. таблицю №1) і складених відповідно логічних рівнянь.

Таблиця № 1 Таблиця істинності

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

A |

0 |

0

0

0

1

1

1

1

B |

0

0

1

1

0

0

1

1

C |

0 |

1

0

1

0

1

0

1

Y1 |

Y2 |

Y3 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Y4 |

Y5 |

0 |

0 |

|

|

0 |

0 |

|

|

0

0

0

1

0

0

0 |

1 |

|

|

|

|

0 |

0 |

|

|

0 |

0 |

|

|

0 |

0 |

|

|

Y6 |

Y7 |

Y8 |

0 |

0 |

0 |

0 0 0

0 0 0

0 0 0

0 0 0

1 0 0

0 1 0

0 0 1

На малюнку №2. приведена часова діаграма роботи дешифратора.

4

Мал. 2

Поява малорозрядних дешифраторів (пірамідальний і матричний) у вигляді СІС поставила питання про використання їх як засобів побудови дешифраторів більшої розрядності, що дає істотну економію апаратурних витрат.

Будь-який потрібний дешифратор може бути побудований за пірамідальною структурою. При вході слово ділиться на поля, розрядність яких відповідає кількості входів наявних дешифраторів СІС, а потім з СІС будується пірамідальна структура, що становить сукупність лінійних дешифраторів.

Матричні дешифратори формуються на основі простих лінійних дешифраторів меншої розмірності, тобто будуються у вигляді матриці.

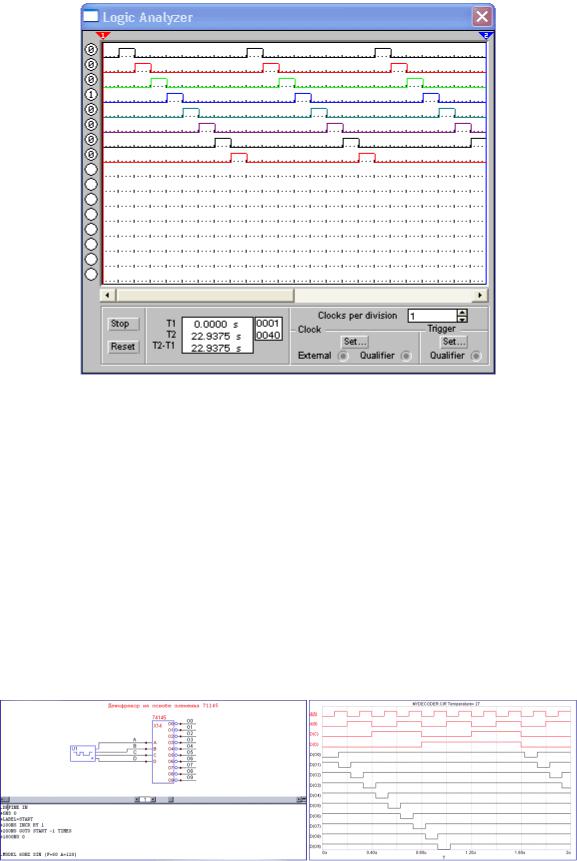

На малюнку №3 представлена схема дешифратора зібрана на елементі (мікросхемі) №71145, яка використовується для побудови складніших схем. Дешифратор приведений нижче працює з негативною логікою (див. малюнок №4).

Мал. 3 |

Мал. 4 |

Шифратори. Двійкові шифратори перетворюють код “1з N” у двійковий код, тобто виконують мікрооперацію, зворотну мікрооперації дешифраторів.

5

При збудженні одного з вхідних кіл шифратора на його виходах формується слово, що відображує номер збудженого кола.

Повний двійковий шифратор має 2n входів і n виходів. Одне з основних використань шифратора - введення даних з клавіатури, при якому натиснення клавіші з десятковою цифрою повинно приводити до передачі в пристрій двійкового коду даної цифри. Приклад побудови шифратора (див. малюнок №5), на малюнку №6 приведена тимчасова діаграма роботи шифратора.

Мал. 5 |

Мал. 6 |

Хід роботи

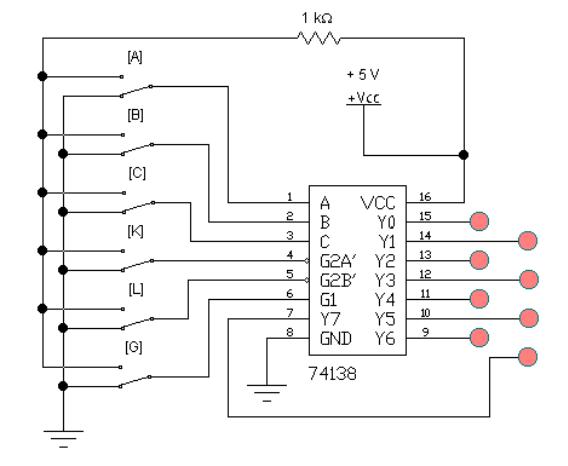

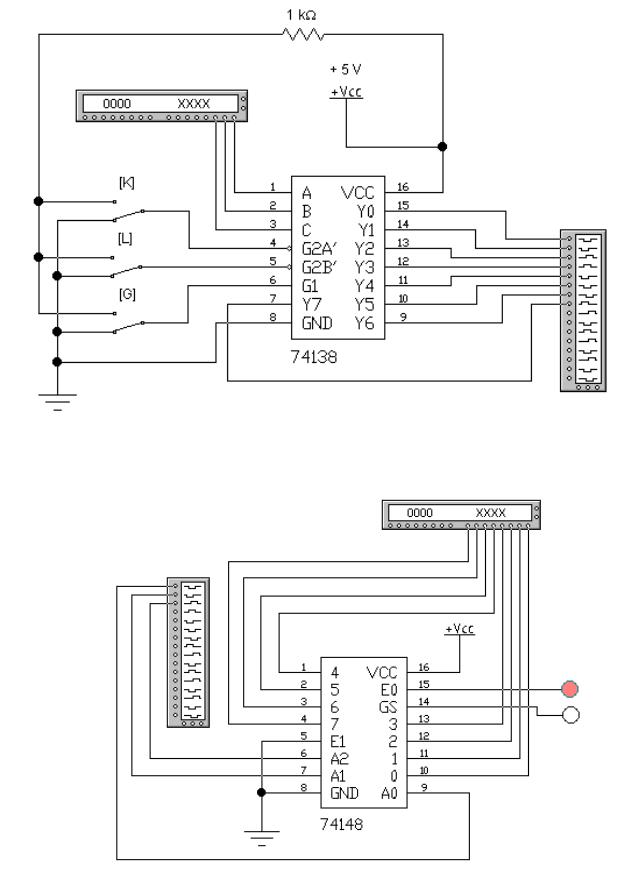

Зібрати схему відповідно до малюнка 1. У схему включені: логічні пробники, джерело постійної напруги + 5 В, двопозиційні перемикачі, резистор 1 кОм, і мікросхема 74138 (дешифратор 3х8).

Дослідження принципу роботи дешифратора 3х8 в основному режимі.

Зібрати схему, зображену на мал. 7. Подати на керуючі входи G2A’, G2B’, G1 рівень логічного нуля. Визначити і записати рівні сигналів на виходах Y0...Y7 у таблицю істинності при G = 0 (таблиця 1). Подати на вхід G рівень логічної одиниці. Подаючи всі можливі комбінації рівнів логічних сигналів на входи А, В, С за допомогою однойменних ключів, визначити за допомогою логічних пробників рівні логічних сигналів на виході схеми. Заповнити таблицю істинності дешифратора при G=1 (таблиця 1)

6

Таблиця 1 — Таблиця істинності дешифратора 3х8

Керування |

|

Входи |

|

|

|

|

Виходи |

|

|

|

|||||

G2A’ |

G2B’ |

G1 |

C |

|

B |

|

A |

Y0 |

Y1 |

Y2 |

Y3 |

Y4 |

Y5 |

Y6 |

Y7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Керування |

|

Входи |

|

|

|

|

Виходи |

|

|

|

|||||

G2A’ |

G2B’ |

G1 |

C |

|

B |

|

A |

Y0 |

Y1 |

Y2 |

Y3 |

Y4 |

Y5 |

Y6 |

Y7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Мал. 7 — Дешифратор 3х8

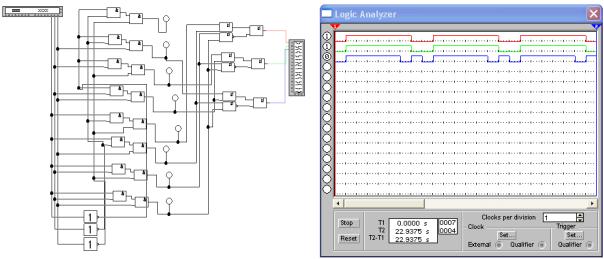

Дослідження роботи дешифратора за допомогою логічного аналізатора.

Мікросхема КМ555ИВ1 — пріоритетний шифратор, який приймає напругу низького рівня на один з восьми паралельних адресних входів 11—18. На виходах А0—А2 з’являється двійковий код, пропорційний номеру входу, що

7

став активним. Пріоритет у тому випадку, якщо декілька входів отримали активні рівні, буде мати старший серед них за номером. Вищий пріоритет у входу 18.

Мікросхема має дев’ятий, дозволяючий вхід Е1. Він дозволяє зробити всі входи 11—18 неактивними за відношенням до сигнальних рівнів. Для цього на вхід Е1 слід подати напругу заборони високого рівня. Таким чином можна відключити виходи шифратора і змінити вхідну інформацію. Мікросхема КМ555ИВ1 має два додаткових виходи (груповий сигнал) и Е0 (дозвіл від виходу). На виході з’явиться напруга низького рівня, якщо хоча б на одному з трьох сигнальних виходів А0—А2 присутня напруга низького рівня. По-другому, низький рівень на виході відображує наявність низького рівня на одному з виходів. На виході Е0 з’явиться напруга низького рівня, якщо на всіх входах — високі рівні. Використовуючи сумісно вихід Е0 и Е1, можна будувати багаторозрядні пріоритетні шифратори.

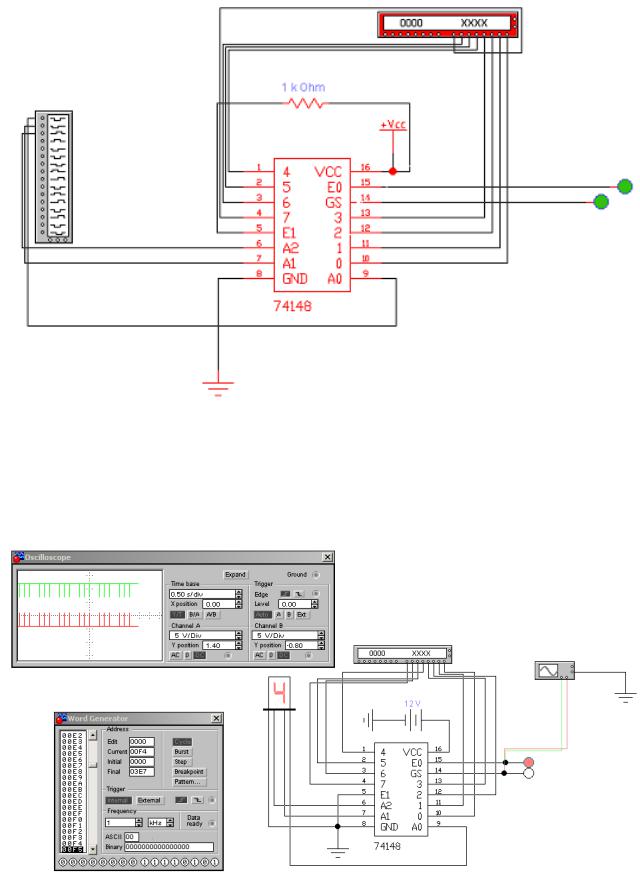

Зібрати схему, приведену на мал. 3. Включити схему. За допомогою відповідних ключів встановити стан керуючих входів G1=1, G2A=G2B=0. Подаючи слова від генератора слів, отримати тимчасові діаграми роботи дешифратора на екрані логічного аналізатора.

Дослідження роботи шифратора

Зібрати схему, приведену на мал. 9. У генератор слів по адресах від 0 до 8 записати слова відповідні одиничному коду на виходах (11111111, 11111110, ..., 00000000). Встановити генератор слів в режим «Цикл» і встановити частоту виведення слів 1 Гц. Встановити на логічному аналізаторі частоту опиту 2 Гц. Включити схему. За отриманими тимчасовими діаграмами заповнити таблицю істинності шифратора (таблиця 3). Призначення виводів ІМС 74148: 0...7 — входи; А0, A1, A2 — виходи; E1 — вхід дозволу; Е0, GS — виходи для каскадуючих шифраторів. При моделюванні слід врахувати, що всі входи і виходи шифратора 74148 інверсні (на функціональній схемі ІМС в програмі EWB вони помилково показані прямими).

Таблиця 3— Таблиці істинності шифратора

Дозвіл |

|

|

|

Входи |

|

|

Виходи |

|

Каскад |

|||||

E1 |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

A2 |

A1 |

|

A0 |

GS |

E0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

8

Мал. 8— Дослідження роботи дешифратора за допомогою логічного аналізатора.

Мал. 9 — Дослідження роботи шифратора за допомогою логічного аналізатора (на вході дозволу E1 логічний 0)

9

Мал. 10 — Дослідження роботи шифратора за допомогою логічного аналізатора (на вході дозволу E1 логічна одиниця)

Зібрати схему, відображену на мал.11. шляхом набору значень у генераторі слів, відобразити послідовно значення на цифровому індикаторі від 0 до 9 згідно порядкових номерів за журналом – 1-10, 11-20, 21-30 – 1 … 0

мал. 11. Дослідження роботи шифратора за допомогою осцилографа та цифрового індикатора

10