Электроника Коллектив кафедры Электроника, БГУИР 2014 (Мет пособие)

.pdf

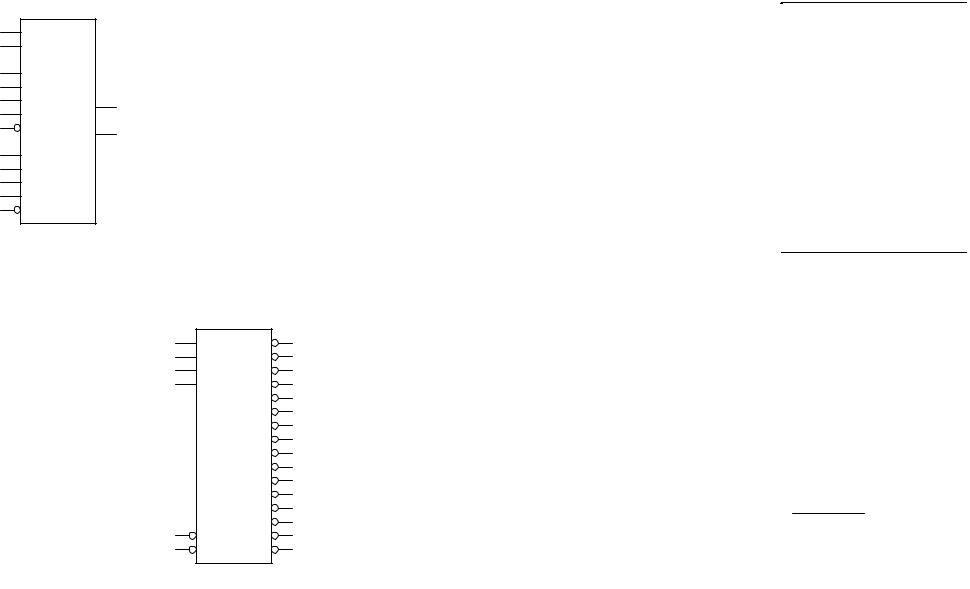

IN74AC153/IN74ACT153/IN74HC153A/IN74HCT153A (1554КП2/1594КП2/1564КП2/5564КП2)

Таблица истинности

|

|

|

Входы |

|

Выход |

|

|

|

A1 |

A0 |

Y |

EN |

|||||

1 |

|

X |

X |

0 |

|

0 |

|

0 |

0 |

D0 |

|

0 |

|

0 |

1 |

D1 |

|

0 |

|

1 |

0 |

D2 |

|

0 |

|

1 |

1 |

D3 |

|

16 – питание; 8 – общий.

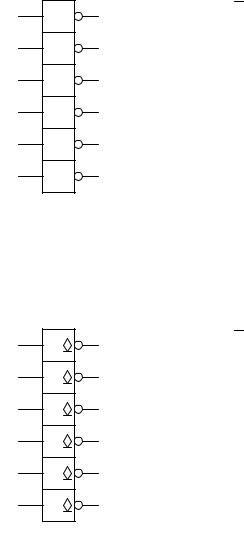

Рисунок В.20 – Два селектора-мультиплексора 4-1 со стробированием

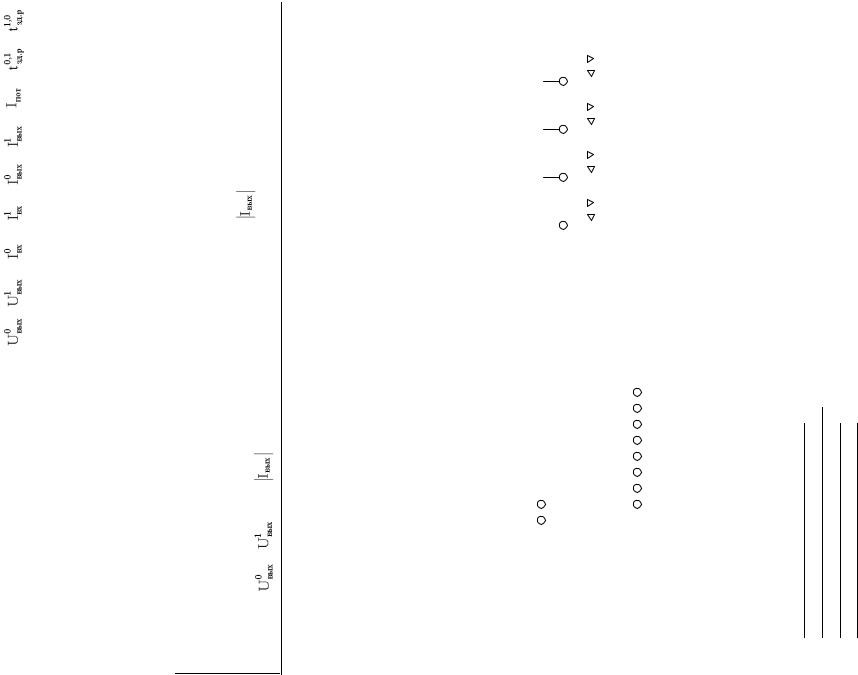

IN74HC154A (1564ИД3)

24 – питание; 12 – GND.

Рисунок В.21 – Дешифратор-демультиплексор 4-16 с инверсией на выходе

68

Таблица 3.4 Таблица переходов и возбуждения памяти автомата

S |

R |

Q0 |

Q1/D |

Режимы работы автома- |

|

|

|

|

|

та |

|

0 |

0 |

0 |

0 |

Режим хранения |

|

|

|

|

|

||

0 |

0 |

1 |

1 |

||

|

|||||

|

|

|

|

|

|

0 |

1 |

0 |

0 |

Режим установки |

|

0 |

1 |

1 |

0 |

в состояние 0 |

|

|

|

|

|

|

|

1 |

0 |

0 |

1 |

Режим установки |

|

1 |

0 |

1 |

1 |

в состояние 1 |

|

|

|

|

|

|

|

1 |

1 |

0 |

Х |

Запрещенный режим |

|

|

|

|

|

||

1 |

1 |

1 |

Х |

||

|

|||||

|

|

|

|

|

Примечание. Комбинация входных сигналов S = R = 1 в таблице является запрещенной, поскольку возникает неопределенность в выборе выходного состояния Х = 0 \/ 1.

4-й шаг – выходная цепь синтезируемого автомата не связана с его комбинационной схемой, что является особенностью автоматов Мура. Следовательно, можно констатировать, что Q1 = D, и записать так

называемое характеристическое уравнение автомата, в котором выходные сигналы условно представлены как логические переменные:

|

_ _ |

_ _ |

_ |

|

Q1 = S RQ0 \/ S R Q0 \/ S RQ0. |

(3.1) |

|||

Минимизируем выражение (3.1) и преобразуем его, используя |

||||

правило де Моргана, в базис ИЛИ-НЕ: |

|

|||

_ |

_ _ |

|

_____ |

|

Q1 = RQ0 \/ SR = R(Q0 \/ S) = R \/ (Q0 \/ S). |

(3.2) |

|||

5-й шаг – строим по логическому выражению (3.2) комбинационную схему автомата и пристраиваем к ней память автомата ЛЗ (см. рисунок 3.5).

41

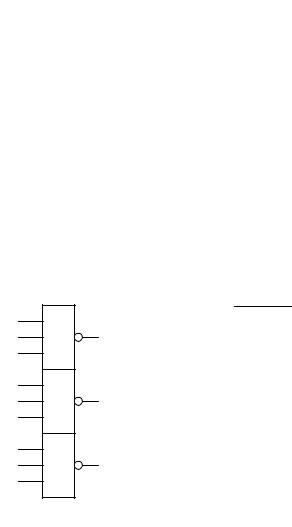

Рисунок 3.5 Схема автомата на |

Рисунок 3.6 Схема автомата на |

идеальных логических элементах |

реальных логических элементах |

В этой схеме считается, что логические элементы идеальны и срабатывают мгновенно. Однако реальные логические элементы всегда работают с некоторой задержкой. Можно (и нужно) учесть это обстоятельство и возложить функции элемента памяти на задержки внутри логических схем. Тогда надобность в дискретной (отдельной) линии задержки отпадает. Схема созданного автомата с учетом внутрисхемных задержек показана на рисунке 3.6. Нетрудно заметить, что созданный автомат есть не что иное, как обычный RS-триггер. Важно понимать, что приведенная методика синтеза позволяет создавать и более сложные цифровые автоматы.

Задача 5

Изучите микросхему КЦУ схемотехники КМОП, заданную в таблице 12.

Таблица 12 – Исходные данные к задаче 5

Номер |

Условное обозначение ИМС |

|

Код на |

Номер |

|

варианта |

международное |

прототип |

|

входах |

выхода |

|

Дешифраторы |

-демультиплексоры |

|

|

|

1 |

IN74AC137N |

ЭКР1554ИД7 |

|

100 |

Y3 |

2 |

IN74HC154AN |

ЭКР1564ИД3 |

|

1011 |

Y7 |

3 |

IN74ACT139N |

ЭКР1594ИД14 |

|

01 |

Y3 |

4 |

IN74HCT138AN |

ЭКР5564ИД7 |

|

110 |

Y4 |

5 |

IN74HC139AN |

ЭКР1564ИД14 |

|

10 |

Y1 |

Мультиплексоры

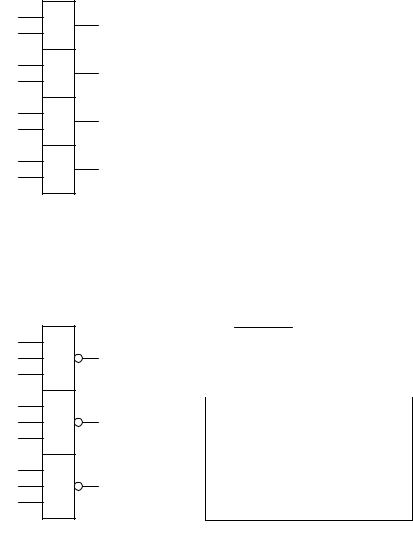

IN74AC139/IN74ACT139/IN74HC139A/IN74HCT139A (1554ИД14/1594ИД14/1564ИД14/5564ИД14)

2 |

|

|

|

|

4 |

Таблица истинности |

|

|

|||||||

|

A0a |

DC Y0a |

|

|

|

||||||||||

3 |

|

|

5 |

|

|

|

|

|

|

|

|

|

|

||

|

A1a |

Y1a |

|

|

|

|

|

|

|

|

|

|

|||

1 |

|

6 |

|

|

|

Входы |

|

Выходы |

|

||||||

|

CSa |

Y2a |

|

|

|

|

|

||||||||

|

|

|

7 |

|

|

|

|

A1 |

A0 |

Y0 |

Y1 |

Y2 |

Y3 |

||

|

|

|

Y3a |

|

|

|

CS |

|

|||||||

|

|

|

|

||||||||||||

14 |

|

A0b |

Y0b |

12 |

|

1 |

|

X |

X |

1 |

1 |

1 |

1 |

||

|

|

0 |

|

0 |

0 |

0 |

1 |

1 |

1 |

||||||

|

|

||||||||||||||

13 |

|

A1b |

Y1b |

11 |

|

|

|

|

|

|

|

|

|

||

|

|

0 |

|

0 |

1 |

1 |

0 |

1 |

1 |

||||||

|

|

||||||||||||||

15 |

|

CSb |

Y2b |

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

1 |

0 |

1 |

1 |

0 |

1 |

||||||

|

|

|

Y3b |

9 |

|

|

|||||||||

|

|

|

|

|

|

0 |

|

1 |

1 |

1 |

1 |

1 |

0 |

||

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

||||||||

16 – питание; 8 – общий.

Рисунок В.18 – Два дешифратора-демультиплексора 2-4 с инверсией на выходе

IN74AC151/IN74ACT151/IN74HC151A/IN74HCT151A (1554КП7/1594КП7/1564КП7/5564КП7)

|

|

|

|

|

|

|

|

|

Таблица истинности |

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Входы |

|

Выходы |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

A2 |

A1 |

A0 |

Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EN |

|

Y |

||||||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

1 |

|

X |

X |

X |

0 |

1 |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

0 |

|

0 |

0 |

0 |

D0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D0 |

||||||||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

0 |

|

0 |

0 |

1 |

D1 |

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

D1 |

||||||||||||||

|

|

|

Y |

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

0 |

|

0 |

1 |

0 |

D2 |

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

D2 |

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

0 |

|

0 |

1 |

1 |

D3 |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

D3 |

|||||||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

0 |

|

1 |

0 |

0 |

D4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

D4 |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

0 |

|

1 |

0 |

1 |

D5 |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

D5 |

|||||||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

0 |

|

1 |

1 |

0 |

D6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D6 |

|||||||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||||||

16 – питание; 8 – общий. |

0 |

|

1 |

1 |

1 |

D7 |

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

D7 |

||||||||||||||||||||||||

Рисунок В.19 – Селектор-мультиплексор 8-1 со стробированием

67

42

Рисунок В.17 – Дешифратор-демультиплексор 3-8 с инверсией на выходе

66

6 |

IN74AC157N |

ЭКР1554КП16 |

0 |

|

B0…B3 |

|

7 |

IN74HC158AN |

ЭКР1564КП18 |

1 |

|

|

|

A0...A3 |

||||||

8 |

IN74ACT251N |

ЭКР1594КП15 |

100 |

|

D6 |

|

9 |

IN74AC253N |

ЭКР1554КП12 |

10 |

|

D1 |

|

10 |

IN74HCT251AN |

ЭКР5564КП15 |

011 |

|

D4 |

|

1 Дайте определение и поясните назначение заданного КЦУ.

2 Зарисуйте по [7, приложение В], условное графической обозначение (УГО) заданной микросхемы и поясните назначение выводов.

3 Зарисуйте по [7, приложение В], таблицу истинности для заданной микросхемы и поясните принцип работы.

4 Укажите, какой выход дешифратора-демультиплексора будет выбран, если на информационных входах действует код, заданный в таблице 12. Поясните, при каком условии активный уровень сигнала появится на выбранном выходе и какой уровень сигнала будет на остальных выходах (выполняется для вариантов 1-5).

5 Укажите код, который поступает на информационные и разрешающие входы дешифратора-демультиплексора, если выбран указанный в таблице 12 выход (выполняется для вариантов 1-5).

6 Укажите, какой информационный вход будет соединяться с выходом мультиплексора, если на адресных входах действует код, заданный в таблице 12 (выполняется для вариантов 6-10).

7 Укажите код, который необходимо подать на адресные и разрешающий входы микросхемы мультиплексора, чтобы с выходом соединялся вход, указанный в таблице 12 (выполняется для вариантов 6-10).

8 Определите по [7, приложение Б] основные электрические параметры заданной микросхемы КЦУ. Результат запишите в таблицу, аналогичную по форме таблице 13.

5 Решение задачи см на сайте www.reshuzadachi.ru

Методические указания по выполнению задачи 5

В задаче 5 необходимо изучить стандартную микросхему КЦУ схемотехники КМОП. Для решения этой задачи следует использовать справочный материал, приведенный в [приложения Б и В].

43

|

|

), |

|

|

|

|

|

|

|

заполнения) |

|

(t не более |

нс нс |

28 28 |

8 7 |

температурыотминус |

мкА0= , ауровни |

||

|

(I |

не |

более |

||||||

|

|

PHL |

|

|

|

|

|

|

|

|

|

), |

не более |

|

|

|

|

|

|

|

|

(t |

|

|

|

|

|

||

|

|

PLH |

|

|

|

|

|

|

|

динамическиеистатическиеОсновные–13Таблицапараметры заданных микросхем (образец |

|

), |

|

|

В В В мкА мкА мА мА мкА |

КМОП6ЛИ1564ЭКРIN74HC21AN5 0,1 4,9 – 1,0 1,0 4 – 4 20 |

КМОП1ЛА1554ЭКРIN74AC20N5 0,1 4,9 – 1,0 1,0 24 – 24 40 |

Примечания обозначениямеждународныеуказаныскобкахВ1 соответствующих параметров. источниканапряжениядляуказаныПараметры2 питания U |

потребляемыйМаксимальный.С85°плюсдо40ток I для–инапряженийвыходных≤ 50 мкА. |

U-Схемо-обоУсловноеМеждународное (Vтехникапозначениеобозначение 88-17021ГОСТмикросхем )прототип( |

|||||||||

|

|

CC |

|

|

|

|

|

|

|

|

|

(I |

|

|

|

|

|

|

|

|

|

), |

|

более более более более |

|

|

|

ИП тока выходного для |

|

|

|

(I не не не не |

|

|

|

||||

|

|

OH |

|

|

|

|

|

|

|

|

|

), (I |

|

|

|

|

|

рабочей |

|

|

|

), |

|

|

|

|

|

|

|

|

|

OL |

|

|

|

|

|

|

|

|

|

IH |

|

|

|

|

|

и |

|

|

|

(I |

|

|

|

|

|

В |

|

|

|

), |

|

|

|

|

|

5 |

|

|

|

IL |

|

|

|

|

|

= |

|

|

|

), |

- ме не |

нее |

|

|

|

|

указан |

|

|

(V ), |

|

|

|

|

|||

|

|

OH |

|

|

|

|

|

|

|

|

|

(V не |

более |

|

|

|

|

пот |

|

|

|

OL |

|

|

|

|

|

|

|

|

ИП |

) |

|

|

|

|

|

|

|

|

CC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

44

IN74AC125/IN74ACT125/IN74HC125A/IN74HCT125A (1554ЛП8/1594ЛП8/1564ЛП8/5564ЛП8)

|

|

2 |

|

|

|

|

Y A |

|

|

|

|

|

A1 |

|

& |

3 |

Y1 |

|

|

|

|

|

|||

1 |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

Таблица истинности |

|

||||||

OE |

|

|

|

|

||||||||

|

|

|

|

|

||||||||

|

|

5 |

|

|

|

|

|

|

|

|

|

|

A2 |

|

& |

|

|

|

|

|

|

|

|

||

|

6 |

Y2 |

|

Входы |

Выходы |

|||||||

4 |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

||

OE |

|

|

|

A |

|

|

|

|

Y |

|||

|

|

|

|

|

|

OE |

|

|||||

A3 |

9 |

|

& |

8 |

Y3 |

0 |

|

0 |

|

0 |

||

10 |

|

|

|

|

|

|

|

|||||

|

|

1 |

|

0 |

|

1 |

||||||

|

|

|

|

|||||||||

OE |

|

|

||||||||||

12 |

|

|

|

|

X |

|

1 |

|

Z |

|||

|

|

|

|

|

|

|

|

|||||

A4 |

|

& |

11 |

Y4 |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

||||||

13 |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

||

OE |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

14 – питание; 7 – общий.

Рисунок В.16 – Четыре буферных элемента с тремя состояниями на выходе

IN74AC138/IN74ACT138/IN74HC138A/IN74HCT138A (1554ИД7/1594ИД7/1564ИД7/5564ИД7)

|

|

|

|

|

|

Таблица истинности |

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Входы |

|

|

|

|

|

Выходы |

|

|

|

|||||||

|

|

|

|

|

|

|

СS1 |

|

CS2 |

CS3 |

|

A2A1A0Y0Y1Y2Y3 |

|

Y4 |

Y5 |

Y6 |

Y7 |

|||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

X |

X |

1 |

X |

X X 1 1 1 |

1 |

1 |

1 |

1 |

1 |

||||||||||

|

|

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

X |

1 |

|

|

X |

X |

X X 1 1 1 |

1 |

1 |

1 |

1 |

1 |

||||||||

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

0 |

|

X |

X |

X |

X X 1 1 1 |

1 |

1 |

1 |

1 |

1 |

|||||||||

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

1 |

0 |

|

0 |

|

0 |

0 |

0 |

0 |

1 |

1 |

|

1 |

1 |

|

1 |

1 |

1 |

||||

|

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

1 |

0 |

|

0 |

|

0 |

0 |

1 |

1 |

0 |

1 |

|

1 |

1 |

|

1 |

1 |

1 |

||||

|

|

|

|

|||||||||||||||||||||||

16 – питание; 8 – общий. |

1 |

0 |

|

0 |

|

0 |

1 |

0 |

1 |

1 |

0 |

|

1 |

1 |

|

1 |

1 |

1 |

||||||||

1 |

0 |

|

0 |

|

0 |

1 |

1 |

1 |

1 |

1 |

|

0 |

1 |

|

1 |

1 |

1 |

|||||||||

|

|

|

|

|

|

|

1 |

0 |

|

0 |

|

1 |

0 |

0 |

1 |

1 |

1 |

|

1 |

0 |

|

1 |

1 |

1 |

||

|

|

|

|

|

|

|

1 |

0 |

|

0 |

|

1 |

0 |

1 |

1 |

1 |

1 |

|

1 |

1 |

|

0 |

1 |

1 |

||

|

|

|

|

|

|

|

1 |

0 |

|

0 |

|

1 |

1 |

0 |

1 |

1 |

1 |

|

1 |

1 |

|

1 |

0 |

1 |

||

|

|

|

|

|

|

|

1 |

0 |

|

0 |

|

1 |

1 |

1 |

1 |

1 |

1 |

|

1 |

1 |

|

1 |

1 |

0 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

65 |

IN74AC34/IN74ACT34 (1554ЛИ9/1594ЛИ9)

Y A

Таблица истинности

Вход |

Выход |

A |

Y |

0 |

0 |

1 |

1 |

14 – питание; 7 – общий.

Рисунок В.14 – Шесть повторителей

IN74AC86/IN74ACT86/IN74HC86A/IN74HCT86A (1554ЛП5/1594ЛП5/1564ЛП5/5564ЛП5)

Y A B

Таблица истинности

Входы |

|

Выходы |

|

A |

|

B |

Y |

0 |

|

0 |

0 |

0 |

|

1 |

1 |

1 |

|

0 |

1 |

1 |

|

1 |

0 |

14 – питание; 7 – общий.

Рисунок В.15 – Четыре логических элемента «Исключающее ИЛИ»

www.reshuzadachi.ru

ПРИЛОЖЕНИЕ А (справочное)

Система условных обозначений микросхем стандартной логики производства НПО «Интеграл»

Условные обозначения цифровых микросхем установлены в соответствии с ГОСТ 17021–88. Продукция НПО «Интеграл» ориентирована как на внутренний рынок, так и на экспорт. Поэтому введено международное условное обозначение ИМС.

Обозначение ИМС, выпускаемых НПО «Интеграл», состоит из двух элементов:

–первый элемент – две буквы IN (код НПО «Интеграл»);

–второй элемент – буквенно-цифровое обозначение в соответствии с обозначением зарубежного прототипа. Например, прототип микросхемы зарубежного производства MC74HC08AN, выпускаемый на НПО «Интеграл», имеет обозначение IN74HC08AN.

Буква в конце международного обозначения ИМС указывает на тип корпуса:

–N – для пластмассовых DIP-корпусов с дюймовым шагом между выводами;

–D – для пластмассовых SO-корпусов (ширина корпуса 4 мм);

–DW – для пластмассовых 20-, 24- и 28-выводных SO-«широких» корпусов (ширина корпуса 7,6 мм).

Микросхема IN74HC08AN по ГОСТ 17021–88 имеет обозначение ЭКР1564ЛИ1, а IN74HC08AD – ЭКФ1564ЛИ1. Следовательно, буквы перед номером серии указывают на тип корпуса.

Чертежи различных типов корпусов приведены в [4], [8].

64

ПРИЛОЖЕНИЕ Б (справочное) |

Номенклатура и основные электрические параметры микросхем стандартной логики схемотехники КМОП производства НПО «Интеграл» |

Таблица Б.1 – Номенклатура микросхем стандартной логики схемотехники КМОП производства НПО «Интеграл» |

46

|

5564 (IN74HCT) |

6 |

IN74HCT00A |

IN74HCT02A |

– |

IN74HCT04A |

IN74HCT05A |

|

|

|

|

|

|

|

|

Серии микросхем |

1564 (IN74HC) |

5 |

IN74HC00A |

IN74HC02A |

IN74HC03A |

IN74HC04A |

IN74HC05A |

1594 (IN74ACT) |

4 |

IN74ACT00 |

IN74ACT02 |

– |

IN74ACT04 |

IN74ACT05 |

|

|

|

|

|

|

|

|

|

|

1554 (IN74AC) |

3 |

IN74AC00 |

IN74AC02 |

– |

IN74AC04 |

IN74AC05 |

Подгруппа и вид по ГОСТ 17021–88 |

2 |

ЛА3 |

ЛЕ1 |

ЛА9 |

ЛН1 |

ЛН2 |

|

|

|

|

|

|

|

|

|

Функциональное назначение |

1 |

1 Четыре логических элемента «2 И-НЕ» |

2 Четыре логических элемента «2 ИЛИ-НЕ» |

3 Четыре логических элемента «2 И-НЕ» с открытыми стоками |

4 Шесть логических элементов «НЕ» |

5 Шесть логических элементов «НЕ» с открытыми стоками |

|

|

|

|

|

|

|

|

|

IN74HC30A/IN74HCT30A (1564ЛА2/5564ЛА2)

|

|

|

|

|

Y A | B | C | D | E | F | G | H | |

|||||||||||||||

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

Таблица истинности |

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

Входы |

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Выходы |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

A |

B |

С |

D |

|

E |

|

F |

|

G |

H |

|

Y |

|||

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

0 |

X |

X |

X |

X |

X |

X |

X |

|

1 |

|

|||||

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

X |

0 |

X |

X |

X |

X |

X |

X |

|

1 |

|

|||||

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

X |

X |

0 |

X |

X |

X |

X |

X |

|

1 |

|

|||||

|

|

|

|

|

||||||||||||||||

14 – питание; 7 – общий. |

X |

X |

X |

0 |

X |

X |

X |

X |

|

1 |

|

|||||||||

X |

X |

X |

X |

0 |

X |

X |

X |

|

1 |

|

||||||||||

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

X |

X |

X |

X |

X |

0 |

X |

X |

|

1 |

|

|||||

|

|

|

|

|

X |

X |

X |

X |

X |

X |

0 |

X |

|

1 |

|

|||||

|

|

|

|

|

X |

X |

X |

X |

X |

X |

X |

0 |

|

1 |

|

|||||

|

|

|

|

|

1 |

1 |

1 |

1 |

|

1 |

|

1 |

|

1 |

1 |

|

0 |

|

||

|

|

|

Рисунок В.12 – Логический элемент «8 И-НЕ» |

|

|

|

||||||||||||||

|

|

IN74AC32/IN74ACT32/IN74HC32A/IN74HCT32A |

||||||||||||||||||

|

|

|

(1554ЛЛ1/1594ЛЛ1/1564ЛЛ1/5564ЛЛ1) |

|

|

|

|

|||||||||||||

|

|

|

|

|

Y A B |

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

Таблица истинности |

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

Входы |

|

|

|

|

|

|

Выходы |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

A |

|

|

|

|

B |

|

|

|

|

|

Y |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

0 |

|

|

|

|

0 |

|

|

|

|

|

0 |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

0 |

|

|

|

|

1 |

|

|

|

|

|

1 |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

1 |

|

|

|

|

0 |

|

|

|

|

|

1 |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

1 |

|

|

|

|

1 |

|

|

|

|

|

1 |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

14 – питание; 7 – общий.

Рисунок В.13 – Четыре логических элемента «2 ИЛИ»

63

IN74AC21/IN74ACT21/IN74HC21A (1554ЛИ6/1594ЛИ6/1564ЛИ6)

|

|

|

|

|

Y A B C D |

|

|

|||

|

|

|

|

|

|

|

||||

|

|

|

|

|

Таблица истинности |

|

||||

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Входы |

|

Выходы |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

B |

С |

|

D |

Y |

|

|

|

|

|

||||||

|

|

|

|

|

0 |

X |

X |

|

X |

0 |

|

|

|

|

|

||||||

|

|

|

|

|

X |

0 |

X |

|

X |

0 |

|

|

|

|

|

||||||

|

|

|

|

|

||||||

|

|

|

|

|

X |

X |

0 |

|

X |

0 |

|

|

|

|

|

||||||

|

|

|

|

|

X |

X |

X |

|

0 |

0 |

|

|

|

|

|

||||||

14 – питание; 7 – общий. |

1 |

1 |

1 |

|

1 |

1 |

||||

|

|

|

|

|

|

|||||

Рисунок В.10 – Два логических элемента «4 И»

IN74AC27/IN74ACT27/IN74HC27A/IN74HCT27A (1554ЛЕ4/1594ЛЕ4/1564ЛЕ4/5564ЛЕ4)

Y A B C A B C

Таблица истинности

|

Входы |

|

Выходы |

A |

B |

С |

Y |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

14 – питание; 7 – общий.

Рисунок В.11 – Три логических элемента «3 ИЛИ-НЕ»

62

|

6 |

IN74HCT08A |

IN74HCT10A |

– |

IN74HCT20A |

– |

IN74HCT22A |

IN74HCT27A |

IN74HCT30A |

IN74HCT32A |

– |

|

|

|

|

|

|

|

|

|

|

|

|

|

5 |

IN74HC08A |

IN74HC10A |

IN74HC11A |

IN74HC20A |

IN74HC21A |

IN74HC22A |

IN74HC27A |

IN74HC30A |

IN74HC32A |

– |

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

IN74ACT08 |

IN74ACT10 |

IN74ACT11 |

IN74ACT20 |

IN74ACT21 |

– |

IN74ACT27 |

– |

IN74ACT32 |

IN74ACT34 |

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

IN74AC08 |

IN74AC10 |

IN74AC11 |

IN74AC20 |

IN74AC21 |

– |

IN74AC27 |

– |

IN74AC32 |

IN74AC34 |

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

ЛИ1 |

ЛА4 |

ЛИ3 |

ЛА1 |

ЛИ6 |

ЛА7 |

ЛЕ4 |

ЛА2 |

ЛЛ1 |

ЛИ9 |

Продолжение таблицы Б.1 |

|

|

|

|

|

|

|

|

|

|

|

1 |

6 Четыре логических элемента «2 И» |

7 Три логических элемента «3 И-НЕ» |

8 Три логических элемента «3 И» |

9 Два логических элемента «4 И-НЕ» |

10 Два логических элемента «4 И» |

11 Два логических элемента «4 И-НЕ» с открытым стоком |

12 Три логических элемента «3 ИЛИ-НЕ» |

13 Логический элемент «8 И-НЕ» |

14 Четыре логических элемента «2 ИЛИ» |

15 Шесть повторителей |

47

|

6 |

IN74HCT86A |

IN74HCT125A |

IN74HCT138A |

IN74HCT139A |

IN74HCT151A |

IN74HCT153A |

– |

IN74HCT55A |

|

|

|

|

|

|

|

|

|

|

|

5 |

IN74HC86A |

IN74HC125A |

IN74HC138A |

IN74HC139A |

IN74HC151A |

IN74HC153A |

IN74HC154A |

IN74HC55A |

|

|

|

|

|

|

|

|

|

|

|

4 |

IN74ACT86 |

IN74ACT125 |

IN74ACT138 |

IN74ACT139 |

IN74ACT151 |

IN74ACT153 |

– |

– |

|

|

|

|

|

|

|

|

|

|

|

3 |

IN74AC86 |

IN74AC125 |

IN74AC138 |

IN74AC139 |

IN74AC151 |

IN74AC153 |

– |

– |

|

|

|

|

|

|

|

|

|

|

|

2 |

ЛП5 |

ЛП8 |

ИД7 |

ИД14 |

КП7 |

КП2 |

ИД3 |

ИД4 |

Продолжение таблицы Б.1 |

|

|

|

|

|

|

|

|

|

1 |

16 Четыре двухвходовых логических элемента «Исключающее ИЛИ» |

17 Четыре буферных элемента с тремя состояниями на выходе |

18 Дешифратор-демуль- типлексор 3-8 с инверсией на выходе |

19 Два дешифратора-де- мультиплексора 2-4 с инверсией на выходе |

20 Селектор-мультип- лексор 8-1 со стробированием |

21 Два селектора-муль- типлексора 4-1 |

22 Дешифратор-демуль- типлексор 4-16 с инверсией на выходе |

23 Сдвоенный дешифра- тор-демультиплексор 2-4 |

IN74AC11/IN74ACT11/IN74HC11A (1554ЛИ3/1594ЛИ3/1564ЛИ3)

Y A B C

Таблица истинности

|

Входы |

|

Выходы |

A |

B |

С |

Y |

0 |

X |

X |

0 |

X |

0 |

X |

0 |

X |

X |

0 |

0 |

1 |

1 |

1 |

1 |

14 – питание; 7 – общий.

Рисунок В.8 – Три логических элемента «3 И»

IN74AC20/IN74ACT20/IN74HC20A/IN74HCT20A (1554ЛА1/1594ЛА1/1564ЛА1/5564ЛА1)

|

|

|

|

|

|

Y |

A B C D |

A | B | C | D |

||||

|

|

|

|

|

|

Таблица истинности |

|

|||||

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Входы |

|

Выходы |

||

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

A |

|

B |

С |

|

D |

Y |

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

0 |

|

X |

X |

|

X |

1 |

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

X |

|

0 |

X |

|

X |

1 |

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

X |

|

X |

0 |

|

X |

1 |

14 – питание; 7 – общий. |

X |

|

X |

X |

|

0 |

1 |

|||||

1 |

|

1 |

1 |

|

1 |

0 |

||||||

Рисунок В.9 – Два логических элемента «4 И-НЕ»

61

48

IN74AC08/IN74ACT08/IN74HC08A/IN74HCT08A (1554ЛИ1/1594ЛИ1/1564ЛИ1/5564ЛИ1)

Y A B

Таблица истинности

Входы |

|

Выходы |

|

A |

|

B |

Y |

0 |

|

0 |

0 |

0 |

|

1 |

0 |

1 |

|

0 |

0 |

1 |

|

1 |

1 |

14 – питание; 7 – общий.

Рисунок В.6 – Четыре логических элемента «2 И»

IN74AC10/IN74ACT10/IN74HC10A/IN74HCT10A (1554ЛА4/1594ЛА4/1564ЛА4/5564ЛА4)

Y A B C

Таблица истинности

|

Входы |

|

Выходы |

A |

B |

С |

Y |

0 |

X |

X |

1 |

X |

0 |

X |

1 |

X |

X |

0 |

1 |

1 |

1 |

1 |

0 |

Примечание – «X» – 0 или 1

14 – питание; 7 – общий.

Рисунок В.7 – Три логических элемента «3 И-НЕ»

60

|

6 |

IN74HCT157A |

– |

IN74HCT240A |

IN74HCT241A |

IN74HCT244A |

IN74HCT245A |

|

|

|

|

|

|

|

|

|

5 |

IN74HC157A |

IN74HC158A |

IN74HC240A |

IN74HC241A |

IN74HC244A |

IN74HC245A |

|

|

|

|

|

|

|

|

|

4 |

IN74ACT157 |

IN74ACT158 |

IN74ACT240 |

IN74ACT241 |

IN74ACT244 |

IN74ACT245 |

|

|

|

|

|

|

|

|

|

3 |

IN74AC157 |

IN74AC158 |

IN74AC240 |

IN74AC241 |

IN74AC244 |

IN74AC245 |

|

|

|

|

|

|

|

|

|

2 |

КП16 |

КП18 |

АП3 |

АП4 |

АП5 |

АП6 |

Продолжение таблицы Б.1 |

|

|

|

|

|

|

|

1 |

24 Четыре селекторамультиплексора 2-1 |

25 Четыре селекторамультиплексора 2-1 с инверсией на выходе |

26 Два четырехразрядных формирователя с тремя состояниями и инверсией на выходе |

27 Два четырехразрядных формирователя с тремя состояниями на выходе |

28 Два четырехразрядных формирователя с тремя состояниями на выходе |

29 Восьмиразрядный двунаправленный приемопередатчик с выходами на три состояния |

49

|

6 |

IN74HCT251A |

– |

– |

– |

IN74HCT283A |

|

|

|

|

|

|

|

|

5 |

IN74HC251A |

IN74HC253A |

IN74HC257A |

IN74HC258A |

IN74HC283A |

|

|

|

|

|

|

|

|

4 |

IN74ACT251 |

IN74ACT253 |

IN74ACT257 |

IN74ACT258 |

– |

|

|

|

|

|

|

|

|

3 |

IN74AC251 |

IN74AC253 |

IN74AC257 |

IN74AC258 |

– |

|

|

|

|

|

|

|

|

2 |

КП15 |

КП12 |

КП11 |

КП14 |

ИМ6 |

Продолжение таблицы Б.1 |

|

|

|

|

|

|

1 |

30 Селектор-мультип- лексор 8-1 с тремя состояниями на выходе |

31 Два селекторамультиплексора 4-1 с тремя состояниями на выходе |

32 Четыре селекторамультиплексора 2-1 с тремя состояниями на выходе |

33 Четыре селекторамультиплексора 2-1 с тремя состояниями и инверсией на выходе |

34 Четырехразрядный двоичный сумматор с ускоренным переносом |

IN74AC04/IN74ACT04/IN74HC04A/IN74HCT04A (1554ЛН1/1594ЛН1/1564ЛН1/5564ЛН1)

Y A

Таблица истинности

Вход |

Выход |

A |

Y |

0 |

1 |

1 |

0 |

14 – питание; 7 – общий.

Рисунок В.4 – Шесть логических элементов «НЕ»

IN74AC05/IN74ACT05/IN74HC05A (1554ЛН2/1594ЛН2/1564ЛН2)

Y A

Таблица истинности

Вход |

Выход |

A |

Y |

0 |

Z |

1 |

0 |

14 – питание; 7 – общий.

Рисунок В.5 – Шесть логических элементов «НЕ» с открытым стоком

59

50