Электроника Коллектив кафедры Электроника, БГУИР 2014 (Мет пособие)

.pdf

www.reshuzadachi.ru

КОНТРОЛЬНЫЕ ЗАДАНИЯ

Задача 1

1 Переведите в десятичную систему счисления с точностью до семи знаков после запятой числа, указанные в таблице 1.

Таблица 1 – Исходные данные к задаче 1, пункт 1

Номер |

Основание СС |

Номер |

Основание СС |

||

варианта |

P = 16 |

P = 2 |

варианта |

P = 16 |

P = 2 |

1 |

27C,A5 |

110110,1010 |

6 |

24B,8C |

101110,1011 |

2 |

3D0,7B |

101101,0110 |

7 |

3A0,E9 |

110010,0111 |

3 |

591,ED |

100110,0101 |

8 |

18B,E6 |

111100,0011 |

4 |

4BA,32 |

100011,1100 |

9 |

2E7,A5 |

101010,0101 |

5 |

3CA,5F |

111010,0111 |

10 |

4B9,0C |

100110,0011 |

2 Переведите в двоичную систему счисления числа, указанные в таблице 2.

Таблица 2 – Исходные данные к задаче 1, пункт 2

Номер |

Основание СС |

Номер |

Основание СС |

||

варианта |

P = 16 |

P = 10 |

варианта |

P = 16 |

P = 10 |

1 |

C2F,5AE |

356,29 |

6 |

E39,6CA |

408,32 |

2 |

F20,CB6 |

573,19 |

7 |

A5E,8B9 |

361,62 |

3 |

D76,AE5 |

567,27 |

8 |

C07,BA4 |

464,81 |

4 |

90C,B3E |

247,36 |

9 |

FD0,3AB |

432,72 |

5 |

A89,0DC |

196,82 |

10 |

90B,F76 |

285,34 |

Примечание – Десятичное число переведите с точностью семь знаков после запятой

3 Сложите в двоичной СС в дополнительном модифицированном коде с точностью до пяти знаков после запятой два десятичных числа X1 и X2, указанные в таблице 3, и результат сравните с результатом сложения в десятичной СС.

Таблица 3 – Исходные данные к задаче 1, пункт 3

Номер |

Десятичные числа |

Номер |

Десятичные числа |

||

варианта |

X1 |

X2 |

варианта |

X1 |

X2 |

|

|

||||

1 |

+ 0,380 |

– 0,630 |

6 |

– 0,365 |

+ 0,240 |

2 |

+ 0,600 |

– 0,850 |

7 |

+ 0,290 |

– 0,540 |

3 |

+ 0,275 |

– 0,525 |

8 |

– 0,660 |

+ 0,410 |

4 |

– 0,750 |

+ 0,625 |

9 |

+ 0,825 |

– 0,950 |

5 |

+ 0,175 |

– 0,425 |

10 |

– 0,860 |

+ 0,610 |

4 Сложите в коде 8421 два десятичных числа, указанные в таблице 4, и результат сравните с результатом сложения в десятичной СС.

Таблица 4 – Исходные данные к задаче 1, пункт 4

Номер |

Десятичные числа |

Номер |

Десятичные числа |

||

варианта |

X1 |

X2 |

варианта |

X1 |

X2 |

|

|

||||

1 |

536 |

768 |

6 |

295 |

806 |

2 |

487 |

713 |

7 |

368 |

937 |

3 |

253 |

748 |

8 |

951 |

349 |

4 |

325 |

697 |

9 |

476 |

528 |

5 |

497 |

504 |

10 |

924 |

178 |

Методические указания по выполнению задачи 1

К выполнению задачи 1 целесообразно приступить после изучения темы «Арифметические основы цифровой техники». Материал данной темы подробно освещен в [1, С. 72-92], [2, С. 151-166], [3, С. 9-19, 23-34, 87-94].

Изучите правила и примеры, представленные в учебниках и данных методических указаниях. Затем приступайте к решению задачи 1.

Правила и примеры перевода чисел в десятичную систему счисления из двоичной и шестнадцатеричной систем счисления

приведены в [1, С. 73], [2, С. 151, 152, 155, 156].

Рассмотрим пример перевода шестнадцатеричного числа A5F,C83 в десятичную систему счисления:

2

A5F,C83(16) 10 162 5 161 15 160 12 16 1 8 16 2 3 16 3

2655,7819824(10).

Правила и примеры перевода чисел в двоичную систему счисления из шестнадцатеричной приведены в [1, с. 75], [2, с. 154].

Рассмотрим пример:

0110 1101 0101, 1011 0000 1100 |

65D,B0C |

(16) |

. |

(2) |

|

|

|

6 D 5 B 0 C |

|

|

|

Переводить десятичные числа в двоичную систему счисления можно различными способами. Наиболее простым является следующий расчетный метод:

Целую часть числа последовательно делят на два до тех пор, пока целая часть частного от последовательного деления станет равна 0. Результат перевода состоит из цифр остатков, причем последний остаток будет представлять старший разряд в записи целой части двоичного числа.

Дробную часть переводят путем последовательного умножения на два. Результат перевода дробной части получают из цифр целых частей частичных произведений, причем старшим разрядом является первая целая часть.

Целая часть числа переводится точно, дробная – приблизи-

тельно. Точность перевода дробной части зависит от числа знаков по-

сле запятой (см. [3, С. 14-19]).

Рассмотрим пример перевода десятичного числа 283,64 в двоичную систему счисления с точностью до семи знаков после запятой.

Переведем целую часть числа:

106

3

– 283 |

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

282 |

– |

141 |

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

140 |

– |

70 |

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

1 |

70 |

– |

35 |

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Младший |

|

|

0 |

34 |

– 17 |

|

2 |

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

разряд |

|

|

|

|

1 |

|

16 |

– |

8 |

|

2 |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

1 |

8 |

– |

4 |

|

2 |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

0 |

4 |

– |

2 |

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

2 |

– |

1 |

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

Направление |

|

|

|

|

|

0 |

0 |

0 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|||||||

|

|

|

|

|

|

|

|

чтения |

|

|

|

|

|

|

|

|

|

|||

Старший

разряд

Запишем результат перевода целой части: 283(10) 100011011(2).

Переведем дробную часть числа, умножая последовательно на два только дробь, стоящую справа от запятой.

0,64 × 2

Старший разряд × 1 ,28

2

0,56 × 2

1,12 × 2

Направление чтения × 0,24

2

× |

0,48 |

|

2 |

× |

0,96 |

|

2 |

Младший |

1 ,92 |

|

разряд |

||

|

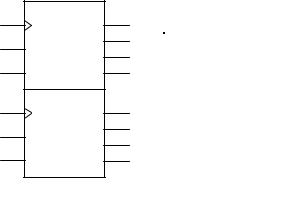

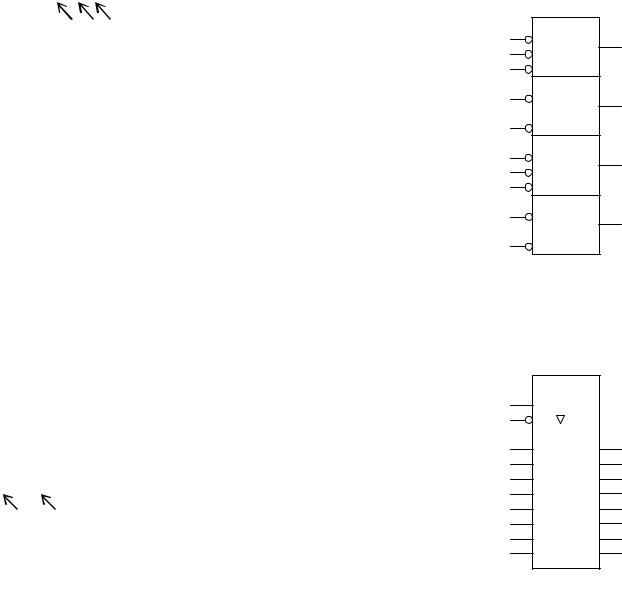

Рисунок В.19 – Два четырехразрядных двоичных счетчика

105

4

IN74AC4520/IN74ACT2520 (1554ИЕ23/1594ИЕ23)

Таблица состояний |

|

||||

|

Входы |

|

|

|

|

|

|

|

Функция |

||

C |

EN |

|

R |

|

|

|

|

|

|||

X |

X |

|

1 |

|

Сброс на «0» |

↑ |

1 |

|

0 |

|

Счет на увеличение |

0 |

↓ |

|

0 |

|

|

↓ |

X |

|

0 |

|

Без изменений |

X |

↑ |

|

0 |

|

|

↑ |

0 |

|

0 |

|

(хранение) |

1 |

↓ |

|

0 |

|

|

16 – питание; 8 – общий.

104

Запишем результат перевода дробной части: 0,64(10) 0,1010001(2).

Полный результат перевода: 283,64(10) 100011011,1010001(2).

Правила представления и суммирования двоичных чисел в дополнительном коде приведены в [3], С. 30-33, 81-87]. Перед решением пункта 3 задачи 1 изучите теоретический материал и примеры, приведенные в данных методических указаниях.

Дополнительный код отрицательного двоичного числа находится как дополнения модуля этого числа до граничного числа, представляемого в данной разрядной сетке. Дополнительный код для двоичных чисел меньших единицы образуется по формуле:

|

X, еслиX 0, |

|

|

[X]доп |

0, |

|

10(2) X, еслиX |

|

где 10(2) –граничное число, причем [X]гр | Xmax | 1. |

||

Рассмотрим примеры: |

|

|

X1 = + 0,1101; |

[X1]доп 0.1101. |

|

X2 = – 0,1101; |

[X2 ]доп 10 ( 0,1101) 1.0011. |

|

Из формулы и примеров видно, что изображение положительного числа в дополнительном коде совпадает с его изображением в прямом коде. Для представления отрицательного двоичного числа в дополнительном коде необходимо в знаковом разряде поставить единицу, произвести замену цифр исходного числа на обратные и к полученному коду прибавить единицу младшего разряда.

Обратное преобразование, т.е. получение числа из дополнительного кода выполняется по тому же правилу, что и получение дополнительного кода. Рассмотрим пример:

[X]доп 1.1011;

[X]пр 1.0100 0,0001 1.0101; X – 0,0101.

5

При алгебраическом сложении двоичных чисел в дополнительном коде используются следующие правила:

а) знаковые разряды суммируются так же, как и значащие разряды числа;

б) единица переноса из знакового разряда при сложении в дополнительном коде отбрасывается;

в) если в знаковом разряде суммы получился нуль, то сумма положительна и для перехода к естественной форме числа обратное преобразование не требуется. Если же в знаковом разряде суммы получилась единица, то сумма отрицательна и требуется обратное преобразование.

Рассмотрим примеры.

Пример 1

Выполним суммирование двух двоичных чисел X1 = + 0,11001 и X2 = – 0,01011 в дополнительном коде.

|

|

1 |

|

|

|

1 |

|

|

|

– |

Переносы |

|

|

[X1]доп = |

|

|

0. |

1 |

1 |

0 |

0 |

1 |

|

|

|

+ |

|

|

|

|

|

|

|

|

|

|

|

|

|

[X2 ]доп = |

|

|

1. |

1 |

0 |

1 |

0 |

1 |

|

– |

Сумма |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

[X3 ]доп = |

1 |

0. |

0 |

1 |

1 |

1 |

0 |

|

|

|

|

|

X3 = |

|

|

– |

отбрасывается |

|

|

|||||

|

|

|

|

|

||||||||

|

|

|

|

|

||||||||

|

+ |

0, |

0 |

1 |

1 |

1 |

0 |

|

(2) . |

|

||

Результат получился положительным, и обратное преобразование не требуется.

Пример 2

Поменяем знаки чисел X1 и X2 и выполним суммирование в до-

полнительном коде. Результат получится отрицательным, и потребуется обратное преобразование.

IN74AC534/IN74ACT534/IN74HC534A/IN74HCT534A (1554ИР41/1594ИР41/1564ИР41/5564ИР41)

Таблица состояний

|

Входы |

|

Выходы |

Функция |

|||

EN |

C |

D |

Q |

||||

|

|||||||

0 |

|

↑ |

1 |

1 |

Загрузка 1 |

||

0 |

|

↑ |

0 |

0 |

Загрузка 0 |

||

0 |

|

0, 1, ↓ |

X |

Без изм. |

Хранение |

||

1 |

|

X |

X |

Z |

Третье состояние |

||

20 – питание; 10 – общий.

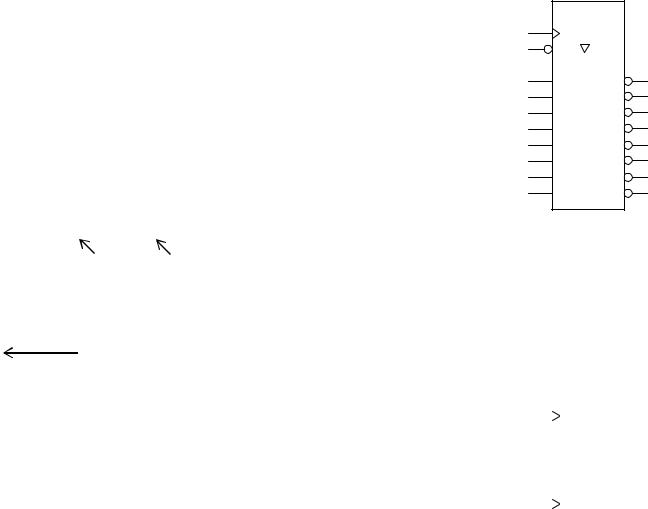

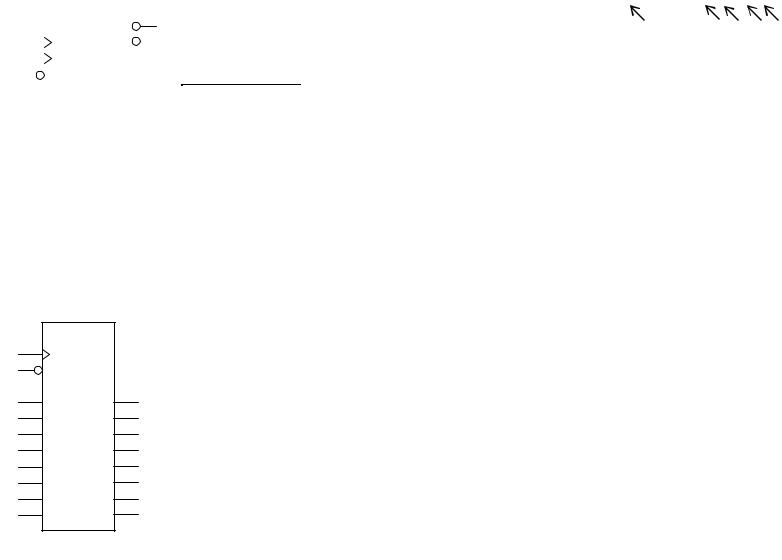

Рисунок В.17 – Восьмиразрядный регистр, управляемый по фронту, с параллельным вводом-выводом данных, с тремя состояниями и инверсией на выходе

IN74AC4015/IN74ACT4015/IN74HC4015A (1554ИР46/1594ИР46/1564ИР46)

7 |

SRG4a |

5 |

Таблица состояний |

|

||||||

Da |

Q0a |

|

|

|

|

|

|

|

||

|

4 |

|

|

|

|

|

|

|

||

9 |

Ca |

Q1a |

|

Входы |

Выходы |

Функция |

||||

3 |

|

|||||||||

6 |

Q2a |

|

C |

D |

R |

Q0 |

Qn |

|||

|

10 |

|

|

|||||||

Ra |

Q3a |

|

|

|

|

|

|

|

||

|

X |

X |

1 |

0 |

0 |

Сброс на «0» |

||||

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

Последователь- |

15 |

SRG4b |

13 |

|

↑ |

0 |

0 |

0 |

Qn–1 |

||

Db |

Q0b |

|

ный сдвиг |

|||||||

|

12 |

|

|

|

|

|

|

|||

1 |

Cb |

Q1b |

|

↑ |

1 |

0 |

1 |

Qn–1 |

Последователь- |

|

11 |

|

|||||||||

14 |

Q2b |

|

ный сдвиг |

|||||||

|

2 |

|

|

|

|

|

||||

Rb |

Q3b |

|

↓ |

X |

0 |

Без изм. |

Хранение |

|||

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

16 – питание; 8 – общий.

Рисунок В.18 – Два четырехразрядных сдвиговых регистра с последовательным вводом, параллельным выводом информации

103

6

IN74AC374/IN74ACT374/IN74HC374A/IN74HCT374A (1554ИР23/1594ИР23/1564ИР23/5564ИР23)

Таблица состояний |

|

|||||||

|

|

|

Входы |

|

|

|

||

|

|

Выходы |

Функция |

|||||

|

|

EN |

C |

D |

Q |

|||

|

|

|

||||||

|

|

0 |

|

↑ |

1 |

1 |

Загрузка 1 |

|

|

|

0 |

|

↑ |

0 |

0 |

Загрузка 0 |

|

|

|

0 |

|

0, 1, ↓ |

X |

Без изм. |

Хранение |

|

|

|

1 |

|

X |

X |

Z |

Третье состояние |

|

20 – питание; 10 – общий.

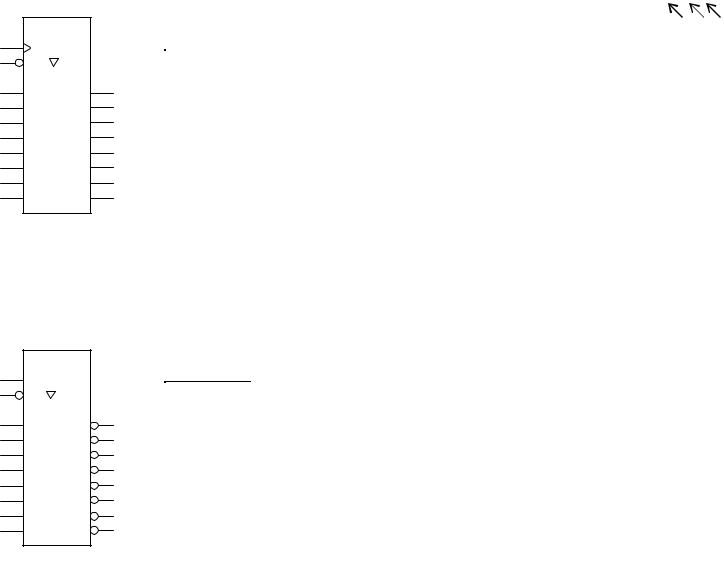

Рисунок В.15 – Восьмиразрядный регистр, управляемый по фронту, с параллельным вводом-выводом данных, с тремя состояниями выхода

IN74AC533/IN74ACT533/IN74HC533A/IN74HCT533A (1554ИР40/1594ИР40/1564ИР40/5564ИР40)

Таблица состояний |

|

||||||||

|

|

|

Входы |

|

|

|

|||

|

|

Выходы |

Функция |

||||||

|

|

EN |

LE |

|

D |

Q |

|||

|

|

|

|

||||||

|

|

0 |

|

1 |

|

1 |

0 |

Передача дан- |

|

|

|

0 |

|

1 |

|

0 |

1 |

ных со входов D |

|

|

|

0 |

|

0 |

|

X |

Без изм. |

Хранение |

|

|

|

|

|

(защелка) |

|||||

|

|

1 |

|

X |

|

X |

Z |

Третье состояние |

|

20 – питание; 10 – общий.

Рисунок В.16 – Восьмиразрядный регистр, управляемый по уровню, с параллельным вводом-выводом данных, с тремя состояниями и инверсией на выходе

102

|

|

|

|

1 |

1 |

1 |

|

|

– |

Переносы |

[X1]доп = |

1. |

0 |

0 |

1 |

1 |

1 |

|

|

||

+ [X2 |

]доп = |

0. |

0 |

1 |

0 |

1 |

1 |

|

|

|

[X3 |

]доп = |

1. |

1 |

0 |

0 |

1 |

0 |

– |

Сумма |

|

[X3 ]пр |

= |

1. |

0 |

1 |

1 |

0 |

1 + 0, 0 0 0 0 1 = 1. 0 1 1 1 0. |

|||

|

X3 |

= – |

0, |

0 |

1 |

1 |

1 |

0 |

(2) . |

|

При сложении чисел одного знака может произойти переполнение разрядной сетки, что приведет к искажению результата. На практике для выявления переполнения разрядной сетки применяют модифицированные машинные коды, в которых два знаковых разряда. Для положительных чисел в знаковых разрядах записывается 00, для отрицательных – 11. Появление комбинаций 01 или 10 в знаковых разрядах свидетельствует о переполнении разрядной сетки, т.е. является сигналом ошибки. Например, двоичное число X = – 0,1101 в модифицированном дополнительном коде будет записано следующим образом:

[X]мдоп = 11.0011.

Пример 3

Выполним суммирование двух десятичных чисел X1 = + 0,450 и X2 = – 0,575 в двоичной СС с точностью до пяти знаков после запятой

в дополнительном модифицированном коде и сравним результаты суммирования в двоичной и десятичной СС.

Так как | X2 | > | X1 |, то в естественной форме следует выполнить вычитание числа X1 из числа X2 и результату присвоить знак минус.

+X1 = |

+ |

0, |

4 |

5 |

0 |

(10) |

= |

+ |

0, |

0 |

1 |

1 |

1 |

0 |

(2) |

||

|

X2 |

= |

– |

0, |

5 |

7 |

5 |

(10) |

= |

– |

0, |

1 |

0 |

0 |

1 |

0 |

(2) |

|

X3 |

= |

– |

0, |

1 |

2 |

5 |

(10) |

= |

– |

0, |

0 |

0 |

1 |

0 |

0 |

(2) |

7

|

|

|

|

1 |

1 |

1 |

|

|

|

+ [X1]мдоп |

= |

0 |

0. |

0 |

1 |

1 |

1 |

0 |

|

[X2 ]мдоп |

= |

1 |

1. |

0 |

1 |

1 |

1 |

0 |

|

[X3 ]мдоп |

= |

1 |

1. |

1 |

1 |

1 |

0 |

0 |

|

[X3 ]прм |

= |

1 |

1. |

0 |

0 |

0 |

1 |

1 + 0, 0 0 0 0 1 = 1 1. 0 0 1 0 0. |

|

X3 |

= |

– 0,00100 (2) |

= – (0 · 20 + 0 · 2–1 + 0 · 2–2 + 1 · 2–3 + |

||||||

+ 0 · 2–4 + 0 · 2–5) = – 0,125 (10) .

Результаты суммирования в естественной форме и дополнительном модифицированном коде совпадают.

Правило и пример перевода десятичного числа в двоично-

десятичный код 8421 приведены в [1, С. 73, 74] и [5, С. 19, 20].

Рассмотрим пример:

304,971 |

0011 0000 0100, 1001 0111 0001 |

. |

|||||

(10) |

(2 10) |

|

|||||

|

3 |

0 |

4 |

9 |

7 |

1 |

|

Правило и примеры суммирования десятичных чисел в коде

8421 приведены в [1, С. 85, 86], [2, С. 165], [3, С. 91, 92].

Рассмотрим пример суммирования десятичных чисел N1 = 458 и N2 = 629 в десятичной СС и коде 8421.

Десятичная система счисления:

|

|

|

1 |

|

1 |

|

|

– |

Переносы |

+ |

N1 = |

4 |

5 |

8 |

(10) |

– |

Первое слагаемое |

||

|

|

N2 |

= |

6 |

2 |

9 |

(10) |

– |

Второе слагаемое |

|

|

N3 |

= 1 |

0 |

8 |

7 |

(10) |

– |

Сумма |

IN74HC279A (1564ТР2)

Таблица состояний

|

Входы |

Выходы |

Функция |

||||||||

S1 |

S2 |

R |

Q |

||||||||

|

|||||||||||

0 |

|

0 |

|

0 |

|

1* |

Неопределенность |

||||

0 |

|

|

X |

1 |

|

1 |

Установка |

||||

|

X |

|

0 |

|

1 |

|

1 |

Установка |

|||

1 |

|

1 |

|

0 |

|

0 |

Сброс |

||||

1 |

|

1 |

|

1 |

|

Без изм. |

Хранение |

||||

16 – питание; 8 – общий.

Рисунок В.13 – Четыре RS-триггера

IN74AC373/IN74ACT373/IN74HC373A/IN74HCT373A (1554ИР22/1594ИР22/1564ИР22/5564ИР22)

Таблица состояний

|

Входы |

|

Выходы |

Функция |

|||

EN |

LE |

|

D |

Q |

|||

|

|

||||||

0 |

|

1 |

|

1 |

1 |

Передача дан- |

|

0 |

|

1 |

|

0 |

0 |

ных со входов D |

|

0 |

|

0 |

|

X |

Без изм. |

Хранение |

|

|

|

(защелка) |

|||||

1 |

|

X |

|

X |

Z |

Третье состояние |

|

20 – питание; 10 – общий.

Рисунок В.14 – Восьмиразрядный регистр, управляемый по уровню, с параллельным вводом-выводом данных, с тремя состояниями на выходе

101

8

IN74AC192(193)/IN74ACT192(193)/IN74HC192(193)A/IN74HCT192(193)A

(1554ИЕ6(ИЕ7)/1594ИЕ6(ИЕ7)/1564ИЕ6(ИЕ7)/5564ИЕ6(ИЕ7))

|

|

|

|

|

|

|

|

B0 |

|

Q0 Q1 Q2 Q3 |

CD |

|

|

|||||||

|

|

|

|

|

|

|

|

Q0 Q1 Q2 Q3 |

|

|

||||||||||

|

|

|

|

|

C0 |

CU |

||||||||||||||

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

Таблица состояний |

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

Входы |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Функция |

||||||

|

|

|

|

|

|

|

|

R |

LD |

+1 |

-1 |

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

1 |

|

|

X |

X |

X |

Асинхронный сброс |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

0 |

|

0 |

|

X |

X |

Предустановка |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

16 – питание; 8 – общий. |

|

0 |

|

1 |

|

↑ |

1 |

Счет на увеличение |

||||||||||||

|

0 |

|

1 |

|

1 |

↑ |

Счет на уменьшение |

|||||||||||||

|

|

|

|

|

|

0 |

|

1 |

|

1 |

1 |

Хранение |

||||||||

Рисунок В.11 – Синхронный четырехразрядный двоично-десятичный (двоичный) реверсивный счетчик с параллельной загрузкой

IN74AC273/IN74ACT273/IN74HC273A/IN74HCT273A (1554ИР35/1594ИР35/1564ИР35/5564ИР35)

Таблица состояний

|

Входы |

Выходы |

Функция |

|||

R |

|

C |

D |

Q |

||

|

|

|||||

0 |

|

X |

X |

0 |

Сброс на «0» |

|

1 |

|

↑ |

1 |

1 |

Загрузка 1 |

|

1 |

|

↑ |

0 |

0 |

Загрузка 0 |

|

1 |

|

0 |

X |

Без изм. |

Хранение |

|

1 |

|

↓ |

X |

|||

20 – питание; 10 – общий.

Рисунок В.12 – Восьмиразрядный регистр, управляемый по фронту, с параллельным вводом-выводом данных, с входом сброса

100

Код 8421:

|

|

|

1 |

|

|

|

1 |

1 |

1 |

1 |

|

|

|

|

|

|

– Переносы |

|

N |

= |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

(2-10) |

– Первое слагаемое |

|

+ |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

N2 = |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

|

|

– Второе слагаемое |

||

|

(2-10) |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

N*3 = |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

(2-10) |

– Предварительная |

||

|

N4 |

= |

0 |

1 |

1 |

0 |

|

|

|

|

0 |

1 |

1 |

0 |

|

|

сумма |

|

|

|

|

|

(2-10) |

– Поправка |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

N3 |

= 1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

(2-10) |

– Окончательная |

|

|

|

|

|

|

|

сумма |

|||||||||||

|

|

|

|

|

|||||||||||||

|

|

1 |

|

|

0 |

|

|

|

8 |

|

|

|

7 |

|

|

|

|

В младшей тетраде коррекция проведена из-за наличия единицы переноса во вторую тетраду.

Результаты суммирования в десятичной и двоично-десятич- ной системах счисления совпадают.

Задача 2

Разработайте логическую и принципиальную электрическую схему КЦУ, функционирование которого задано таблицей истинности (таблица 5).

1 Минимизируйте заданную логическую функцию табличным методом с помощью карт Карно. Запишите результат минимизации в МДНФ.

2 Постройте логическую схему устройства в базисе И, ИЛИ, НЕ. 3 Запишите результат минимизации через логическую операцию

И-НЕ.

4 Постройте логическую схему устройства в базисе И-НЕ.

5 Постройте принципиальную электрическую схему устройства в базисе И-НЕ на микросхемах схемотехники КМОП, серия которых задана в примечании к таблице 5.

6 Синтезировать в базисе ИЛИ-НЕ КЦУ согласно заданному варианту.

7 Преобразовать МКНФ ЛФ в базис ИЛИ-НЕ.

9

8 Построить логическую схему КЦУ в базисе ИЛИ-НЕ на микросхемах схемотехники КМОП серии 1564.

9 Построить принципиальную электрическую схему КЦУ в базисе ИЛИ-НЕ на микросхемах схемотехники КМОП.

10 Проверьте правильность функционирования логических и принципиальной электрической схем КЦУ для пятого набора аргументов и сделайте вывод о правильности их функционирования. 11 Определите среднюю задержку распространения сигнала от входов к выходу и среднюю потребляемую мощность в принципиальной электрической схеме КЦУ.

Таблица 5 – Исходные данные для синтеза КЦУ

Номер |

|

Наборы |

|

|

|

|

Номер варианта |

|

|

|

|||||

набора |

аргументов |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

– |

|||

аргументов |

x4 |

x3 |

x2 |

x1 |

f1 |

f2 |

f3 |

f4 |

f5 |

f6 |

f7 |

f8 |

f9 |

f10 |

f11 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

2 |

0 |

0 |

1 |

0 |

1 |

1 |

Ф |

0 |

Ф |

Ф |

Ф |

1 |

1 |

0 |

1 |

3 |

0 |

0 |

1 |

1 |

Ф |

0 |

1 |

Ф |

0 |

1 |

0 |

Ф |

Ф |

1 |

0 |

4 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

Ф |

5 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

Ф |

0 |

1 |

1 |

0 |

1 |

1 |

6 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

Ф |

1 |

Ф |

Ф |

0 |

Ф |

7 |

0 |

1 |

1 |

1 |

0 |

0 |

Ф |

1 |

Ф |

0 |

Ф |

1 |

1 |

1 |

1 |

8 |

1 |

0 |

0 |

0 |

1 |

Ф |

0 |

0 |

Ф |

1 |

0 |

0 |

1 |

Ф |

1 |

9 |

1 |

0 |

0 |

1 |

Ф |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

10 |

1 |

0 |

1 |

0 |

1 |

1 |

Ф |

Ф |

0 |

Ф |

Ф |

0 |

Ф |

0 |

1 |

11 |

1 |

0 |

1 |

1 |

1 |

Ф |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

12 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

Ф |

Ф |

1 |

Ф |

0 |

0 |

Ф |

1 |

13 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

14 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

Ф |

Ф |

Ф |

Ф |

15 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

Ф |

Ф |

1 |

1 |

0 |

0 |

1 |

0 |

Методические указания к решению задачи №2

Рассмотрим особенности минимизации ЛФ табличным методом с помощью карт Карно и примеры синтеза КЦУ в различных базисах.

IN74AC174/IN74ACT174/IN74HC174A/IN74HCT174A (1554ТМ9/1594ТМ9/1564ТМ9/5564ТМ9)

Таблица состояний

|

Входы |

Выходы |

Функция |

||||||

R |

|

C |

D |

Q |

Q |

||||

|

|

||||||||

0 |

|

X |

X |

0 |

1 |

|

Сброс на «0» |

||

1 |

|

↑ |

1 |

1 |

0 |

|

Установка |

||

1 |

|

↑ |

0 |

0 |

1 |

|

Сброс |

||

1 |

|

0 |

X |

Без. изм. |

Хранение |

||||

1 |

|

↓ |

X |

||||||

|

|

|

|

|

|

||||

16 – питание; 8 – общий.

Рисунок В.9 – Шесть D-триггеров с общими входами управления и сброса

IN74AC175/IN74ACT175/IN74HC175A (1554ТМ8/1594ТМ8/1564ТМ8)

|

|

|

|

|

|

|

|

|

|

Таблица состояний |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Входы |

Выходы |

|

||||||

|

|

Q0 |

|

|

Функция |

||||||||||||||

|

|

|

|

|

R |

|

C |

D |

Q |

|

Q |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

Q1 |

|

|

|

|

0 |

|

X |

X |

0 |

|

1 |

|

Сброс на «0» |

||

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

1 |

|

↑ |

1 |

1 |

|

0 |

|

Установка |

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

Q2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

1 |

|

↑ |

0 |

0 |

|

1 |

|

Сброс |

||||

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

1 |

|

0 |

X |

Без изм. |

Хранение |

||||

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

Q3 |

|

|

|||||||||||||||

|

|

|

|

|

1 |

|

↓ |

X |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

16 – питание; 8 – общий.

Рисунок В.10 – Четыре D-триггера с общими входами управления и сброса

99

10