- •Принцип двоичного кодирования

- •0 D 0 0 1 0 0 0 инверт

- •1) Проверить, выровнены ли порядки, и. Если нет. То выровнять.

- •2} Сложить мантиссы (одна из них. Возможно, денормализовша).

- •С 1992 г. - неотъемлемая часть Intel и amd.

- •271 Команда - групповые арифметические и логические операции , сдвиги , сравнения , перегруппировка и извлечение отдельных чисел , различные варианты пересылок .

- •Команды управления виртуальной памятью .

- •6} В режиме ss&2

- •3 Register ImmediateFormat 1a

- •Instruction -Level Pa га I lei ism

- •Instruction -Level Parallel ism

- •Su perscalarArch itectu res

- •Intel 486 - один конвейер , Pentium - 2 конвейера из 5 стадий .

- •Su perscalarArch itectu res

- •Su perscalarArch itectu res

- •Instruction

- •1011X j|I 2 - все параллельно

- •1 Упрощается архитектура процессора ; вместо распараллеливающей логики на eric процессоре можно разместить больше регистров , функциональных устройств .

- •BusWidth

- •1. Арбитраж пин

- •3. Методы повышения эффективности пин

- •4. Стандарты шинS Примеры

- •Bus Arbitration (2)

- •Способы расширения полосы пропускания шин :

- •Pci BusTransactions

- •Сокращённые обозначения -kj,Mi7 Gi.Ti.Pi и Ei.

- •Vax/1980 pPra/1996

- •MemoryChips

- •Volatile

- •1. Блочная организация основной памяти

- •2. Микросхемы памяти

- •Расслоение памяти

- •Расслоение памяти

- •1. Динамические сву

- •Динамические сву для видеоадаптеров

- •Многопортовые os/

- •Volatile

- •2. (Пни -память

- •3. Ассоциативные 3/

- •4. Организация fau -памяти

- •Пример 2

- •Пример 2

- •1. Организация fcu -памяти

- •2. Система ввода -вывода

- •Ёмкость каи - 32kb , строки го 25б байт .

- •Address

- •64 Kb cache, direct -mapped,32 -byte cache block

- •32 Kb cache, 2 -wayset -associative, 16 -byteblocks

- •16Kb,4 -wayset-associativecache732 -bitaddress, byte -addressablememory/32 -byte cache blocks/lines

- •Write -through - прежде всего обновляется слово ,

- •Средства обнаружения и защиты от ошибок . Архитектура современных н)¥щ основана на полностью ассоциативном отображении .

- •Структура гу

- •1. Понятие конвейера

- •If: Instruction fetch

- •Id: Instruction decode/ register file read

- •Риск го данным - взаимосвязь команд го данным

- •Pipelined Datapath

- •Hazards

- •Superscalar Architectures

- •Instruction

- •Instruction decode

- •1. Очередность вьщачи декодированных команд на исполнительные блоки отличается от последовательности предписанной программой -неупорядоченная выдача команд (out-of-orderissue ),

- •Sisd,misd,simd,mimd.

- •Классификация Флинна

- •Heterogeneous multiprocessor chip with six cores

- •Организация памяти вс

- •Message-passing interconnection network

- •3 Stages

- •3 Stages

- •Num am ulti processors

- •Interconnection network

- •18Bits 8

- •18Bits 8

- •And memories are not shown.

- •(A) a star, (b) a complete interconnect.

- •(C) a tree, (d) a ring, (e) a grid, (f) a double torus.

- •(G) a cube, (h) a 4d hypercube.

- •Red Storm (2)

Vax/1980 pPra/1996

2010+

CSE431 LIE Htm or;1 Hierarchy.4

ruin, psu.jnus

Память отстаёт го быстродействию от ф

Слайд 10

Printed

with FinePrint- purchase atwww.fineprint.com

Иерархия запоминающих устройств

Чем

меньше время доступа , тем выше стоимость

хранения

бита .

Чем больше ёмкость , тем ниже стоимость хранения , го больше время доступа .

Г(эи создании системы памяти постоянно приходится решать задачу обеспечения требуемой емкости и высокого быстродействия за приемлемую цену .

Наиболее эффективным решением является создание иерархической памяти .

Уровни иерархии тесно связаны - все данные на одном уровне продублированы так же на более низком уровне , все данные с более низкого уровня - на следующем нижележащем уровне .

Слайд 11

Иерархия

запоминающих устройств

Емкость

доступа стоимость

Взаимодействие

Сотни

байтовW10hC

^

? Регистры

Ко

манды.операнды (1-8

байт)

I

Кэш-память

(L1)

!

Блюии

-, ,

г{8-125

байт)

15-30

нс Кэш-памвть

(L2)

I 'LБлоки

1Г(8-12Эбайг)

Аппаратура

Основная

память

Страницы

; (058Кбй

1-8

Мбайт

■

10

мкс Дис

ка вая кэш- п а мя ть

Страницы

; (0,5-6

Кбайт у,

I

,

RAID

I

срайлы

(мегабайты)

Оптические

днс^и

Файлы

(мегабайты)

Я)

I

о

секунды-минуты ЗУ

на магнитных лентах

о

I

6

Б4-129 Кбайт

10-15 не

7

4

S00-1000 Мбайт 20-40 икс

_i__

20-4000 М&айт в-10 мс

0J-B Гбайт

Н еогр а н ичен на я

Компилятор, программа

Аппаратура

Аппаратура I

Аппаратура

О

п а ра ци онная

система

Пользователь/ оператор

Слайд 12

Printed

with FinePrint- purchase atwww.fineprint.com

MemoryHierarchies

|

|

/Registers\ |

| |

|

/ |

/ Cache |

\ | |

|

/ |

Main memory |

| |

|

/ |

Magnetic disk |

\ | |

|

/ Tape |

|

|

Optical disk \ |

Afive -level memory hierarchy.

Чем ниже го пирамиде : меньше «стоимость /бит », больше ёмкость , больше время доступа , меньше частота обращения Ц1 к памяти .

Слайд В

Иерархия

запоминающих устройств

Принцип

локальности го обращению .

Адрес очередной

команды - либо следует либо расположен

рядом

с текущей (локальность го адресу).

Данные как правило

так же структурируются (лок-пь го

данным ).

Кроме того , программы содержат множество небольших циклов и подпрограмм . Это означает, что небольшие наборы команд могут многократно повторяться в течение некоторого интервала времени , есть имеет место временная локальность . Вое три вида локальности объединяет понятие локальность го обращению . Принцип локальности часто облекают в численную форму и представляют в виде так называемого правила "90/10":90% времени работы программы связано с доступом к ГР/о адресного пространства этой программы .

то

Printed with FinePrint- purchase atwww.fineprint.com

Слайд П

Иерархия запоминающих устройств

Из

свойства локальности -> программу

разумно представить

в виде последовательно обрабатываемых

фрагментов

. Помещая такие фрагменты в более

быструю память

, можно существенно снизить общие

задержки на обращение

, поскольку команды и данные , будучи

один раз

переданы из медленного 3/

в

быстрое , затем могут использоваться

многократно и среднее время доступа

к нич

в этом случае определяется уже более

быстрым 3/.

Между каждыми двумя уровнями иерархии блоками данных своего размера -для пересылки .

Г(эи доступе к данным - сперва поиск на более высоком уровне : попадание (hit) или промах (miss). Г(эи очередном промахе - ещё на уровень ниже . Г^и нахождении - блок информации пересылается наверх (пересылка только между 2-мч соседними уровнями !)

Слюй 15

Иерархия

запоминающих устройств

Г(эи

оценке эффективности подобной

организации памяти обычно используют

следующие характеристики :

•коэффициент попаданий (nitrate ) - отношение числа обращений к памяти , при которых произошло попадание , к общему числу обращений к 3/ данного уровня ;

•коэффициент промахов (missrate ) - отношение числа обращений к памяти , при которых имел место промах , к общему числу обращений к 3/ данного уровня ;

•время обращения при попадании (hittime ) - время , необходимое для поиска нужной информации в памяти верхнего уровня , плюс время на фактическое считывание данных ;

Слайд 16

•потери на промах (misspenalty ) - время , требуемое для замены блока в памяти более высокого уровня на блок с нужными данными , расположенный в 3/ следующего (более низкого ) уровня .

Printed

with FinePrint- purchase atwww.fineprint.com

Иерархия запоминающих устройств

Описание

некоторого уровня иерархии 3/

предполагает

конкретизацию четырех моментов :

•размещения блока - допустимого места расположения блока на примыкающем сверху уровне иерархии ;

•идентификации блока - способа нахождения блока ;

•замещения блока - выбора блока , заменяемого при промахе с целью освобождения места для нового блока ;

•согласования копий (когерентность данных) -обеспечения согласованности копий одних и тех же блоков , расположенных на разных уровнях .

В некоторых ЕМ фирмы БЧ есть расширенная память (expandedstorage ) - меньшее быстродействие и стоимость го отношению к основной . В иерархию не входит - к ней запрещено обращение от внешних устр -в.

Слайд 17

Primary Memory

Memory Addresses (1)

Address

Address 1 Cell

Address

о I

1 I

l

з

41

TT1

51

I

I

I

el

I i

7

12

bits

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

1l |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

2| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

3| |

|

|

|

|

I |

| |

|

|

|

|

|

|

|

| |

|

4| |

|

|

|

|

I |

| |

|

|

|

|

|

|

|

| |

|

5| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

6| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

7| |

|

|

|

|

I |

| |

|

|

|

|

|

|

|

| |

|

8| |

|

|

|

|

I |

| |

|

|

|

|

|

|

|

| |

|

9| |

|

|

|

|

I |

| |

|

|

|

|

|

|

|

| |

|

10 | |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

11| |

|

|

|

|

I |

| |

8 bits (a)

1

a

i II

4

I

I

16 bits

Three ways of organizing a 96 -bitmemory.

Каждая ячейка содержит фиксированное число запоминающих элементов .

Слайд 18

Printed

with FinePrint- purchase atwww.fineprint.com

PrimaryMemory

Memory Addresses (2)

Number

of bits per cell for some historically interesting

commercial computers

|

Computer |

Bits/cell |

|

Burroughs B1700 |

1 |

|

IBM PC |

8 |

|

DEC PDP-8 |

12 |

|

IBM 1130 |

16 |

|

DECPDP-15 |

18 |

|

XDS940 |

24 |

|

Electrologica X8 |

27 |

|

XDS Sigma 9 |

32 |

|

Honeywell 6180 |

36 |

|

CDC 3600 |

48 |

|

CDC Cyber |

60 |

Слайд 19

Основная память

Основная

память (СП) -> единственный вид памяти

, к которой

Ц1 может обращаться непосредственно

. Основная

память - 3/

с

произвольным доступом .

Основная память может включать в себя два типа устройств :

-оперативные запоминающие устройства (СВУ) и -постоянные запоминающие устройства (ПЗУ).

СВУ - RAM( Random Access Memory ). Для большинства типов полупроводниковых СВУ характерна энергозависимость : даже при кратковременном прерывании питания хранимая информация теряется . Микросхема СВУ должна быть постоянно подключена к источнику питания и поэтому может использоваться только как временная память .

Слайд Т)

Printed with FinePrint- purchase atwww.fineprint.com

Основная память

Вторую

группу полупроводниковых 3/

основной

памяти

образуют

энергонезависимые микросхемы ПЗУ (ROM - Read -Only Me mory). ПЗУ обеспечивает считывание информации , го не допускает ее изменения (в ряде случаев информация в ПЗУ может быть изменена , го этот процесс сильно отличается от считывания и требует значительно большего времени ).

Энергозависимые СБУ можно подразделить на две основные подгруппы :

динамическую память (DRAM - DynamicR and omAccess

Me mory ) и статическую память (5RAM - StaticR and от Access Me mory).

Слайд Ъ.

Основная память

В

статических СВУ запоминающий элемент

может хранить

записанную информацию неофаниченно

долго (при

наличии питающего напряжения ).

Запоминающий элемент динамического СВУ способен хранить информацию только в течение достаточно короткого промежутка времени , после которого информацию нужно восстанавливать заново , иначе она будет потеряна . Динамические 3/, как и статические , энергозависимы .

Роль запоминающего элемента в статическом СВУ исполняет триггер (схема с двумя устойчивыми состояниями , обычно состоящую из четырех или шести транзисторов ).

Слайд 22

Printed with FinePrint- purchase atwww.fineprint.com

Статическое и динамическое СВ/

![]()

Выбор ячейки

Выход

Выбор ячейки

пит

Выход Уст. е О

Вход

SR/W , на б

транзисторах - быстрее , менее чувствительны к внешним излучениям

Простота схемы HW\ позволяет достичь высокой плотности размещения , в итоге , снизить стоимость . Главный недостаток - что накапливаемый на конденсаторе заряд <о временем теряется . Среднее время утечки заряда DR/W1 составляет согни (десятки ) миллисекунд , поэтому , заряд следует регенерировать .

Слюй 23

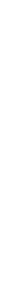

Latches - Защёлки

Q

(а)

(Ь)

Пэи R=S=0 два стабильных состояния :

Защёлка ИГИ -НЕ (NCR ) в состоянии 0.

Защёлка ИГИ -НЕ (NOR) в состоянии 1.

R=S= 1 - запрещено в следствие неопределённости при возврате к R=S=0 .

Printed

with FinePrint- purchase atwww.fineprint.com

Слайд Ъ

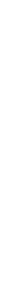

Latches - Защёлки

Clock

J|_

Q

Синхронные RS -защёлки . A clocked SR latch.

Слайд 25

Latches - Защёлки

Q

Синхронная D защёлка - A clocked D latch. (Используется 11 транзисторов ).

Printed

with FinePrint- purchase atwww.fineprint.com

Сяаид

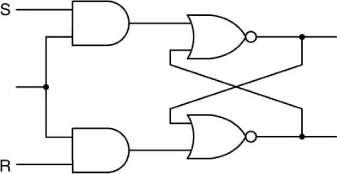

Rp -Hops - Триггеры

Защёлки

запускаются уровнем сигнала , триггеры

фронтом

!

а [\л

Ь , ^ bANDc

d

(а)

|

|

1 |

|

|

i |

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

1 |

Time

A pulse generator.

Timing at four points in the circuit.

Слайд 27

Rp -Hops

Q

ADflip -flop.

D- триггер (на практике используются более сложные схемы ).

Printed

with FinePrint- purchase atwww.fineprint.com

Сяаид

|

|

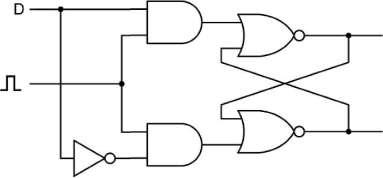

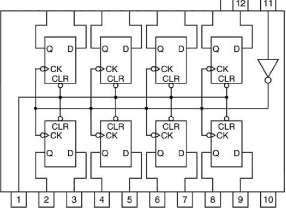

Fip -Hops | ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D Q |

|

D Q |

|

D Q |

|

D Q |

|

|

|

|

CK (a) |

—С |

CK (b) |

|

>CK (c) |

—С |

>CK (d) |

|

|

|

D latches and flip -flops. D - защёлки (a,b) и триггеры (c,d). | ||||||||

|

|

Триггер (с) меняет состояние на возрастающем фронте (с 0 на 1), a (d) - на заднем фронте (с 1 на 0). У многих схем есть #Q, Set(Preset) ->Q=1, Reset(CIear) -> Q=0 | ||||||||

|

|

|

|

|

|

|

|

|

Слшд |

29 |

Rp

-Hops

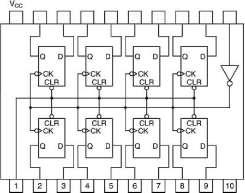

Vcc

ГйП ГТз1

|

|

1 |

|

|

|

|

|

1 |

|

|

| ||||||||||||||||||

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||

|

|

|

|

|

|

|

( |

|

|

|

| ||||||||||||||||||

|

|

|

|

|

1 |

|

|

|

| ||||||||||||||||||||

|

|

CLR D 0 >CK Q PR |

|

|

CLR D Q >CK Q PR |

| |||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||

|

|

Y |

|

|

|

1 |

|

|

| ||||||||||||||||||||

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||

|

|

П |

|

|

|

|

|

| |||||||||||||||||||||

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||

[7]

GND

(a)

независимых D-триггера i-a одной микросхеме (Dual Dflip -flop ).

Слайд ЗЭ

Printed

with FinePrint- purchase atwww.fineprint.com

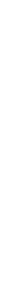

Rp -Hops

Vcc

_______

__

[iol ГТэ1 [Tel ГГт! ГГб1 ITsl ГТП ГТз

GND

Восьмиразрядный триггер (Octalflip -flop ) - в качестве восьмиразрядного регистра .

Слайд 31

WordO

Logicdiagram

fora

4x3

memory.

Each

rowisone of

the four 3

-bitwords.

(5

- chipselect

FD

-

read

CE

-

output

enable

Memory Organization

Output enable = CS - RD ■ OE

Printed

with FinePrint- purchase atwww.fineprint.com

Memory Organization (2)

![]()

Data out

Control

(a)

(b)

(d)

(a)A noninverting buffer - буферный элемент без инверсии .

Effect of (a) when control is high.

Effect of (a) when control is low.

An inverting buffer - буферный элемент синверсией .

Слайд

Memory

Organization

20

19 18 17 16 15 14 13 12 11

Output

«гаЫи

-

QS,

■

RD

■ Of

8-&TT - 2D выводов f 12 6m" - 14 выводов .

Слайд

Printed

with FinePrint- purchase atwww.fineprint.com

Блочная организация памяти

Ад, А7

Дешифратор номера банка памяти

Банк,

Банк3

О

128

256

384

Регистр

адреса

У

Блок

управления

127

255

383

511

АеА)

Мупьтиллексор/демультиплексор

Запрос

Шина адреса

Шина данных

Адресное пространство памяти разбито на группы последовательных адресов . Каждая такая группа обеспечивается отдельным банком памяти . Для обращения используется 9-разрядный адрес , семь младших разрядов которого (Аб - АО) поступают параллельно на вое банки памяти и выбирают в каждом из ник одну ячейку .

Слюд 35

Блочная

организация памяти

Ag,

Aj

Дешифратор номера банка памяти

Банк,

Банк,

О

128

255

384

Регистр

адреса

У

Блок

управления

Ag.-A^j

127

I

255

383

Мупьтиллексор/демультиплексор

511

Запрос

Шина адреса

Шина данных

Слайд 36

Два старших разряда адреса (А8, А7) содержат номер банка . Выбор банка обеспечивается либо с помощью дешифратора номера банка памяти , либо путем мультиплексирования информации рис. иллюстрирует оба варианта ) В функциональном отношении такая СП может рассматриваться как единое 3/f емкость которого равна суммарной емкости отдельных банков , а быстродействие -быстродействию отдельного банка .

Printed

with FinePrint- purchase atwww.fineprint.com