- •Тема 4 Программная модель микропроцессоров архитектуры ia-32

- •1. Особенности архитектуры ia-32

- •2. Структура микропроцессоров ia-32

- •3. Регистры

- •4. Формат команды микропроцессора ia-32

- •5. Типы данных

- •6. Пространство памяти

- •7. Режимы адресации

- •8. Система команд

- •8.1. Инструкции пересылки данных

- •8.2. Инструкции двоичной арифметики

- •8.3. Инструкции десятичной арифметики

- •8.4. Инструкции логических операций

- •8.5. Инструкции сдвигов

- •8.6. Инструкции обработки бит и байт

- •8.7. Инструкции передачи управления

- •8.8. Инструкции строковых операций

- •8.9. Инструкции работы с флагами

- •8.10. Инструкции загрузки указателей

- •8.11. Разные инструкции

6. Пространство памяти

Память для 32–разрядных процессоров 80х86 подразделяется на байты (8 бит), слова (16 бит), двойные слова (32 бита). Слова записываются в двух смежных байтах, начиная с младшего. Адресом слова является адрес его младшего байта. Двойные слова записываются в четырех смежных байтах, опять–таки начиная с младшего байта, адрес которого и является адресом двойного слова.

Более крупными единицами являются страницы и сегменты. Память может логически организовываться в виде одного или множества сегментов переменной длины (в реальном режиме – фиксированной). Сегменты могут выгружаться на диск и по мере необходимости с него подкачиваться в физическую память. В защищенном режиме возможно разбиение логической памяти на страницы размером 4 Кбайт, каждая из которых может отображаться на любую область физической памяти. Начиная с 5–го поколения, появилась возможность увеличения размера страницы до 4 Мбайт. Сегментация является средством организации логической памяти, используемым на прикладном уровне. Разбиение на страницы применяется на системном уровне для управления физической памятью.

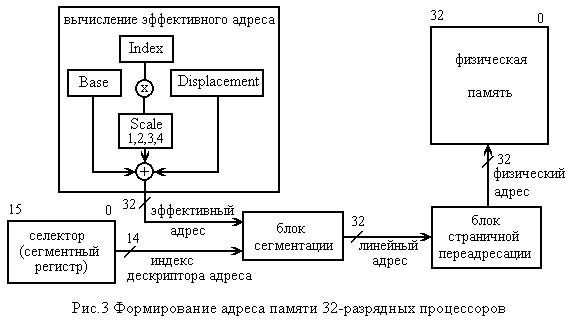

Применительно к памяти различают три адресных пространства: логическое, линейное и физическое. Основным режимом работы 32–разрядных процессоров считается защищенный режим, в котором работают все механизмы преобразования адресных пространств (см. рисунок 6.1).

Логический адрес, также называется виртуальным, состоит из селектора сегмента (в реальном режиме – просто адреса сегмента) и эффективного адреса, называемого также смещением. Эффективный адрес формируется суммированием компонентов base, index, displacement с учетом масштаба scale. Поскольку каждая задача может иметь до 16 Кбайт селекторов, а смещение, ограниченное размером сегмента, может достигать 4 Гбайт, логическое адресное пространство для каждой задачи может достигать 64 Тбайт. Все это пространство виртуальной памяти в принципе доступно программисту (при условии поддержки со стороны операционной системы).

Блок сегментации транслирует логическое пространство в 32–битное пространство линейных адресов. Линейный адрес образуется сложением базового адреса сегмента с эффективным адресом. Базовый адрес сегмента в реальном режиме образуется умножением содержимого используемого сегментного регистра на 16 (как и в 8086). В защищенном режиме базовый адрес загружается из дескриптора, хранящегося в таблице, по селектору, загруженному в используемый сегментный регистр.

Рисунок 6.1. Формирование адреса памяти

32–битный физический адрес памяти образуется после преобразования линейного адреса блоком страничной переадресации. Он выводится на внешнюю шину адреса процессора. В простейшем случае (при отключенном блоке страничной переадресации) физический адрес совпадает с линейным. Включенный блок страничной переадресации осуществляет трансляцию линейного адреса в физический страницами, размером 4 Кбайт (для старших поколений процессоров возможны страницы размером 2 или 4 Мбайт).

7. Режимы адресации

Система команд 32–разрядных процессоров предусматривает 11 режимов адресации. При этом только в двух случаях операнды не связаны с памятью. Это операнд–содержимое регистра, которое берется из любого 8-, 16- или 32-битного регистра процессора, и непосредственный операнд (8, 16 или 32 бит), который содержится в самой команде. Остальные девять режимов (см. таблица 7.1) так или иначе, обращаются к памяти.

При обращении к памяти эффективный адрес вычисляется с использованием следующих компонентов:

Смещение (Displacement) – 8-, 16- или 32-битное число, включенное в команду.

База (Base) – содержимое базового регистра. Обычно используется для указания на начало некоторого массива.

Индекс (Index) – содержимое индексного регистра. Обычно используется для выбора элемента массива.

Таблица 7.1. Режимы адресации

|

Режим |

Адрес |

|

Прямая адресация (Direct mode) |

EA = Displacement |

|

Косвенная регистровая адресация(Register Indirect Mode) |

EA = Base |

|

Базовая адресация (Based Mode) |

EA = Base + Displacement |

|

Индексная адресация (Index Mode) |

EA = Index + Displacement |

|

Масштабированная индексная адресация (Scaled Index Mode) |

EA = Scale * Index + Displacement |

|

Базово–индексная адресация (Based Index Mode) |

EA = Base + Index |

|

Масштабированная базово–индексная адресация (Based Scaled Index Mode) |

EA = Base + Scale * Index |

|

Базово–индексная адресация со смещением (Based Index Mode with Displacement) |

EA = Base + Index |

|

Масштабированная базово–индексная адресация со смещением (Based Scaled Index Mode with Displacement) |

EA = Base + Scale * Index + Displacement |

Масштаб (Scale) – множитель (1, 2, 4 или 8), указанный в коде инструкции. Этот элемент используется для указания размера элемента массива, доступен только при 32–битной адресации.

Эффективный адрес вычисляется по формуле

EA = Base + Index * Scale + Displacement

При обращении к памяти использование сегментных регистров по умолчанию определяется типом обращения (см. табл.5). Для большинства типов обращения на время текущей инструкции при необходимости возможно использование альтернативного сегментного регистра, на что указывает префикс замены сегмента (CS:, DS: и т.д.) перед кодом инструкции.