Домашнее задание

.docxМинистерство образования и науки Российской Федерации

Федеральное бюджетное государственное образовательное учреждение высшего профессионального образования

«Омский государственный технический университет»

Кафедра «Автоматизация и робототехника»

ДОМАШНЕЕ ЗАДАНИЕ

по дисциплине «Схемотехника систем управления»

Тема: «Дешифратор адреса»

Вариант 5.3

Проверил: доцент, к.т.н.

___________ А. Н. Компанейц

“___”__________2012 г.

Разработал: ст. гр. БМТ-419

____________ Д. В. Дьяконов

“___”__________2012 г.

Омск 2012

Дешифратор адреса

Задание:

Разработать дешифратор адреса (ДА) 5×4 с задатчиком адреса на микросхеме цифрового компаратора и DC, а также рассчитать необходимые задержки.

Решение:

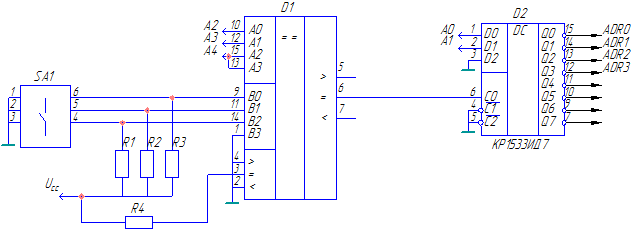

ДА 5х4, изображенный на рис. 1, выполнен на микросхеме цифрового компаратора (КР1533СП1) и дешифратора - демультиплексора 3 на 8 (КР1533ИД7).

В данной схеме код адреса, выдаваемый процессором, поступает на входы А3-А0 компаратора, а с задатчика адреса на В3-В0. При совпадении кодов на выходе «=» формируется «1». Сигналы с выходов компаратора поступают на входы разрешения дешифратора С0-С2. Дешифратор основываясь на сигнале поступившем на вход С0 и кодов адреса, выдаваемых процессором, поступивших на входы D0-D1, формирует на выходе необходимые сигналы. Задатчик адреса выполнен на 3-разрядной сборке микропереключателей SA1. Разомкнутое состояние контактов обеспечивает подачу на входы микросхемы логической «1». При замыкании микропереключателей на соответствующих входах устанавливается логический «0».

Задержки дешифратора адреса на микросхеме компаратора при установке и снятии адреса определяются выражениями:

Рис.1. Принципиальная электрическая схема дешифратора адреса