- •1. Принципы и базовые алгоритмы обработки сигналов в цифровых системах. Требования к аппаратной базе для выполнения базовых операций цос.

- •3. Форматы представления данных в сигнальных процессорах. Сравнительные особенности процессоров, ориентированных на обработку фз- и пз-данных. Оценка необходимой разрядности процессора.

- •1. Данные с фиксированной запятой (Fixed-Point Numbers)

- •2. Данные с плавающей запятой (Floating-Point Numbers)

- •4. Этапы и средства разработки и отладки по для процессоров цос. Критерии выбора языка программирования и средств разработки по

- •6. Особенности программной организации ввода-обработки-вывода данных в системах цос, работающих в реальном времени. Работа по прерываниям. Использование буферов.

- •7. Методики оптимизации кода для risc-процессоров

- •Inline- функции

- •8. Dsp семейства adsp-2106x. Основные характеристики и особенности архитектуры.

- •9. Карта памяти adsp-2106x. Пространства внутренней памяти, памяти многопроцессорной системы и внешней памяти. Пространство памяти iop-регистров.

- •10. Физическая организация внутренней памяти. Блоки памяти. Возможные виды конфликтов при обращении к внутренней памяти и способы их устранения. Адресация нормальных и коротких слов.

- •12. Доступ к памяти в программе. Организация dag. Основные возможности. Особенности программирования регистров dag. Кольцевые буферы.

- •13. Системные регистры: назначение и работа с ними. Устройство обмена между шинами (px-регистры).

- •14. Общие принципы работы вычислительных блоков adsp-21ххх. Особенности организации вычислений с пз- и фз-данными. Регистровый файл. Поддерживаемые типы данных и их идентификация в программе.

- •15. Теневые регистры. Регистры флагов. Понятие "липких" флагов. Флаги аккумулирующих сравнений.

- •16. Описание и функции алу. Флаги состояния и режимы работы алу. Мас. Функционирование мас. Особенности выполнения операций округления и насыщения при работе с фз-операндами. Флаги состояния мас.

- •17. Сдвигатель. Функционирование сдвигателя. Выделение и депонирование битовых полей. Флаги состояния сдвигателя. Организация многофункциональных вычислений. Ограничения.

- •19. Организация циклов. Ограничения при организации циклов. Циклы не по счетчику. Достоинства и недостатки аппаратной поддержки циклов.

- •20. Кэш инструкций. Структура и функционирование. Возможности управления обновлением кэша. Примеры повышения/понижения эффективности выполнения кода с учетом работы кэша.

- •21. Обработка прерываний: общая последовательность действий. Таблица прерываний. Маскирование прерываний. Регистры, программного секвенсора, используемые при обработке прерываний.

- •22. Отличия работы процессора при разрешенных и запрещенных вложенных прерываниях.

- •23. Организация работы с таймером. Программные прерывания. Внешние прерывания.

- •24. Понятие и назначение dma-пересылок в adsp-2106x. Направления пересылок. Каналы dma. Принципы функционирования dma-контроллера adsp-2106x. Генерация прерываний dma-контроллером.

- •26. Цепочечные dma-пересылки в adsp-2106x. Tcb-блоки. Инициирование и завершение цепочечных dma-пересылок. Контроль состояния цепочечной dma-пересылки

- •27. Порты sharc-процессоров. Реализуемые виды интерфейсов. Организация взаимодействия между процессорным ядром и портами при вводе/выводе данных.

- •29. Архитектура и принципы функционирования линк-портов (звеньевых портов) adsp-2106x. Регистры управления работой линк-портов adsp-2106x. Связь между линк-буферами и линк-портами.

- •30. Организация взаимодействия между процессорами по выделенным каналом через линк-порты. Регистр lsrq и его назначение. Идея алгоритма "передачи маркера".

- •31. Механизм арбитража внешней шины. Схемы приоритетов. Приоритетный доступ процессорного ядра.

- •32. Операции вещательной записи. Блокировка шины. Использование "зеркальных" семафоров. Межпроцессорные сообщения и вектор прерывания virpt.

- •33. Отличительные особенности компилятора cc21k. Поддерживаемые типы данных и их реализация.

- •2.1. Общие сведения

- •2.2. Поддерживаемые типы данных

- •34. Расширения языка с. Ассемблерные вставки – использование регистров. Поддержка пространств памяти данных памяти команд. Доступ к круговым буферам.

- •2.3.1. Поддержка inline-функций

- •2.3.2. Ассемблерные вставки

- •2.3.3. Поддержка пространств памяти данных и памяти команд

- •2.3.4. Доступ к круговым буферам

- •2.4.1. Использование памяти

- •2.4.2. Регистры компилятора

- •36. Работа со стеком при вызове процедур в рамках rte. Передача и возврат параметров. Взаимодействие программ на с и ассемблере

- •2.4.4. Передача параметров в функции и возврат значений

- •2.5. Взаимодействие подпрограмм на с и ассемблере

- •2.5.1. Описания имен и области их видимости

- •2.5.2. Макросы для работы со стеком при вызове и возврате из функций на ассемблере

- •2.5.3. Вызов подпрограммы на ассемблере из программы на с

- •2.5.4. Вызов подпрограммы на с из подпрограммы на ассемблере

- •37. Разработка обработчиков прерываний. Диспетчер прерываний. Классификация обработчиков прерываний по "быстродействию" и накладным расходам.

1. Принципы и базовые алгоритмы обработки сигналов в цифровых системах. Требования к аппаратной базе для выполнения базовых операций цос.

Цифровая обработка сигналов (ЦОС) – это арифметическая обработка в реальном времени последовательности значений амплитуды сигнала, определяемых через равные временные промежутки.

Принципы цифровой обработки сигналов:

Цифровое представление сигналов с необходимой точностью.

Выполнение в реальном, или близком к реальному, масштабе времени большого количества вычислительных операций надо потоками данных (массивами), в том числе и бесконечными во времени.

Основными алгоритмами ЦОС являются:

БИХ- и КИХ-фильтрация сигнала;

корреляционная функция двух сигналов или автокорреляционная функция сигнала;

прямое/обратное преобразование Фурье;

помехоустойчивое (канальное) кодирование;

формирование пакетов для передачи по каналам связи;

векторное квантование;

модуляция и демодуляция узкополосных сигналов.

Фильтрация сигналов

В области ЦОС выделяют фильтры следующих видов:

с конечной импульсной характеристикой (КИХ);

с бесконечной импульсной характеристикой (БИХ).

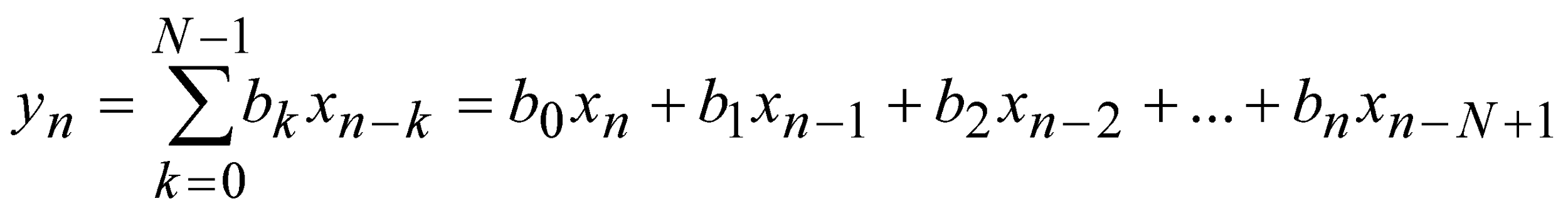

В КИХ-фильтре отсчет выходного сигнала определяется только значениями входного сигнала и задается уравнением вида:

где xn и yn – соответственно отсчеты входного и выходного сигналов, N – порядок фильтра (количество коэффициентов), bk – коэффициенты фильтра.

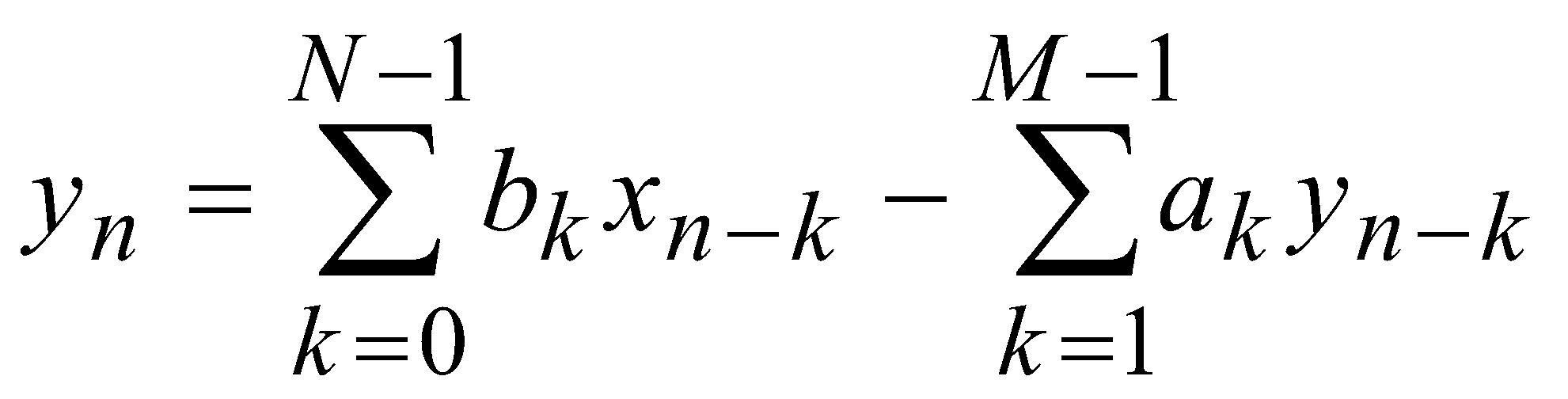

В БИХ-фильтре отсчет выходного сигнала определяется значениями входного сигнала и предыдущими значениями выходного сигнала:

Для эффективной реализации необходимы:

выполнение операций «умножения с накоплением»;

одновременная выборка из памяти двух операндов;

доступ к памяти с автоматической модификацией указателя;

циклическая организация буфера (кольцевые буферы);

аппаратная поддержка циклов.

Фурье-преобразование сигнала

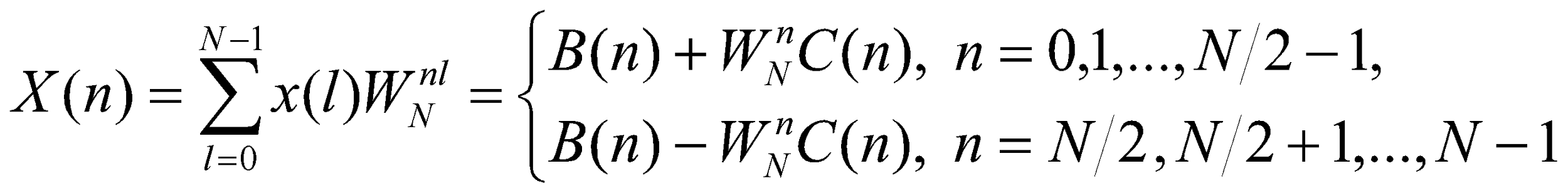

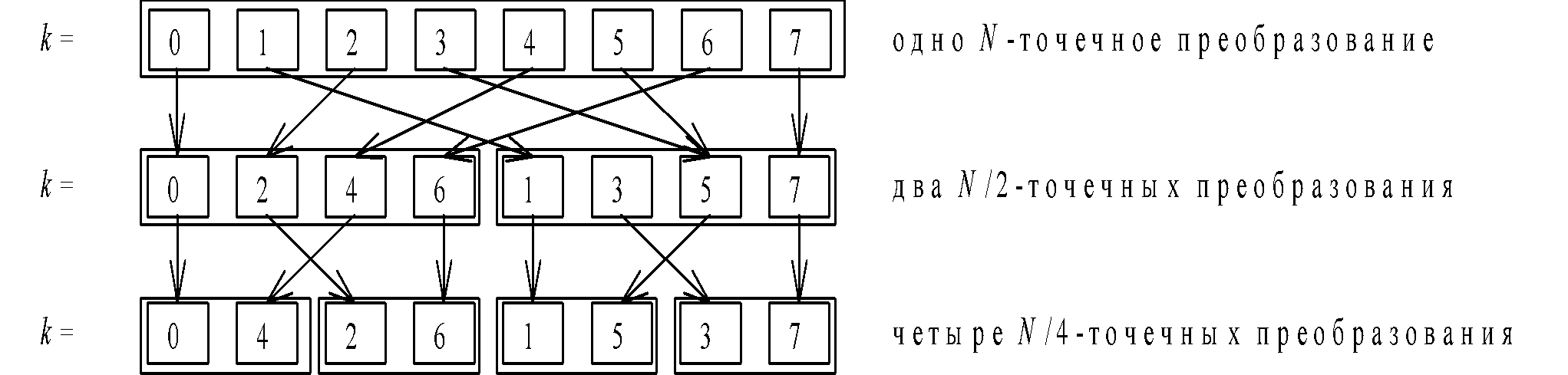

В системах цифровой обработки сигналов чаще используется быстрое преобразование Фурье. Его реализация приводит к существенному уменьшению вычислительной сложности. Основная идея быстрого преобразования Фурье состоит в том, чтобы разбить исходный N-отсчетный сигнал x(n) на два более коротких сигнала, преобразования которых далее комбинируются таким образом, чтобы получить преобразование исходного N-отсчетного сигнала.

Вычисление N-точечного (отсчетного) преобразования можно произвести путем вычисления двух N/2-точечных. Для указанных условий Фурье-преобразование имеет следующий вид:

![]() ;

;

![]() ;

;

![]()

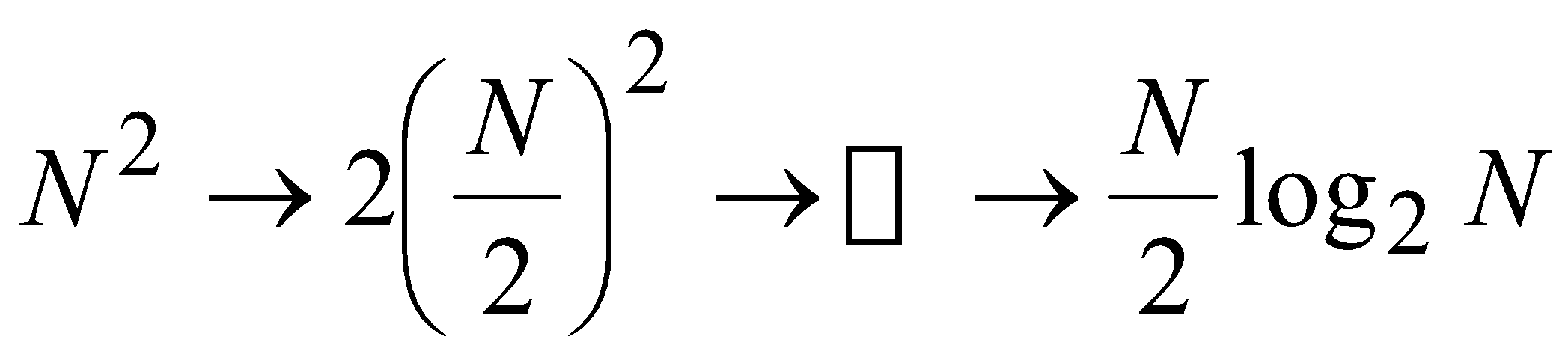

Аналогично, два N/2-точечных преобразования можно свести к четырем N/4-точечным и так далее. При этом сокращение объема вычислений составит:

.

.

Для эффективной реализации необходимы:

бит-реверсная адресация;

дуальное сложение/вычитание;

умножение с накоплением;

аппаратная поддержка циклов;

табличная реализация функций sin, cos.

Пример: порядок адресации элементов при выполнении, например, четырех 2-х точечных преобразования (при N=8) будет такой:

Представим адреса элементов в двоичном коде и переставим биты в обратном (реверсном) порядке:

-

Прямой:

000

001

010

011

100

101

110

111

Реверсный:

000

100

010

110

001

101

011

111

Значение:

0

4

2

6

1

5

3

7

Формирование пакетов данных

Формирование тела пакета, а также его заголовка и хвостовика в соответствии с требованиями конкретного приложения и протоколом обмена данными. Реализация депонирования битовых полей – при формировании пакета, когда требуемое значение помещается в формируемое слово в нужную позицию и занимает правильное количество битов без использования дополнительных операций сдвигов. Выделение битовых полей – при распознавании пакета, обратная операция.

Требования к аппаратной базе для выполнения базовых операций ЦОС:

выполнение операций «умножения с накоплением»;

одновременная выборка из памяти двух операндов;

доступ к памяти с автоматической модификацией указателя;

циклическая организация буфера (кольцевые буферы);

аппаратная поддержка циклов (автоматическая проверка условия выхода из цикла без потери тактов);

дуальное сложение/вычитание;

бит-реверсная адресация;

повышенная точность представления операндов;

табличная реализация элементарных функций;

эффективный доступ к битовым полям.

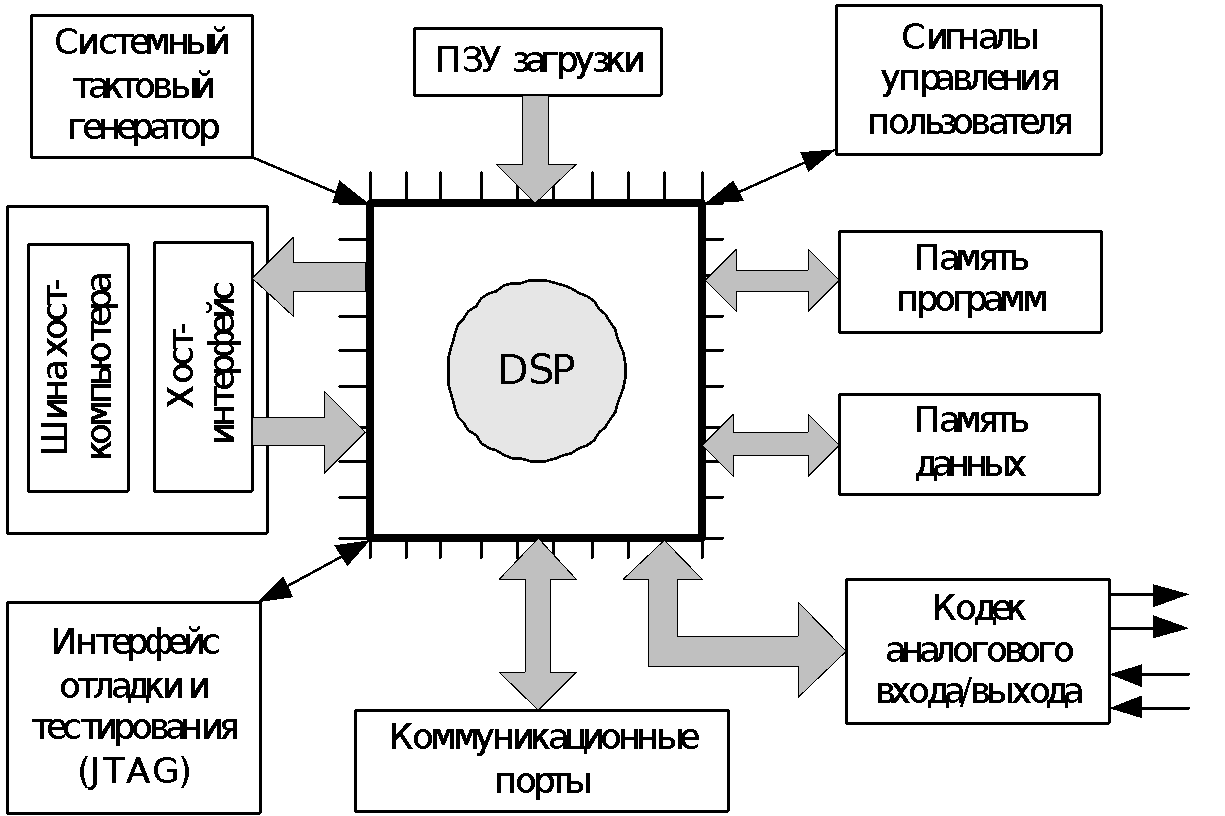

2. Обобщенная архитектура сигнальных процессоров: фундаментальные особенности. Способы взаимодействия DSP-процессора с внешними устройствами различных типов. Методы оценки производительности процессоров.

Цифровой сигнальный процессор представляет собой специализированный процессор с RISC-архитектурой (архитектура процессора, в котором быстродействие увеличивается за счёт упрощения инструкций, сокращён объём (и время) работы, выполняемый каждой инструкцией), предназначенный для решения задач цифровой обработки сигналов.

Принципиальные особенности архитектуры сигнальных процессоров:

принцип «детерминированного выполнения» - можно заранее сказать, как долго тот или иной фрагмент кода будет выполняться на сигнальном процессоре;

Гарвардская архитектура – предполагает наличие двух раздельных пространств для хранения данных и инструкций и отдельных шин для каждого из них. Шины функционируют независимо, инструкция и данные могут быть извлечены одновременно. Следующий уровень - Супер-Гарвардская архитектура (SHARC – Super Harvard ARChitecture, термин введен фирмой Analog Devices), отличающаяся наличием кэша команд и контроллера ввода/вывода:

Контроллер ввода/вывода. Чтобы обеспечить ввод/вывод данных из процессора с высокой скоростью, не снижая вычислительных возможностей процессора, контроллер ввода/вывода посредством механизма прямого доступ к памяти (Direct Memory Access, DMA) позволяет записывать и считывать данные напрямую из внутренней памяти процессора.

элементы RISC-архитектуры. Конвейеризация и сокращение длительности командного цикла – обычно применяется двух- или трехкаскадный конвейер – выполняются одновременно две или три инструкции, размещение операндов в регистрах, использование теневых регистров, аппаратная поддержка циклов;

аппаратная реализация типовых операций ЦОС – аппаратный умножитель для сокращения времени операции умножения;

специализированные команды ЦОС – оптимизированы для выполнения базовых задач цифровой обработки сигналов;

расширенные коммуникационные возможности – наличие встроенных АЦП и ЦАП.

Взаимодействие с внешними устройствами

Обычно система ЦОС представляет собой комплексную аппаратную схему, включающую кроме DSP ряд внешних устройств. В нормальном режиме DSP работает синхронно с АЦП или КОДЕКОМ, принимая или выдавая данные с постоянным временным интервалом синхронно с сигналами тактового генератора, расположенного на плате.

В то же время DSP может обмениваться данными с хост-процессором или от схемы управления пользователем. Эти события происходят асинхронно, т.е. в произвольные моменты времени. Для обработки таких событий могут использоваться две схемы:

ввод/вывод данных с последовательным опросом (POLLED I/O), когда процессор просто "регулярно" проверяет состояния на определенных ножках и принимает решение в зависимости от уровня сигнала. Хотя эта схема проста, она приводит к снижению производительности, т.к. часть опросов выполняется "вхолостую";

управление с использованием прерываний. Как обычно, такая схема требует выделения таблицы векторов прерываний для обработки каждого внешнего сигнала и написания программно обработчика прерывания.

механизмы прямого доступа к памяти, которые позволяют организовать обмен большими объемами (блоками) данных между коммуникационными портами процессора и внутренней памятью без использования ресурсов процессорного ядра параллельно с ходом выполнения основной программы.

Также поддерживается отладка в реальном времени.

Методы оценки производительности

Производительность процессоров может оцениваться по нескольким критериям:

- MIPS – количество инструкций, выполняемых в секунду;

- MFLOPS, MOPS – оценки количества операций в секунду, которое может выполнить процессор, также без учета конкретного алгоритма.

- MMACS – количество операций умножения с накоплением в секунду.

Более комплексные метрики учитывают также стоимость, объем памяти и энергопотребление. Соответственно каждый процессор может представляться в виде параллелепипеда в системе координат с осями, соответствующими единицам энергопотребления (mA), производительности (MIPS), требуемого размера памяти (Кб).

Более реалистичные оценки производительности получают путем прогона на DSP определенных задач - типовых алгоритмов ЦОС, например, векторное произведение, сложение векторов, фильтры. Такая оценка позволяет оценить производительность всей системы.

Также используются оценки на наборах тестов (BDTImark2000 и др.) и оценки на типовых приложениях (Full Application Benchmark).